基于TSV的3D堆叠集成电路测试

韩博宇, 王 伟, 刘 坤, 陈 田, 李润丰, 郑浏旸

(1.合肥工业大学 计算机与信息学院,安徽 合肥 230009;2.情感计算与先进智能机器安徽省重点实验室,安徽 合肥 230009)

0 引言

尽管TSVs互连的三维芯片堆叠仍有许多技术挑战,但其仍被视为是一种关键技术,以帮助半导体行业遵循摩尔定律到下一个10年。3DICs利用快速、密集的片内通孔,克服了互连扩展的障碍[1-2]。

此外,3DICs技术还使得芯片外形尺寸更加紧凑,从而实现真正意义上的SoC。但为满足该技术的高精度要求,需要对每一片IC进行电气测试,以剔除有缺陷的部件,保证提供给用户的产品质量。然而,3D技术的采用,受到了对3D测试问题认识不足和缺乏DFT技术的阻碍,其解决方案仍然未得到很好的研发,致使预期收益与使用价值之间存在较大的差距[3]。因此在所有挑战中,3DICs测试的工具和方法被视为头号挑战就不足为奇了。此外,三维芯片堆叠还存在一些特有的测试挑战[4]。

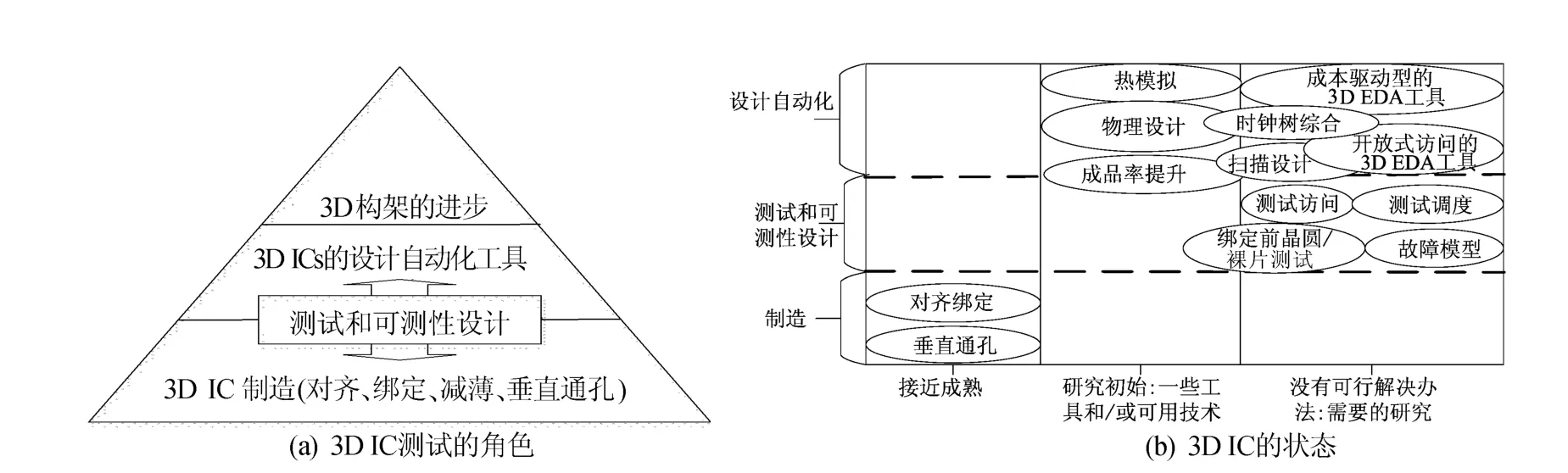

本文介绍了3DICs的测试挑战,并概述了3D芯片测试策略早期和目前进行的工作。图1显示了3D集成,其定位在正在进行的研究活动的背景下,图1a三角的底部显示了3DICs行业主要的特有制造方面[5-6],被视为探讨3D设计自动化和构架研究的基础。

虽然3DICs制造技术已近乎成熟,但某些设计方法挑战和大部分测试问题仍基本处于未开发状态,如图1b所示。

图1 3DIC测试和相关的3D集成背景下的挑战

1 3D堆叠芯片新的测试流程

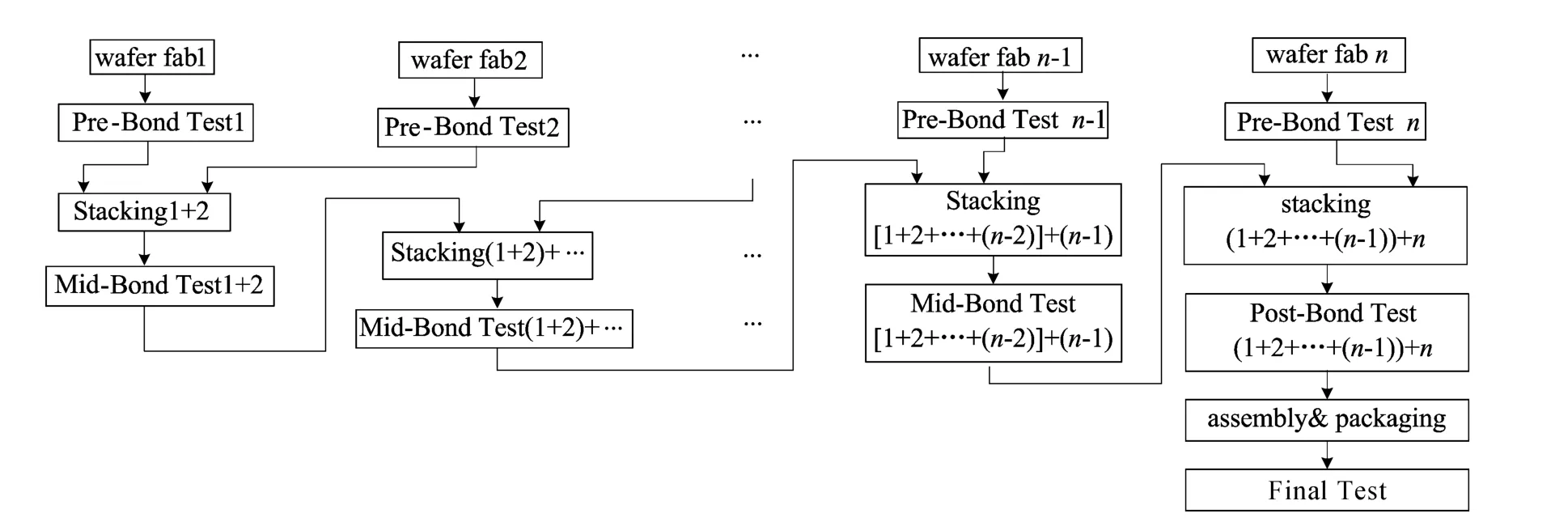

传统的单裸芯片的测试流程包括2个测试时刻,即晶圆测试和最终封装测试。3DSICs的测试流程则复杂得多,其制造过程由许多步骤组成,并因此具有许多潜在的自然测试时刻。图2显示了一个多裸片堆叠的测试时刻[7]。堆叠前的测试称为绑定前测试,如图2中的Pre-Bond Test 1,Pre-Bond Test 2,…,Pre-Bond Testn,它们可以在晶圆减薄之前或之后进行。堆叠后,可以进行测试,无论是称为绑定中测试的部分堆叠,如图2中的 Mid-Bond Test 1+2,Mid-Bond Test(1+2)+…,…,Mid-Bond Test(1+2+…+(n-2))+(n-1));还是称为绑定后测试的完整堆叠,如图2中的Post-Bond Test(1+2+…+(n-1))+n)。所有这些测试,外部测试访问都是通过探测来实现的,通常是在晶圆级。一旦堆栈被封装,一个最终封装测试就可以进行。用于最终测试的外部晶圆探测,如图2中的Final Test,是通过一个封装引脚、一个测试套接字执行的。

图2 一个多裸片堆叠可能的测试时刻

测试时,在满足市场合理的成本下,应该保证产品质量,因此没有单一尺寸适合所有的测试流程。早期的测试都会产生由于下游减薄、堆叠和封装等操作可能导致的缺陷,因此需要重新测试。制造成本和成品率以复杂的方式与测试流程交织在一起,因此需要对测试成本进行建模,以确定给定产品的最佳测试流程。

测试流程在时间上不是一成不变的,因此模块化的测试方法[8]得到青睐,其各种组件和互连可以作为独立的单元(相对于一个单片测试,这种裸片堆栈是作为一个单一的单片实体被测试)被测试。模块化的测试方法允许包含、排除和重新安排各种模块测试[8-9]。模块化测试方法的另一个好处是能降低整体测试数据量。

2 TSVs绑定前测试

在传统IC制造中,封装之前晶圆被探测和单独裸片测试称为晶圆排序。在3D集成中,如果可以在测试前绑定裸片,或者能先晶圆排序并堆叠相匹配的裸片在彼此的顶部,则3DICs的成品率可以增加。然而,3D集成晶圆的绑定前测试面临着一些严峻的挑战[10]。

2.1 良好的裸片(KGD)

在一个非集成的生产流程中,整体制造产业链被多家公司控制。对于3D-SICs,一个非集成的生产流程更可能是传统的(2D)ICs堆叠。在一个非集成的生产流程中,一家公司建造模块的中间产品,有可能是另一家公司的最终产品。在这样的环境中,通常需要中间产品通过最终质量测试,包括速度和老化测试。这些中间产物被称为已知良好的裸片(KGD)[11],或者在裸片堆叠的情况下,为已知良好的堆叠(KGS)。

2.2 KGD晶圆级测试和老化

为了使3DICs技术在商业上可行,绑定前测试技术是一项迫切的需求。老化测试是一种在半导体工业中被广泛使用的技术。老化测试中的晶圆级测试(WLTBI)是一项有利于降低老化测试成本的技术,其允许在较低的裸片堆叠成本下获得KGDs或KGS,因此尤其适用于3D集成。该方法在裸晶圆形成时设备进行老化测试和电气测试。这些整体晶圆并行测试系统,可以在提供传统老化测试时测试数以千计的芯片。

在内建自测试中,通常使用老化测试方法。芯片设计者采用片上DFT基础设施,以实现WLTBI。监控老化测试是一种在被测试设备(DUT)上设置有输入测试模式的方法,在线监控输出对DUT的响应,从而导致故障设备被识别。因此,WLTBI有很大的潜力,通过消除老化测试和测试过程之间的障碍来降低测试成本。同时,WLTBI也会减轻一些晶圆堆叠的绑定前测试问题[12-13]。

2.3 DFT技术

设计者必须在绑定前确保每个单独裸片层被设计为可测试的。对于这样的3DICs设计,启用绑定前测试将需要重新考虑传统的DFT策略。因此一个不同的DFT策略是必要的,因为绑定前测试主要集中在片内电路的缺陷。此外,未减薄晶圆上的TSV缺陷测试需要专门的DFT和测试方法[14-16]。另一方面,减薄晶圆的绑定前测试会带来全新的挑战。

2.4 绑定前的可测性

一个更具挑战性的情况是使用端口分解施加到基于存储器结构的划分样式,其中只有1个裸片层可以在绑定前访问实际SRAM单元。然而对于其他层,如果要应对其不完整的功能就需要新的方法。对于端口分解设计技术,特别是绑定前的可测性问题,必须在逻辑设计期间考虑到。例如可以至少为每个单独的层设计出1个读端口和1个写端口,以启用绑定前测试。它可能放置测试数据于写端口,然后有数据立即从相同层的读端口反馈回来,仿佛数据被一个虚拟设备的一个存储单元通过片内通孔供给。例如它可能在绑定前值得执行一个95%的覆盖测试,而不是一个明显更昂贵的99.5%的覆盖测试。

2.5 测试的经济性

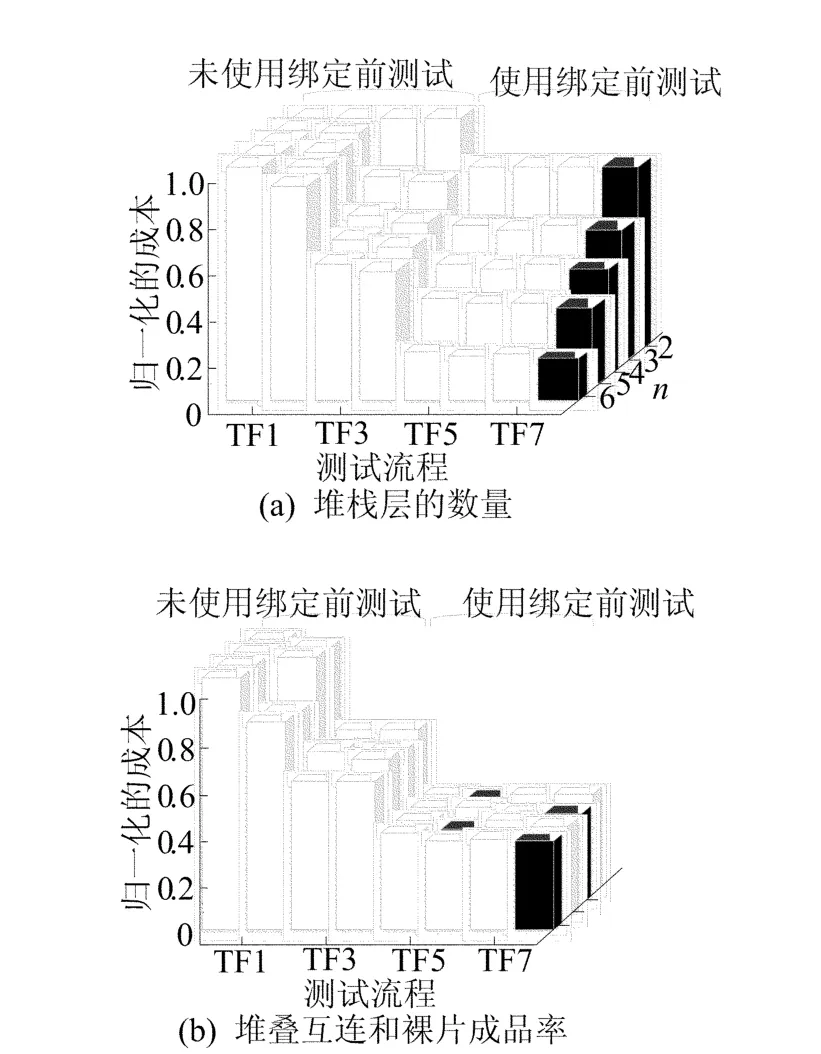

文献[17]提出了一个裸片到裸片(D2D)和裸片到晶圆(D2W)堆叠的成本模型,以制造、测试及封装的成本和成品率作为输入参数。该模型可面向基于2个关键假设的不同的测试流程:① 假设一个最终封装测试,捕获所有以前未发现的故障,与所有的测试流程相比,不同之处在于测试和产品成本,但没有传出产品质量;② 假设裸片堆叠以线性顺序发生,并且每个堆叠操作至多在2个裸片内引入新的缺陷,并在堆叠操作中参与直接互连。成本模型在测试流程产生的产品成本的比较如图3所示[17]。

图3 归一化到TF1的8个测试流程变化的成本比较

测试流程TF1中,所有的产品成本被标准化。黑色柱表示在一个特定的情况下,最低的产品总成本的测试流程。由图3可知,不包括绑定前测试的测试流程TF1~TF4比包括绑定前测试的测试流程TF5~TF8,具有较高的产品成本。

相比于D2W和D2D堆叠,晶圆到晶圆(W2W)堆叠提供了最高的生产量,允许最小的裸片尺寸,提供最薄的晶圆和最高的TSV密度。W2W堆叠的缺点是不能避免一个有瑕疵的裸片堆叠到一个良好的裸片上,反之亦然,从而导致低的复合成品率。此缺点是由大量的堆栈层数量、每块晶圆少量的裸片数和/或低裸片成品率加剧的。晶圆匹配是在预先测试的晶圆库的基础上匹配的,可以使(低)复合成品率显著增加,例如绑定前测试的成本超调[18-19]。

3 TSVs绑定后的可靠性和测试

3.1 TSVs绑定后的可靠性问题

在测试领域,3D芯片面临着新的挑战[20]。在绑定多层2D晶圆逐层堆叠制造3D芯片的过程中[21],若其中某一层发生故障未检出,就会导致绑定完成后制成的大规模多层3D芯片报废,大大增加制造成本。因此,在3D芯片制造中,在对未绑定前的2D晶圆单独测试的基础之上,还必须逐层对堆叠过程中的3D芯片半成品反复进行测试,确保每堆叠一层后的3D芯片成品的可靠性。

为了使3DICs在商业上是可行的,最关键的一步是最后的整合,必须确保只有KGDs将会被绑定和封装。随着3D层数的增加,一个随机绑定策略已经不是经济适用的,因为它可能会降低总的成品率。

3.2 TSVs绑定后的测试问题

需要在3DICs设计中考虑DFT是保证TSV绑定后成品率的关键。不过,TSVs弥补了这一基础设施的关键测试,任何有缺陷的TSV将会防止对一定的逻辑块的访问。在这种情况下,即使是一个在2层之间的单个TSV的缺陷,也可以导致整个芯片堆叠无效,降低了整体的成品率。

在一个一体化生产流程中,裸片/晶圆的生产、堆叠和封装都是在一个公司的控制下。此时,输出产品的质量通常由一个全面的最终测试确定,而任何前面的测试仅仅是最终测试的子集,以便在初期剔除掉故障部件,防止下游较高的成本。

绑定后测试主要集中在测试新成立的基于TSVs的互连。假设片内电路准备好在绑定前测试阶段被测试,如果堆叠操作有可能损坏它,那么绑定后测试只应重新测试该电路。因此,测试基础结构应该使得裸片堆叠的所有组件和互连可重新被测试。

4 结束语

3DICs已成为延长摩尔定律所预测轨迹的关键技术。本文介绍了3DICs面临的一些挑战和有关正在进行的研究工作,如测试挑战的基本概念、绑定前测试挑战和TSVs绑定后的可靠性和测试挑战。由于TSVs填充、对齐方式和绑定可造成的新的类型缺陷,研究解决方案都需要从整体上解决这些测试挑战,才能使3D集成技术被广泛采用。

[1]新兴市场趋动3D-IC发展[J].电子设计技术,2008(6):26.

[2]彭永红,辛 洁,周晓伟,等.NoC功耗与性能的研究[J].现代电子技术,2012,35(4):173-176.

[3]Lu Jianqiang,Gutmann R J.Experiences in developing a research-focused project course:IP-core based IC design enabled by 3Dwafer bonding[C]//Proceedings of the 2001International Conference on Microelectronic Systems Education(MSE’01),2001:9-90.

[4]王 伟,高晶晶,方 芳,等.一种针对3D芯片的BIST设计方法[J].电子测量与仪器学报,2012,26(3):215-222.

[5]Chan Mansun.The potential and realization of multi-layers three-dimensional integrated circuit[C]//Solid-State and Integrated-Circuit Technology,2001,Proceedings,6th International Conference on,2001,1:40-45.

[6]Lee H,Chakrabarty K.Test challenges for 3Dintegrated circuits[J].IEEE Design & Test of Computers,2009,26(5):26-35.

[7]Marinissen E J.Challenges and emerging solutions in tes-tingD-and 3D-stacked ICs[C]//Design,Automation & Test in Europe Conference & Exhibition(DATE),IEEE,2012:1277-1282.

[8]Marinissen E J,Zorian Y.IEEE Std 1500enables modular SoC testing[J].IEEE Design & Test of Computers,2009,26(1):8-16.

[9]Ingelsson U,Goel S K,Lasson E,et al.Test scheduling for modular SoCs in an abort-on-fail environment[C]//Proceedings of IEEE European Test Symposium (ETS),2005:8-13.

[10]Mak T M.Testing of 3Dcircuits[M]//Garrou P,Bower C,Ramm P.Handbook of 3DIntegration:Technology and Applications Using 3DIntegrated Circuits.Wiley-CVH,2008:623-633.

[11]Zorian Y.Multi-chip module test strategies[M].Kluwer Academic Publishers,1997.

[12]Lewis D L,Lee H.A scan-island based design enabling pre-bond testability in die-stacked microprocessors[C]//Proc Int Test Conf.IEEE CS Press,2007:1-8.

[13]Park D,Eachempati S,Das R,et al.MIRA:a multi-layered on-chip interconnect router architecture[C]//Proc 35th Int Symp.Computer Architecture (ISCA 08).IEEE CS Press,2008:251-261.

[14]Tsai M,Klooz A,Leonard A,et al.Through silicon via(TSV)defect/pinhole self test circuit for 3D-IC[C]//Proceedings of IEEE International Conference on 3DSystem Integration(3DIC),2009:1-8.

[15]Chen Poyuan,Wu Chengwen,Kwai D M.On-chip TSV testing for 3DIC before bonding using sense amplification[C]//Proceedings of IEEE Asian Test Symposium(ATS),2009:450-455.

[16]Chen Poyuan,Wu Chengwen,Kwai D M.On-chip testing of blind and open-sleeve TSVs for 3DIC before bonding[C]//Proceedings of IEEE VLSI Test Symposium(VTS),2010:263-268.

[17]Hamdioui S,Beenakker K,Mottaqiallah T.Test cost anal-ysis for 3Ddie-to-wafer stacking[C]//Proceedings of IEEE Asian Test Symposium (ATS),2010:435-441.

[18]Verbree J,Marinissen E J,Roussel P,et al.On the cost-effectiveness of matching repositories of pre-tested wafers for wafer-to-wafer 3Dchip stacking[C]//Proceedings of IEEE European Test Symposium (ETS),2010:36-41.

[19]Taouil M,Hamdioui S,Verbree J,et al.On maximizing the compound yield for 3Dwafer-to-wafer stacked ICs[C]//Proceedings of IEEE International Test Conference(ITC),2010:1-10.

[20]Lin Yumin,Zhan Haujie,Kao Kuoshu,et al.Low temperature bonding using non-conductive adhesive for 3Dchip stacking with 30μm-pitch micro solder bump interconnections[C]//Electronic Components and Technology Conference(ECTC),2012:1656-1661.

[21]Matsumoto K,Ibaraki S,Sakuma K,et al.Thermal resistance evaluation of a three-dimensional(3D)chip stack[C]//Electronics Packaging Technology Conference(EPTC),2010:614-619.