基于概率签名的硬件木马检测技术

郑朝霞,李一帆,余 良,田 园,刘政林

基于概率签名的硬件木马检测技术

郑朝霞,李一帆,余 良,田 园,刘政林

(华中科技大学光学与电子信息学院,武汉 430074)

针对集成电路芯片被植入硬件木马后带来的安全问题,提出一种基于概率签名的硬件木马检测技术。通过逻辑功能检测,采用随机算法构建芯片电路(布尔函数)的概率签名,作为唯一的识别符模板,当被测电路的签名与模板不匹配时发出告警。设计全加器和AES加密2款电路,植入常见硬件木马并进行攻击实验,对这2种电路的原始电路以及植入硬件木马后电路的概率签名是否发生改变进行理论分析与研究。采用统计学参数估计法在FPGA平台进行实验,结果表明,该概率签名技术能检测出一般规模组合逻辑电路中植入的硬件木马,置信度达到95%。

集成电路芯片;硬件安全;硬件木马;概率签名;AES加密

1 概述

近年来,硬件木马引起了世界各国工业界和学术界的极大关注[1],众多国外大学和科研机构就这一领域展开了研究,并在硬件木马实现技术[2]方面取得了相当的研究成果[3],而针对硬件木马检测[4]技术,目前的研究主要集中于电流、电压[5]等电路旁路信息[6]方面。国内鲜有相关文章发表,由于硬件木马等恶意电路的隐蔽性,攻击者可以利用其窃取机密信息,破坏硬件电路,造成严重的经济损失与社会危害。本文研究了概率签名技术在硬件木马检测中的有效性,基于一位全加器和AES加密电路,对它们分别植入硬件木马,然后对这2种电路污染前和污染后的概率签名进行理论分析与FPGA实验验证。

2 电路的概率签名原理

根据这一理论可以分析测试芯片的概率签名是否与原始设计电路的概率签名一致,以判断该芯片是否被植入了硬件木马,而原始电路的概率签名可以直接在设计时得到。

3 一位全加器电路的概率签名木马检测

3.1 一位加法器的概率签名

根据电路概率签名的原理,研究其在简单电路中的硬件木马检测应用,设计了一个原始的一位全加器,其电路如图1所示,其逻辑表达式如下:

3.2 植入硬件木马的一位全加器概率签名改变

分别采用2种木马插入方式来研究该全加器的概率签名在受污染后是否发生概率签名,具体实验如下:

(1)针对和信号的木马植入及其概率签名改变情况

图2 针对和Si信号的木马插入

(2)针对进位的木马植入及其概率签名改变情况

假设另外一种木马破坏情况,假设电路的+1输出出错,电路受到木马干扰后电路改变如图3所示。

图3 针对进位Ci+1的木马插入

4 AES电路的概率签名木马检测

对于输入端口较多的设计,在其概率签名的计算中,输入概率分布会趋向于一个数量级庞大的分式表达式,造成电路概率签名的获取实际上变得不可行。因此,对于一个输入输出端口较多的设计,无法直接按照上述方案进行概率签名分析。

4.1 原始AES的电路设计

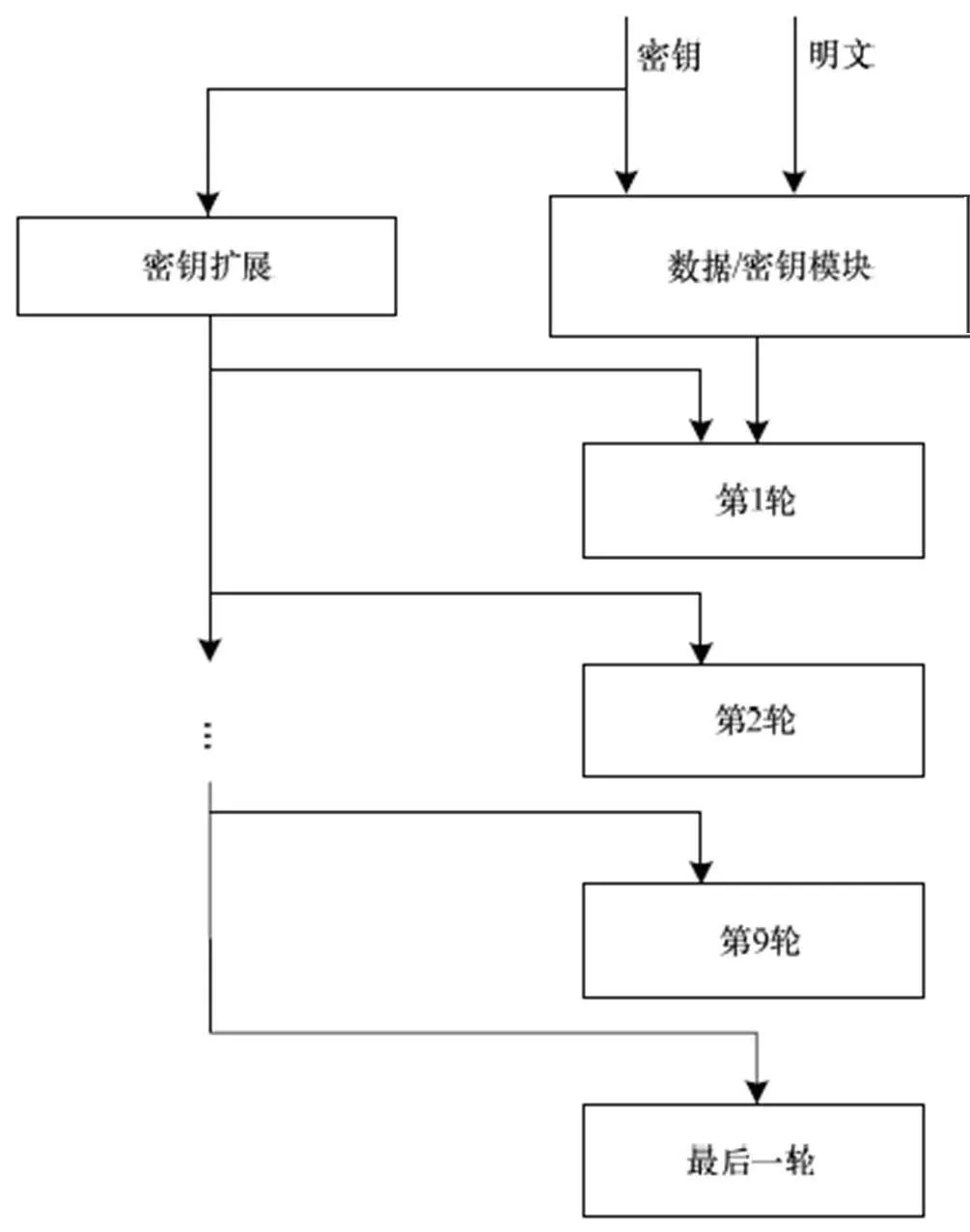

AES算法[11]是一种典型的迭代型分组密码,它的分组长度和密钥长度均是在128bit、192bit或者256bit这3种中进行选取。

本文取分组长度和密钥长度均为128 bit,因此,这里的AES算法是将输入的一组数据(明文或密文)划分成 16 Byte,以4×4状态矩阵的形式对其进行后续操作,具体流程如图4所示。首先进行初始密钥加(add round key)操作,即数据和密钥的异或运算。然后便开始总共10轮的轮变换操作,每一轮依次经过字节代换(substitute byte)、行移位(shift row)、列混合(mix column)和轮密钥加(add round key) 4步变换,其中,第10轮不进行列混合(mix columns)操作。对于解密操作,其与加密过程类似,可分为直接解密和等价解密,在等价解密算法中,只需将每一轮中的各个替换成相应的逆操作,而顺序保持不变,同时将用于密钥加操作的轮密钥做出相应的调整。

图4 AES加密算法流程

4.2 AES电路的硬件木马插入与实现

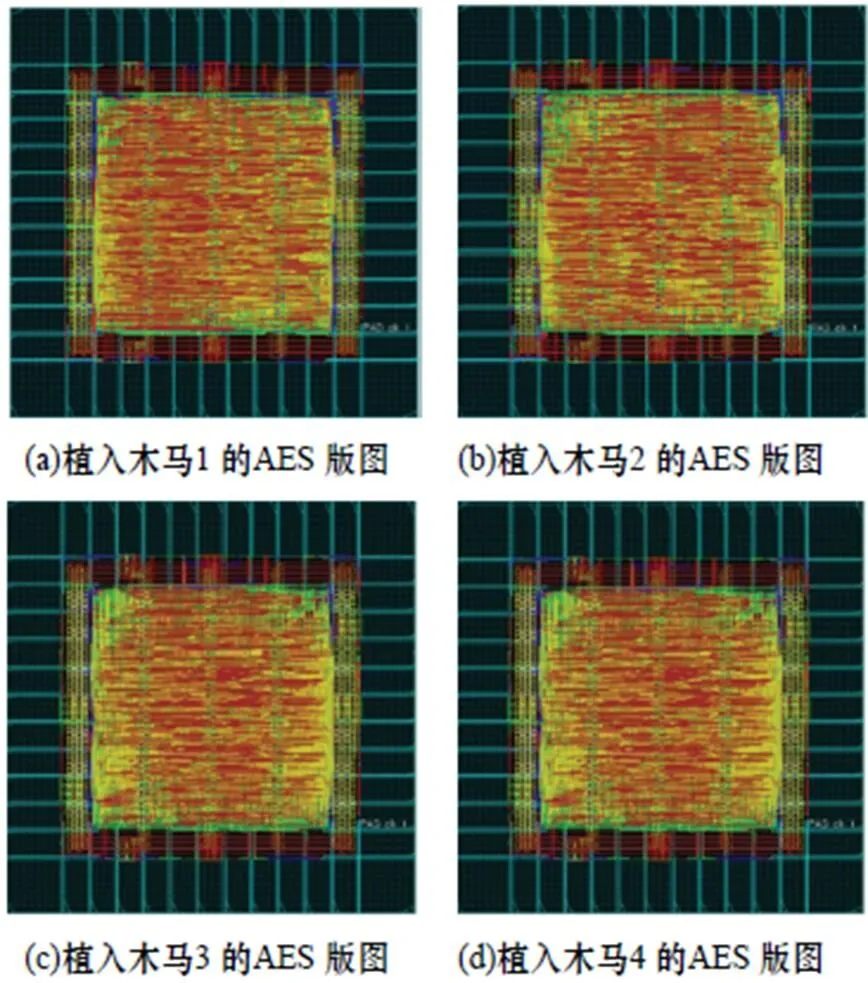

根据对硬件木马的分类,实现了下面这4种硬件木马,用于植入到本文AES加密的关键路径S盒设计中[12]:

(1)硬件木马1:小规模组合电路,对输入明文寄存器text_in_r中的连续某些位与特定的数据进行比较,当两者一致时触发木马,此时将输入明文某一个字节相对应的初始密钥sa22加1。

(2)硬件木马2:时序计数器电路,电路开始工作时开始计数,当计到某一个较大的数量时触发木马,此时将篡改轮变换中某一字节轮密钥sa22_next的输出。

(3)硬件木马3:序列检测器,检测输入明文的某一位,此处对text_in进行检测,当检测出特定的序列时触发木马,将加密输出text_out篡改为所输入的明文。

(4)硬件木马4:输入条件比对,当输入明文为某一特定数据时触发木马,将此时的密钥作为输出。

将4种硬件木马分别植入AES加密电路,然后基于联电UMC 0.18 μm工艺分别对其进行ASIC后端设计,其最终的版图结果如图5所示。

按照最终的芯片密度及最初的布局规划换算得到core等价面积(含布线)如表1所示。从表1中可以看出,本文插入的木马对版图面积的影响微乎其微,控制在0.1%~0.3%左右。

图5 4种硬件木马的AES最终版图

表1 带木马AES与原始AES后端面积对比

4.3 概率签名的实验结果

在本文实验中,基于Altera的DE2-70开发板,利用Nios II软核,设计硬件木马的测试与侦测平台如图6所示。

图6 基于FPGA的硬件木马实验平台

在该FPGA平台上,同时实现2种AES模块:原始的AES模块和植入有木马的AES模块。通过控制电路,按照概率签名要求输入测试向量,将128位明文和初始密钥同时送入2个AES模块中,然后测试输出为1的次数,并对样本数据进行统计分析、参数估计,评估出被测电路的概率签名,然后同原始电路的概率签名进行比对,从而概率性地判断该电路模块是否遭到篡改,从图6中可以看到,当受硬件木马污染的电路触发时,利用Nios软核编写相应软件,可将相关结果通过控制窗口打印显示出来。

接下来尝试采用概率签名对这些受木马污染的AES电路进行侦测的可能性。sbox-square模块是用于实现S盒中的平方运算,由于模块的输入、输出均为4位,对于该电路模块的输入端口,按照概率签名原理要求进行赋1。其中以更严格的要求,根据输入数量,取4,=0表示0,=1表示1,=2表示2,=3表示3。以此对4个输出端0、1、2、3分别计算它们的概率签名。通过计算分别得到原始电路中0的概率签名为0.202,1的概率签名为0.996,2的概率签名是0.058 8,3的概率签名是0.999,这样在电路设计时便得到sbox-square电路模块的“唯一标示符”。

然后采用概率统计的方法,基于DE2-70的FPGA平台对上面4种受不同硬件木马污染的电路进行侦测测试。通过编写软件来实现电路的概率签名统计,步骤如下:

(1)按照概率签名原理要求对输入端口赋值1,并将其施加到被测电路和原始电路中。

(2)如果对于某一特定输入向量,如果被测电路和原始电路的概率签名不同,算法终止并以该输入向量作为被感染硬件木马的鉴别指纹。

(3)在施加了个向量后,并且被测电路和设计电路的输出均相同,便可运用统计学推理得出一个能说明它们的概率签名相同的置信区间,即被测电路无木马[8]。

因为输入向量服从正态分布,假定能接受的被测电路无木马的置信度为95%,则=0.05,当仿真向量的个数为1 000时,可计算得到检验统计量0为-1.025,0.025=1.96,由于本文情况中-1.96≤0≤1.96,可以95%地确信被测电路不含木马并且以此终止测试。如果在经过次模拟仿真后,被测电路的各个输出与设计相比均未表现出差异,那么要求与每个主要输出相应的假设的置信度至少要达到能断定被测电路无木马的必须的置信度大小。因此,如果要求能以95%的置信度判定一个被测电路无木马,那么对于被测电路的每一个输出,能够说明输出为1的平均值等于概率签名的这一假设成立的显著性为0.05。

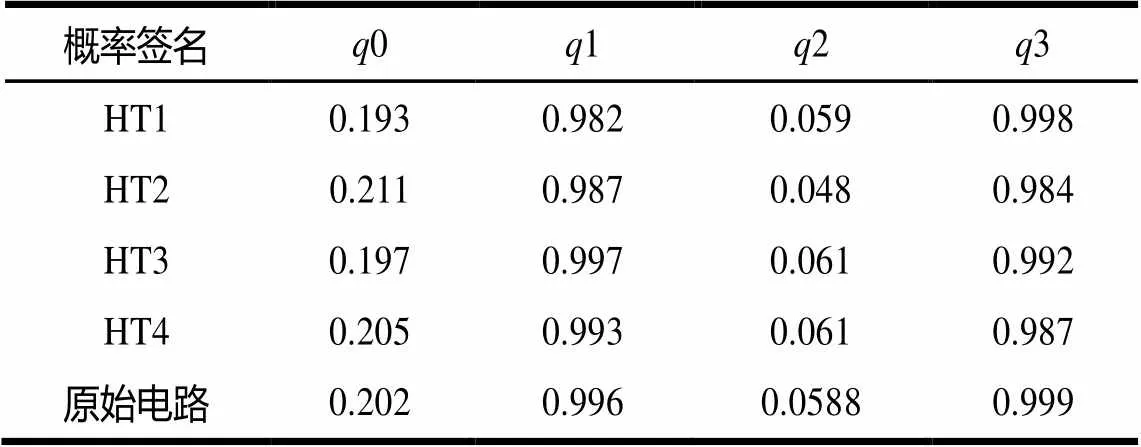

本文对4种植入了不同木马的样片分别进行1 000次实验,利用参数估计分别计算出它们的概率签名如表2所示,表2中第2行~第5行分别是插入4种不同硬件木马后的概率签名,最后一行是没有受到硬件木马污染的电路的概率签名,从表中可以看出,被硬件木马污染后电路的概率签名不在原始电路概率签名95%的置信空间内,换句话说,被硬件木马污染的AES样片通过检测其概率签名是可以被检测出来的。

表2 AES电路的概率签名参数估计

5 结束语

本文分别对2个组合电路:一位全加器和AES加密电路进行了硬件木马植入,然后基于概率签名进行了硬件木马检测技术研究,实验结果表明该方法是可行的。尽管在现阶段的研究中这种概率签名分析只能应用到组合逻辑电路中,但在实际芯片的硬件木马检测中,为了降低检测复杂度,可以利用拆分电路的思想分别对芯片中各个关键的子模块进行概率签名分析,然后将所有这些概率签名信息综合起来,视作鉴别指纹进行硬件木马的检测与定位。

[1] Wolff F, Papachristou C, Bhunia S, et al. Towards Trojan-free Trusted ICs: Problem Analysis and Detection Scheme[C]// Proc. of Conference on Design, Automation and Test in Europe. Munich, Germany: IEEE Press, 2008.

[2] King S T, Tucek J, Cozzie A, et al. Designing and Imple- menting Malicious Hardware[C]//Proc. of the 1st USENIX Workshop on Large-scale Exploits and Emergent Threats. San Franciso, USA: IEEE Press, 2008.

[3] Alkabani Y, Koushanfar F. Extended Abstract: Designer’s Hardware Trojan Horse[C]//Proc. of IEEE International Workshop on Hardware-oriented Security and Trust. Anaheim, USA: IEEE Press, 2008.

[4] Ratanpal G B, Williams R D, Blalock T N. An On-chip Signal Suppression Countermeasure to Power Analysis Attacks[J]. IEEE Transactions on Dependable and Secure Computing, 2004, 1(3): 179-189.

[5] Rad R, Plusquellic J, Tehranipoor M. Sensitivity Analysis to Hardware Trojans Using Power Supply Transient Signals[C]// Proc. of IEEE International Workshop on Hardware-oriented Security and Trust. Anaheim, USA: IEEE Press, 2008.

[6] Agrawal D, Baktir S, Karakoyunlu D, et al. Trojan Detection Using IC Fignerprinting[C]//Proc. of IEEE Symposim on Security and Privacy. Oakland, USA: IEEE Press, 2007.

[7] Jha S, Jha S K. Randomization Based Probabilistic Approach to Detect Trojan Circuits[C]//Proc. of the 11th IEEE High Assurance Systems Engineering Symposium. Nanjing, China: IEEE Press, 2008.

[8] Wu S C, Wang Chunyao. Peach: A Novel Architecture for Probabilistic Combinational Equivalence Checking[C]//Proc. of IFIP International Conference on Very Large Scale Integration. Nice, France: IEEE Press, 2006.

[9] Rivest L, Shamir A, Adleman L. A Method for Obtaining Digital Signature and Public Key Cryptosystems[J]. Communications of the ACM,1978, 21(2): 120-126.

[10] Jain J, Abraham J A, Bitner J R, et a1. Probabilistic Verification of Boolean Functions[J]. Formal Methods in System Design, 1992, 1(1): 61-115.

[11] Daemen J, Rijmen V. 高级加密标准(AES)算法: Rijndael的设计[M]. 谷大武, 徐胜波, 译. 北京: 清华大学出版社, 2003.

[12] 余 良. 数字IC中硬件木马的特性与检测技术研究[D]. 武汉: 华中科技大学, 2012.

编辑 任吉慧

Hardware Trojan Detection Technology Based on Probabilistic Signature

ZHENG Zhao-xia, LI Yi-fan, YU Liang, TIAN Yuan, LIU Zheng-lin

(School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China)

Trojan circuits can bypass traditional defensive techniques as they occupy a layer below the entire software stack. This paper proposes a hardware trojan detection technology based on probabilistic signature. Based on logic detection technology, using random and hypothesis algorithm, this paper constructs the probability signature of circuits(Boolean functions), as the unique identifier template. When the signature of circuit under test does not match the template, an alarm is launched. It designs two circuits that implement full adder and AES encryption, and then they are implanted with common hardware Trojan. It makes in-depth theoretical analysis and research on whether the probabilistic signature of the circuits implanted with hardware Trojans is changed in comparison with the two kinds of original circuits. It tests the circuits based on FPGA platform via probabilistic method. As a result, it is verified that based on the probability signature, it can easily achieve a 95% level of confidence on the detection of hardware Trojans implanted into the combinational logic circuits.

integrated circuit chip; hardware security; hardware trojan; probabilistic signature; AES encryption

1000-3428(2014)03-0018-05

A

TN452

国家自然科学基金资助项目(61006020)。

郑朝霞(1975-),女,副教授、博士,主研方向:SoC及其安全技术;李一帆、余 良、田 园,硕士研究生;刘政林,教授、博士。

2013-08-09

2013-10-10 E-mail:zxzheng@hust.edu.cn

10.3969/j.issn.1000-3428.2014.03.004