基于FPGA的多路竞赛抢答器设计

冀 云

(重庆电子工程职业学院应用电子学院,重庆 401331)

基于FPGA的多路竞赛抢答器设计

冀 云

(重庆电子工程职业学院应用电子学院,重庆 401331)

基于ISE软件开发环境,运用VHDL硬件描述语言,设计了一款4路竞赛抢答器,给出了抢答器系统的系统功能模块;对设计工程进行了综合、编译、仿真,并下载到FPGA芯片xc3s700a-5fg484进行测试;结果表明设计能实现系统预期的功能。

竞赛抢答器;VHDL;仿真波形;硬件测试

抢答器在各种竞赛性质的场合有非常广泛的应用,它由组合逻辑电路进行状态判断与选择,消除了原来由于人眼的误差而未能正确判断最先抢答的选手的情况,从而避免了竞赛场合出现不必要的争执。现行的抢答器设计方案主要有两种:采用触发器和小规模组合逻辑芯片实现;用单片机配合外围电路实现。方法一的优点是思路简单且存在比较成熟的设计范例,但具体电路复杂,元器件较多;相对来说使用单片机实现比较灵活,但如果选手人数较多则会出现I/O口不足的问题。设计采用FPGA现场可编程技术,完全由HDL硬件描述语言实现抢答功能,避免了硬件电路的焊接调试,同时由于FPGA的可编程资源及I/O端口丰富,可以在设计的基础上进行自由改进。

1 抢答器原理及结构

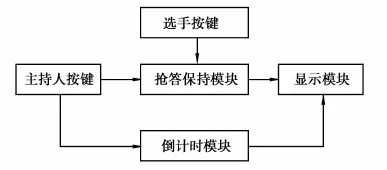

抢答器的原理比较容易理解,首先必须设置一个抢答允许标志位,目的就是用于允许或禁止抢答者按键;如果允许抢答位有效,那么第一位按键的抢答者按下按键的就会将其清除,同时记录下按键者的编号并显示,达到后面的抢答者按键都无效化的效果。系统设计一个多路竞赛抢答器,具有4路抢答输入,每人可通过按键手动申请抢答,要求能够识别第一个抢答的信号,点亮对应的LED表示抢答成功,同时其他选手按键失效;七段数码管对选手序号和抢答所剩的时间进行计时、显示。系统设计结构如图1。

图1 系统结构

2 基于FPGA的抢答器设计

FPGA(现场可编程门阵列)是一种SRAM生产工艺的复杂可编程逻辑器件,基于查找表(LUT)结构技术,当用户描述了一个逻辑电路之后,设计软件会自动计算其所有可能存在的结果,并优先写入RAM。这样每输入一个信号进行逻辑运算就相当于输入一个地址进行查表,找到对应内容的输出结果。

由于FPGA基于查找表结构,因此它不受传统的PLD“与或”阵列的限制以及触发器和I/O端口数量的限制,具有更高的集成度、更强的逻辑实现能力和更好的设计灵活性。而且相对于一般的集成块和单片机,FPGA还具有逻辑块粒度小、运算速度快、逻辑利用率高、使用方便、功耗低等优势。

以往的抢答器设计往往采用小规模集成块,单片机或者FPGA的原理图或混合编辑设计,而系统采取纯文本编辑的方式进行设计,完全用HDL硬件描述语言完成系统功能。因为HDL硬件描述语言为行为描述方式,与具体的硬件电路和设计平台无关,这样不仅描述方便,而且更具灵活性,占用资源更少,同时更易进行修改,具有可移植性。

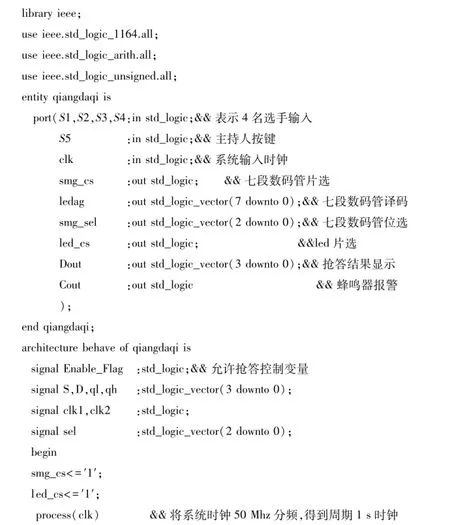

2.1 竞赛抢答器HDL程序设计

主持人启动抢答按钮后,倒计时开始工作,从40 s递减,同时允许4名选手进行按键抢答,若40 s内无人抢答,则计时保持在00,蜂鸣器报警;若在此期间有人抢答,则计时停止,点亮对应选手LED,其他选手按键无效,七段数码管显示选手序号并保持在抢答信号输入时的时间,10 s减去显示时间即为抢答所用时间。对应HDL代码如下:

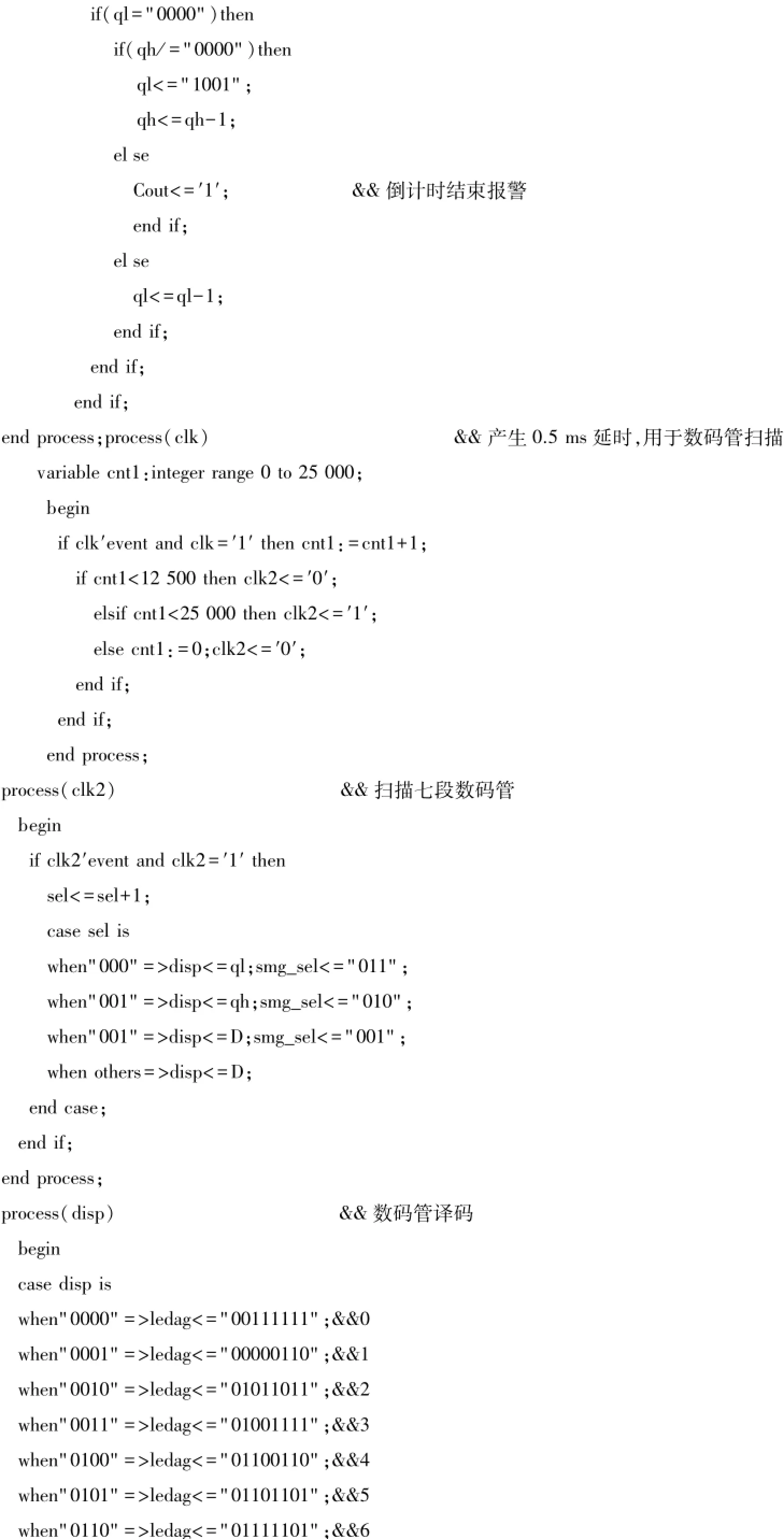

2.2 程序仿真

由于该系统时钟为50MHz,分频得到周期为1 s时钟用于倒计时,仿真器时间无法设置过长,所以采用原始时钟clk直接做仿真。七段数码管采用扫描显示的方式,故通过仿真只能看到计时低位的段码值。综上采取功能仿真,仿真器为ISE Simulator 9.2,功能仿真结果如图2。

图2 功能仿真波形

由仿真波形可见,S5键按下之后,旗标置1,倒计时开始,数码管显示倒计时时间,当选手键S2按下后,倒计时停止,旗标清零。故此设计能够完成抢答器的要求。

2.3 约束和配置下载

设计所选用硬件为CREATE公司的SOPC3000系统,主芯片采用XILINX公司的Spartan3A系列芯片xc3s700a-5 fg484,定义约束为取clk为50 M系统时钟,核心板按键S1为主持人按键,4位选手按键为K1~K4,七段数码管分别表示抢答成功选手序号以及倒计时,下载后得到结果如图3。

由图可见,此时2号选手抢答成功,数码管显示选手序号和倒计时停留在35 s,同时选手对应的LED点亮。此设计符合要求,可以完成系统功能。

3 结 语

运用XILINX公司ISE软件开发平台,设计了基于FPGA的4路竞赛抢答器,进行了功能仿真并且下载到xc3s700a-5fg484芯片中完成硬件调试检测,结果表明本设计能实现选手按键互锁,正确显示最先抢答的选手序号,并对答题时间进行40 s的倒计时报警以及复位重新抢答功能。设计全部由VHDL硬件描述语言实现,简明易懂,具有良好的修改和可移植性,但也存在如代码较长,设计成本相对传统方式较高等有待改进之处。

图3 硬件测试结果

[1]王正勇.EDA技术与应用教程[M].北京:高等教育出版社,2011

[1]刘睿强.FPGA应用技术及实践[M].北京:北京理工大学出版社,2011

[3]张占锋.基于FPGA智力竞赛抢答器的设计[J].大众科技,2008(12):43-44

[4]褚红燕,沈世斌.基于EDA技术的层次化设计方法在电子抢答器中的应用[J].电子工程师,2005(9):66-68

[5]杨俊秀.基于FPGA的多路抢答器设计与实现[J].浙江理工大学学报,2010(3):250-253

Design of Multi-channel Competition Responders Based on FPGA

JIYun

(School of Applied Electronics,Chongqing College of Electronic Engineering,Chongqing 401331,China)

Based on ISE software development environment,by using VHDL hardware description language,this paper designs a kind of four-channel competition responder,gives systematic function module of the responder system,conducts synthesizing,compiling and simulating implementation on designed project,and tests the functions by downloading themodule to FPGA chip xc3s700a-5fg484.The results show that this design can realize the expected functions of the design.

competition responder;VHDL;simulation waveform;hardware test

TN421

A

1672-058X(2014)03-0060-06

责任编辑:代小红

2013-10-10;

2013-11-11.

冀云(1984-),男,讲师,硕士,从事电子系统设计、FPGA应用开发研究.