采用FPGA实现同步串行数据的并行采集

严刚峰 方红 杨维 郭兵

(成都大学电子信息工程学院1,四川 成都 610106;四川大学计算机学院2,四川 成都 610065)

采用FPGA实现同步串行数据的并行采集

严刚峰1,2方红1杨维1郭兵2

(成都大学电子信息工程学院1,四川 成都 610106;四川大学计算机学院2,四川 成都 610065)

同步串行接口具有传输速度快、抗干扰能力强等特点,在具有串行数据传输的电子设备中得到了广泛的应用。同步串行数据的接收需要专用芯片,这使得具有同步串行接口的电子设备的应用受到了限制。针对具有同步串行接口的绝对值编码器,提出了串行数据转换和读取的实现方法,给出了详细的硬件原理图及其电路设计要点,并提供了关键的软件代码。这为具有同步串行接口设备的数据并行采集提供了一种低成本的实现方案。

同步串行接口 FPGA DSP 数据采集 串并转换 硬件设计

0 引言

数据的传输有串行和并行两种方式[1],其中串行方式又可分为同步串行接口和异步串行接口两种。较异步串行方式,同步串行方式传输速度更快,同时还具有连线简单、抗干扰能力强等突出优点,因此同步串行接口已成为一种常用的工业用通信接口。目前,常见的同步串行接口转换器大多是将同步串行信号转换成异步串行信号[2-4],以实现两个互不同步设备之间的数据通信。与并行方式传输数据相比,串行方式的数据传输速率太低,严重影响数据采集的实时性,具有同步串行接口的电子设备一般不会提供串/并行转换的接口,往往需要购置专用的接口芯片或模块[5],因此提高了同步串行接口电子设备的使用成本。

本文采用具有同步串行接口的位置式光电编码器作为数据源,光电编码器是将连接轴的角度量转换成相应的电脉冲序列或以数字量的形式输出,具有体积小、精度高、易于安装等优点,被广泛应用于高速伺服系统、数控机床、机器人等诸多领域。较增量式光电编码器,位置式光电编码器不产生脉冲,而是输出一串数据码,为轴位置提供一个独一无二的编码数字值,减轻了电子接收设备的计算任务;同时,当电源发生故障时,位置式光电编码器还具有位置记忆功能,因此得到了广泛的应用。用于数据读取的电子系统则是采用DSP+FPGA结构,这样只需要在设计电路时,增加时钟控制电路和数据接收电路,配合FPGA就可以实现对同步串行的高速并行采集。这为具有同步串行接口设备数据的并行采集提供了一种低成本的实现方案。

1 硬件设计

1.1 同步串行信号标准模式

同步串行接口编码器根据时钟控制模块向绝对值编码器发送一串时钟脉冲,绝对值编码器立即送出相应的串行位置数据[6-9]。同步串行数据输出过程为:当在空载条件下,信号线“数据+”和“时钟+”为高电平;控制时钟信号第一次从高电平跳至低电平时,储存在编码器的当前数据即进行传输;在第一个脉冲上升沿到来时,编码器串行数据首位(MSB)输出;随着一个个脉冲上升沿的到来,数据逐位传输,直到最后一位(LSB)传输完毕。单稳态触发时间Tm截止前,数据线跳至低电平,数据线跳至高电平之前或时钟中断Tp时间截止前不会有数据传输进行。在时钟序列结束后,单稳态触发时间Tm由最后一个脉冲下降沿触发。单稳态触发时间Tm决定了最低的传输频率。

1.2 硬件电路设计

采用TI公司的DSP处理器TMS320F28332与Altera公司CycloneIII系列FPGA芯片EP3C10E144C8N设计的硬件连接原理如图1所示。

图1 硬件连接原理图Fig.1 Schematic diagram of the hardware connections

图1中,编码器为多圈25位具有同步串行接口的绝对值式角度编码器。

时钟控制模块电路如图2所示。

图2 时钟控制模块电路图Fig.2 The circuit of clock control module

时钟控制模块电路采用的芯片是26LS31高速差分线路驱动器。26LS31具有单电源供电、驱动能力强、三态输出、可靠性高的特点,符合RS-422标准,被广泛应用于串行通信电路中。电路设计时注意在电源管脚处加1个0.1 μF的去耦电容。

数据接收模块采用的芯片是6N137光电耦合器。6N137适合于单通道高速光电信号的耦合,其检测器由1个光敏二极管、高增益线性运放以及1个肖特基钳位的集电极开路三极管组成,具有温度、电流和电压补偿功能。设计该电路时,在6N137光电耦合器电源管脚需加1个0.1 μF的去耦电容,电容应尽量选用高频特性好的电容器,如陶瓷电容或钽电容。电容的位置要尽量靠近光耦的电源引脚处。6N137的6号引脚输出为集电极开路电路,必须有上拉电阻,阻值在750 Ω左右。6N137的2和3号引脚之间是LED,注意要串接1个330 Ω左右的限流电阻。

数据接收模块电路如图3所示。

图3 数据接收模块电路图Fig.3 The circuit of data receiving module

使用编码器时,编码器必须工作在最佳的安全电压,因此,编码器要尽量单独供电,忌高干扰电源,如变频器、接触器等。如有必要,可考虑安装电源滤波器。此外,电源线不要串进信号输出端,负载应根据最大输出电流来配置。电磁场干扰是编码器不稳定和失效的主要原因,所以可考虑使用屏蔽双绞电缆以提高信号传输的可靠性;信号电缆还要注意远离电机、变压器等严重电磁场干扰的设备,电缆铺设时注意信号电缆与电源电缆、大功率电缆与高噪声电缆要分开铺设;当使用金属电缆支架时,要保证支架连接处导通接地,电缆的屏蔽层可以对电磁干扰进行放电;连接屏蔽电缆时,屏蔽层的两侧均应通过低电阻和低电感接地,对于编码器屏蔽线接地时,屏蔽线和0 V线不要接在一起。考虑到通信的距离与传输的速率相关,当传输距离较长时,注意数据读取控制模块所设置的时钟控制频率要小于理论传输速率。

2 软件设计

2.1 串并转换程序设计

FPGA的核心代码如下。

其中,第一个过程程序完成数据的串并转换,第二个过程程序实现DSP将转换好的25位数据进行分次读取的功能。f_clk为DSP提供给FPGA的时钟信号; rst为复位信号,低电平有效;xrw为外部读使能信号,高电平有效;en为启动串并转换信号,高电平有效;cnt为控制时钟计数信号,用于控制输出时钟的周期个数; clk为提供给编码器的时钟信号;din为编码器的串行数据输入信号;reg用于存放并行数据;en_out为时钟信号输出使能信号;end_rd为DSP读取使能信号;ssi_ en为高、低位输出控制信号;data_bus为16位数据线。

2.2 DSP读取转换结果程序设计

通过TMS320F28332芯片的XCLKOUT管脚向FPGA提供时钟信号。时钟频率寄存器的设置如下。

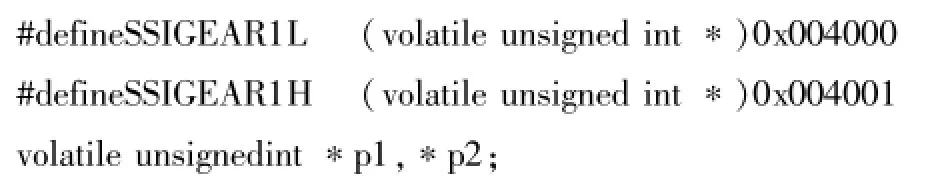

TMS320F28332芯片有多个采用非复用异步总线的片外存储器与外部接口XINTF[9]。每个XINTF区都有一个片选信号,用于访问某一个特定的区域。这里用到的是TMS320F28332的XINTF Zone 0,其基地址为0x004000。定义数据读取的指针如下。

数据的读取代码如下,其中SSIL存放转换好数据的低16位,SSIH存放转换好数据的高9位,组成完整的25位数据放在SSIVAL中,实现程序如下。

3 结束语

本文采用DSP+FPGA结构,对具有同步串行接口位置式光电编码器的数据实现了高速并行采集,提出了串行数据转换和读取的具体实现方法,给出了详细的硬件原理图及其设计要点,并提供了关键的软件代码。FPGA实现对绝对值编码器同步串行数据的读取以及串并转换功能,DSP完成并行数据的读取。整个功能的实现不需要额外购买专用串并转换芯片,只要在印制板中增加时钟控制电路和数据接收电路,就可以对同步串行接口编码器的数据进行采集。采集程序已成功应用于某风电项目的桨叶齿圈桨距角绝对值编码器的数据采集,运行稳定可靠。

本文提出的串/并行转换方法为电子设备中具有同步串行数据的并行采集提供了一种低成本、高可靠的实现方案。

[1] 张德民.数据通信[M].北京:科学技术文献出版社,1997.

[2] 陈霞,袁兆卫,李伟,等.基于FPGA的同步串行接口SPI设计[J].软件导刊,2012,10(9):92-93.

[3] 朱福益,黄忠全,张根保,等.同步串行接口QSPI应用研究[J].机械制造,2004,42(11):34-36.

[4] 戴蓉,王高鹏,齐向华.SSI-485转换器的研究与应用[J].水利水文自动化,2008,26(2):31-33.

[5] 靳红涛,赵勇进,张晓曦.一种工控机高速采集SSI接口数据的方法[J].电子元器件应用,2012,9(10):47-49.

[6] 聂旭中.编码器用SSI协议及实现[J].洛阳师范学院学报, 2010,29(2):73-75.

[7] 张子蓬,王淑青,刘辉.SSI接口的绝对值角度编码器值的读出方法研究[J].工业控制计算机,2005,18(12):4-5.

[8] 梁军,王移川.基于SSI接口的线位移传感器高速并行数据采集设计[J].测控技术,2012,31(5):53-54.

[9] 张卫宁.TMS320C28x系列DSP的CPU与外设[M].北京:清华大学出版社,2005.

Parallel Acquisition of Synchronous Serial Data Implemented by FPGA

Synchronous serial interface has been widely used in electronic equipment with serial data transmission because of its features of high transmission speed and strong anti-interference capability.Since dedicated chip is needed for receiving synchronous serial data,the application of electronic equipment with synchronous serial interface is limited.Aiming at the absolute value encoder with synchronous serial interface,the implementing method of serial to parallel data conversion and reading is proposed.The detail hardware schematic diagram and key points of circuit design are given,and the critical software coding is provided.This offers the low cost implementing scheme of data parallel acquisition for synchronous serial interface devices.

Synchronous serial interface FPGA DSP Data acquisition Serial-to-parallel conversion Hardware design

TH86

A

国家自然科学基金资助项目(编号:11205022、61332001);

四川省教育厅科研基金资助项目(编号:12ZB172);

成都大学2012年基金资助项目(编号:2012-42)。

修改稿收到日期:2014-01-15。

严刚峰(1977-),男,2011年毕业于电子科技大学检测技术与自动化装置专业,获博士学位,副教授;主要从事嵌入式系统设计、随机信号处理以及系统仿真、非线性检测技术与系统等领域的研究。