一种8051软核的用户程序在线调试方法

唐 续, 王 嘉, 蒲晓蓉

(电子科技大学 a.电子工程学院;b.英才实验学院,四川成都 611731)

0 引言

8051及其兼容的单片机是目前最普及的8位单片机,在我校国家级实验教学示范中心及其它高校实践教学中被广泛采用[1-6]。随着现场可编程门阵列(FPGA)及EDA技术的发展,微处理器(MCU)有了新的应用形式——IP核,也出现了多种针对8051 MCU的软核,如DW8051核,OC8051核、T51核及MC805l核等[7-8]。这些MCU软核促进了各种嵌入式系统和片上可编程系统(SOPC)的应用[9-11]。

本文提出一种对8051 MCU软核中应用程序在线调试的方法,以期促进EDA、单片机和SOPC综合实践教学的改革。

1 8051软核的现有应用方法

当前,8051软核的应用开发流程一般如图1所示:使用 Keil μVision[12]等常用单片机开发平台编写应用程序并离线初步调试。之后编译生成hex格式的目标文件,并将其转换为FPGA的ROM初始化文件格式。然后执行FPGA开发平台上的项目流程,生成FPGA配置数据,经JTAG接口下载到FPGA目标板,作上电验证。若结果与设计不符,将重新执行所有流程。

图1 51软核应用的开发流程

不难看出,该流程需在单片机和FPGA两类开发平台上切换。而实际应用开发中,特别是实践教学中,应用程序往往需多次修改,使得多次反复执行上述流程,相当费时。这严重制约了8051软核在实践教学和学生科技活动(如电子设计竞赛)中的运用。

为此,文献[13]提出一种在PC机上修改和编译单片机应用程序,再通过RS232串口将目标代码下载到FPGA的程序存储器中的方法。它省去了FPGA项目流程部分的工作量,但程序编制和修改仍然是离线的,未能实现在目标板上对应用作在线仿真调试。

下文以MC8051软核[14]为例,介绍一种基于在线仿真调试工具Monitor-51[12],对软核中应用程序作在线调试的方法。

2 MC8051软核介绍

MC8051是Oregano Systems公司提供的8051 MCU软核。它提供VHDL语言设计源代码,可配合各种设计平台进行综合实现。可根据实际应用需求进行配置。非常适合SOPC应用设计和实践教学[15]。

2.1 MC8051 特点

采用全同步设计,指令集和标准8051单片机全兼容。指令执行时间为1~4个时钟周期,性能优于标准8051单片机8倍左右。用户可选定时/计数器和串行接口单元的数量;可选是否提供乘法(指令MUL)、除法(指令DIV)以及十进制调整(指令DA)功能;I/O口不复用以便于灵活定制;带256 B的内部RAM;最多可扩展至64KB的ROM和64KB的外部RAM。

2.2 MC8051 组成结构

图2 MC8051组成结构

MC8051的组成结构如图2所示。顶层MC8051_top包括处理器核心MC8051_core和三个存储模块:内部存储模块MC8051_ram、外部代码存储模块MC8051_rom和外部数据存储模块MC8051_ramx。存储模块处于设计的顶层而不包括于核心内,可便于不同FPGA平台的仿真及应用设计。处理器核心MC8051_core由定时/计数器MC8051_tmrctr、算术逻辑运算单元MC8051_alu、串行接口MC8051_siu和控制单元等模块组成。定时/计数器和串行接口单元的数量N可调。图2中还给出了顶层的I/O接口。

3 Monitor-51介绍

Monitor-51是Keil μVision自带的一种利用PC机与51单片机串口通信的侵入式在线调试工具[12]。该工具在单片机系统的应用开发和教学中被广泛使用。

基于Monitor-51的调试方法对硬件有以下要求:

●硬件系统为51系列MCU。

●5KB外部程序存储器,存Monitor-51监控程序。

●256 B外部数据存储器,存监控数据;

东莞理工学院理工科学生数学课程历年成绩分析 刘群锋,姚嘉茹,赵子瑛,尹燕君,李健仪,徐珍树,白乐(100)

●外部数据存储器总容量必须足够容纳所有应用程序代码及数据,且必须为冯·诺伊曼存储结构,即能统一寻址外部数据空间与代码空间,以实现载入执行和修改用户代码的功能。

●占用一个定时器作为串口波特率发生器。

●6 B的空余堆栈。

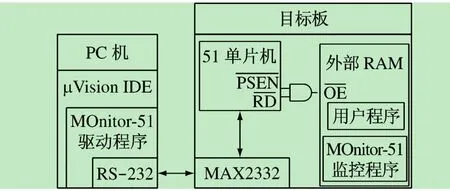

标准51单片机采用的是代码空间和数据空间相互独立的哈佛存储结构。为获得冯·诺伊曼存储结构,标准做法如图3所示,把目标单片机的PSEN引脚和RD引脚取逻辑“与”,再接外部存储器的OE端,从而合并了外部程序空间和外部数据空间。由此,PC机端运行于Keil μVision集成开发环境(IDE)的应用程序和调试信息,通过Monitor-51驱动程序,经RS-232接口传送给目标板上的51单片机,由Monitor-51监控程序分析处理并反馈回PC机,实现单步、全速和断点等方式执行,并能观察各变量和寄存器的值。

图3 Monitor-51调试51单片机系统的电路结构

4 MC8051核中应用程序在线调试方法

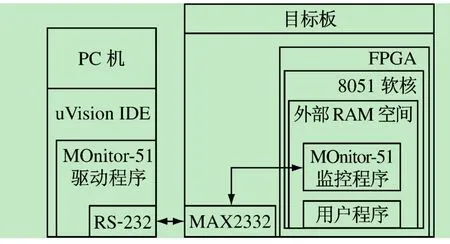

下面提出利用Monitor-51工具,通过标准串口对定制于FPGA中的51软核的用户程序进行在线调试的方法。该方法工作原理如图4所示,和Monitor-51标准用法相似。实现该方法的步骤包括Monitor-51配置和51软核定制两部分。

4.1 Monitor-51监控程序定制

如图4所示,Monitor-51需驻留一段监控程序代码在目标系统的存储空间。为能使该监控程序根据不同目标系统而定制,Keil软件提供两部分文件:INSTALL.A51和 MON51.DLL(与生成监控程序相关的文件均位于Keil软件安装路径下的C51MON51目录中)。其中MON51.DLL为完成 Monitor-51所有功能的库文件,INSTALL.A51则以51汇编源代码的形式提供了定制的接口。最终的目标代码(hex格式)通过参数化脚本文件INSTALL.BAT编译生成。

图4 51软核中用户程序在线调试原理示意

这里,目标系统是MC8051核,需定制的内容有:

(2)配置单片机的外部存储空间。本方法为用户提供直接的零地址仿真调试方式[16],使用户程序不做特别更改就能开展仿真调试。为此,对MC8051软核的外部存储空间,从零地址开始,依次分配给用户程序、用户数据、Monitor-51监视程序和监视程序外部数据。

4.2 支持Monitor-51的MC8051核定制

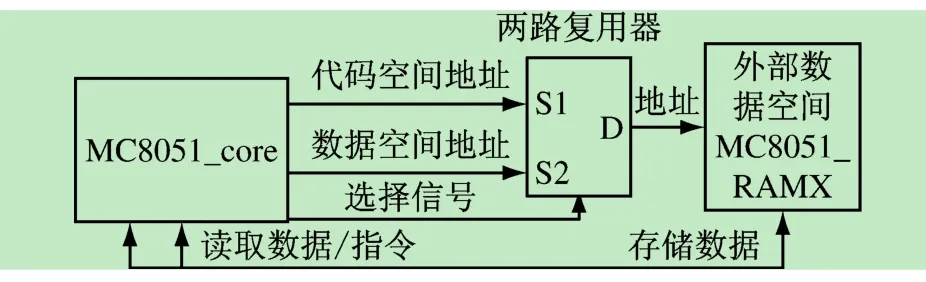

(1)定制冯·诺依曼存储结构。MC8051软核也采用哈佛存储结构。为使用Monitor-51,需要合并其代码空间与外部数据空间,定制成冯·诺依曼存储结构。具体来说,即是去掉图2中的MC8051_rom空间,只设一个代码和用户数据统一编址的可读可写的MC8051_ramx空间。但由于MC8051没有提供标准8051单片机的PSEN和RD信号,不能直接套用已有的合并方式。需要修改MC8051_core相关代码来定制。

通过分析MC8051的源代码得知,MC8051_core内部具有独立的代码空间地址总线和数据空间地址总线。定制的工作可归结为把MC8051_core内部总线与外部数据空间MC8051_ramx的地址总线和数据总线分别重新连接,形成和图3中等效的统一寻址效果。

为此,在MC8051_core外添加一个两路复用器,其输入端分别接代码空间地址总线信号rom_adr_o和外部数据空间地址总线信号adrx_o。复用器的选择信号由MC8051核中指示当前存储器访问类型(为代码空间访问或数据空间访问)的信号s_adrx_mux提供。这使得MC8051对代码空间或对数据空间各自的访问都实质上是对单一的MC8051_ramx块的访问。

而对于数据总线,这里只需将MC8051_ramx的数据线在保持与原内部数据总线连接的同时,也连接至代码空间访问的内部数据总线。这样,实际的传送操作将由MC8051_core对各指令译码来判断完成。定制MC8051核的电路原理如图5所示。

图5 定制MC8051的冯·诺依曼存储结构

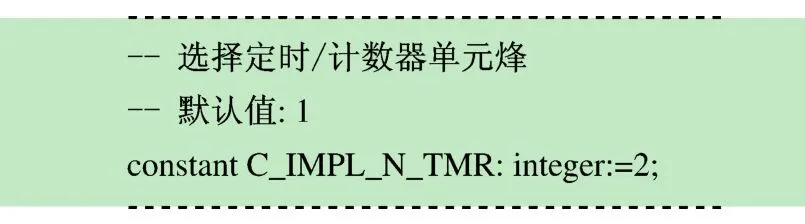

(2)增加定时器。串口将占用一个定时器作为其波特率发生器。为给用户提供完整的51单片机功能,修改mc8051_p.vhd文件中如图6的配置代码,可方便地补充一组定时器。

图6 设置定时器数量为2的代码

(3)修改复位向量。我们知道,Monitor-51工作方式下,单片机复位后需首先进入Monitor-51监控程序,这就要求把单片机标准的复位向量(零地址)修改为监控代码首地址:修改control_mem_rtl.vhd文件中pc< =conv_unsigned(0,16)为 pc< =conv_unsigned(10240,16),其中10240为监控代码的首地址。

4.3 可在线调试的MC8051核生成

以基于 Xilinx的 FPGA实验教学平台(采用Spartan3E系列芯片XC3S250-144)为例,给出可在线调试的MC8051核生成步骤如下:

(1)通过配置INSTALL.A51,添加定时器,设置监控串口波特率9600bps;执行INSTALL.BAT,设置监控程序首地址为0x2800,监控程序的外部数据空间首地址为0x3F00,并编译生成mon51.hex目标文件。

(2)为能加载mon51.hex文件,通过 HEX_BIN.exe和 CoeGenerator.exe将 mon51.hex文件转换为Xilinx FPGA中块RAM的初始化数据文件MON51.coe(两个小软件使用简单,不作赘述)。

(3)MC8051核中的内部MC8051_ram及MC8051_ramx采用FPGA的块RAM核实现。先建立ISE项目,再调用其IP核库的Block Memory Generator(内存块生成工具)来实现。其中MC8051_ramx生成时,以MON51.coe为其初始化数据文件。

(4)根据4.2小节,定制MC8051_core。

(5)根据实验板时钟,生成FPGA内的时钟模块(DCM)为MC8051核提供工作时钟为18 MHz。

(6)在一个ISE项目中,将生成的DCM模块、MC8051_ram、MC8051_ramx和 MC8051_core等部分,添加管脚约束ucf文件,进行综合和布局布线,最后生成包含MC8051核的FPGA配置文件(.bit文件)。

(7)用JTAG接口下载.bit文件到FPGA。

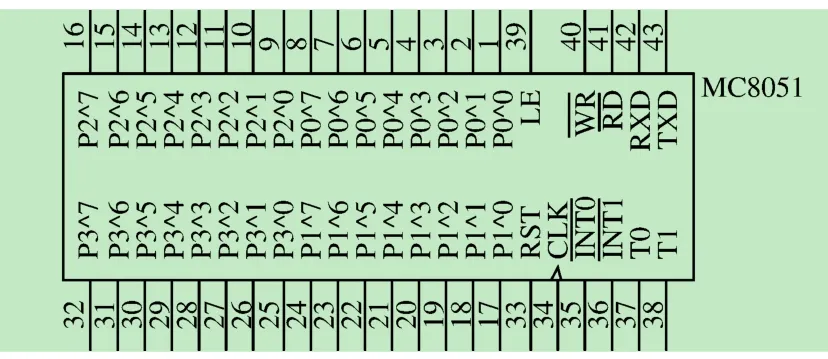

至此,该FPGA平台上建立了一个可在线调试8051单片机的程序。在实际的实验教学中,可进一步形成更加标准的引脚封装,如图7所示。这样,学生可方便地配合平台外设,开展各单片机实验项目。

图7 MC8051封装

4.4 在线调试应用举例

以MC8051单片机P0口驱动8个LED的流水灯实验为例。中间还设置了一个除法运算,验证18MHz主频下除法功能的正常运行。应用Keil μVision4对其在线调试的过程如下:

(1)μVision2设置。新建工程,在工程中可选择目标器件为标准8051单片机,如Atmel->89C51,再进行options设置。在其中的“Debug”栏中选用“Keil Monitor-51 Driver”,并设置串口“Baudrate”为9600。

(2)调试界面。在项目中创建C51源程序文件,成功编译后,点击工具条中图标进入调试界面。其中,单片机的内部寄存器、各局部变量和观察窗口中的变量都在线可见。所有程序修改和调试都只需PC端的操作,无需对FPGA及其中的51软核作重配置。

5 结语

本文提出基于Monitor-51和MC8051软核定制,实现在FPGA平台中在线调试单片机应用程序的方法。该方法有效解决了当前8051软核在单片机实验、EDA实验和SOPC实验等实践教学中运用的瓶颈问题,为三者的融合提供了可能,有力地支撑了本校电子技术综合实践教学的改革,也期望对其他高校的相关工作有所帮助。

[1]李 颖,习友宝.实验教学示范中心实验室运行机制与管理模式的探索与实践[J].实验室研究与探索,2009,28(4):88-90.

LI Yin,XI You-bao.Exploration and Practice on the Operational and Managerial Mode of Experimental Center[J]. Research and Exploration in Laboratory,2009,28(4):88-90.

[2]余 魅,习友宝.建设国家级实验教学示范中心构建创新人才培养平台[J].实验技术与管理,2006,23(12):10-11.

YU Mei,XI You-bao.Constructing a National Representative Center of Laboratory Education,and Building a Platform for Training Creative Students[J].Experimental Technology and Management,2006,23(12):10-11.

[3]陈学英.电子技术综合实验教学方法研究与实践[J].实验科学与技术,2011,9(2):127-130.

CHENG Xue-ying.Teaching Methods Research and Practice on Electronic Technique Comprehensive Experiments[J].Experiment Science and Technology,2011,9(2):127-130.

[4]刘京锐,袁惠梅,王 莹,等.MCU应用系统实验教学装置设计与实现[J].实验技术与管理,2010,27(8):71-74.

LIU Jing-rui,YUAN Hui-mei,WANG Ying,et al.The Projection and Achievement of Practical Teaching Devices of MCU Application System[J].Experimental Technology and Management,2010,27(8):71-74.

[5]宋蕴璞,周文泳,徐鸣谦,等.高校单片机教学实验设备与方式探讨[J].实验室研究与探索,2009,28(11):6-9.

SONG Yun-pu,ZHOU Wen-yong,XU Ming-qian,et al.Exploration on the Ways and Facilities of Single-Chip Computer Experiment in Universities[J].Research and Exploration in Laboratory,2009,28(11):6-9.

[6]万光毅,严义.单片机实验与实践教程[M].北京:北京航空航天大学出版社,2005:149-258.

[7]王 瑞,游志宇,杜 杨,等.MC8051单片机 IP核的FPGA实现与应用[J].电子设计工程,2009,17(1):57-60.

WANG Rui,YIU Zhi-yu,DU Yang,et al.FPGA Implementation and Application of MC8051 MCU IP Core[J].Electronic Design Engineering,2009,17(1):57-60.

[8]徐 慧,王金海,王 巍.基于FPGA的8051 IP核的设计与实现[J].计算机技术与发展,2009,19(3):42-45.

XU Hui,WANG Jin-hai,WANG Wei.Design and Implementation of 8051 IP Core Based on FPGA[J].Computer Technology and Development,2009,19(3):42-45.

[9]丁 昊,庄贵敏,宋 杰,等.基于MC8051内核的便携幅频特性测试仪设计[J].电子技术应用,2011,37(4):29-32.

DING Hao,ZHUANG Gui-min,SONG Jie.Design of Portable Frequency Characteristics Test Instrument Based on MC8051 IP Core[J].Application of Electronic Technique,2011,37(4):29-32.

[10]潘明方,李慧军.基于MC8051软核的星载智能1394终端[J].微计算机信息,2007,23(6):193-195.

PAN Min-fang,LI Hun-jun.On-board Intellectual 1394 Terminal Based on MC8051 IP[J].2007,23(6):193-195.Control&Automation,2007,23(6):193-195.

[11]罗侄敬.在嵌入FPGA的IP核8051上实现TCP/IP的设计[J].电子元器件应用,2007,9(4):44-46.LUO Zhi-jing.Implementation of TCP/IP for 8051 core in FPGA[J].Electonic Component& Device Applications,2007,9(4):44-46.

[12]尹 勇.μVision2单片机应用程序开发指南[M].北京:科学出版社,2005.3,300-306.

[13]陈明义,李 彬.串行通信接口实现MC8051软核在线编程[J].电子科技,2009,22(6):29-32.

CHEN Ming-yi,LI Bin.Implementation of MC8051 Soft-core Insystem Programming Using the Serial Communications Interface[J].Electronic Science and Technology,2009,22(6):29-32.

[14]MC8051 IP CoreUserGuide [EB/OL]. http://www.oreganosystems.at/?page_id=96.[2012-7-1].

[15]高 昀.EDA技术在教学实践中的研究与应用[D].成都:电子科技大学,2009.

[16]陈兴文,刘 燕.基于KEIL 51的单片机开发系统设计[J].微计算机信息,2005,21(5):112-113.

CHEN Xing-wen,LIU Yan The Design of MCU Development System Based on KEIL 51[J].Control& Automation,2005,21(5):112-113.