UHF RFID读写器控制模块的SOPC设计

李 鸿

(湘潭职业技术学院,湖南湘潭411102)

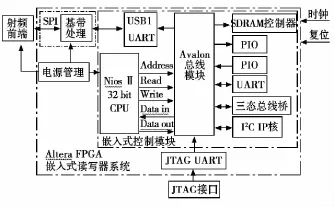

一般来说,UHF RFID读写器包括控制模块、基带处理模块、射频前端、电源、天线及外围接口电路等[1],如图1所示。控制模块是读写器系统正常工作的控制、协调中心,包括微处理器、存储系统、对外通信接口以及用于显示/操作的屏幕/键盘等,通过与后端应用系统之间的通信,执行应用系统发来的或键盘输入的动作指令,对基带处理模块、射频前端的工作状态、数据处理及外部设备(如键盘、显示器等)加以协调控制,执行防碰撞算法,实现多标签无漏识别。控制模块通常采用单片机、DSP、ARM等微处理器结合相应的软件来实现,要求微处理器具有强大的数据实时处理能力,比较高的稳定性和相对低的功耗,丰富的片内外设和I/O设备端口,方便高效的开发环境等[2]。本控制模块采用NiosⅡ嵌入式软核处理器来实现,不仅能满足上述对微处理器的要求,同时成本低,灵活性高,升级容易,外围电路简单,系统更小型化。

图1 读写器基本结构

1 控制模块的SOPC设计

SOPC是基于FPGA可编程SOC,它将处理器、存储器、I/O接口等系统设计所需要的功能模块集成到一片FPGA上,完成整个系统的主要逻辑功能,具有设计灵活,可裁减、可扩充、可升级及软、硬件在系统可编程的特性[3]。NiosⅡ处理器是用户可配置的通用32位RISC软核微处理器,是基于通用FPGA架构的软CPU内核,与外部大容量存储器结合,可构成功能强大的32位嵌入式处理器系统,与用户自定义逻辑结合可构成基于FPGA的片上系统[4]。基于NiosⅡ的SOPC系统设计首先要根据系统要求确定功能模块,然后分别进行硬件设计和软件设计[5],本文主要对控制模块NiosⅡ嵌入式软核处理器系统、通信接口进行设计。

1.1 控制模块硬件设计

1.1.1 控制模块硬件结构

控制模块由NiosⅡ处理器系统来实现,包括与CPU相连接的片内外设和存储器以及与片外存储器和外设相连的接口,采用SOPC设计理念,将NiosⅡ处理器嵌入到FPGA芯片EP2C8Q208C8中,实现所需控制信号的产生和传输,完成协议解析、时序控制、状态转换及防碰撞,包括完成与上位机的通信,根据通信协议要求接收、发送指令,将读写状态通过LCD显示等。如图2所示。

图2 UHF RFID读写器嵌入式控制模块结构图

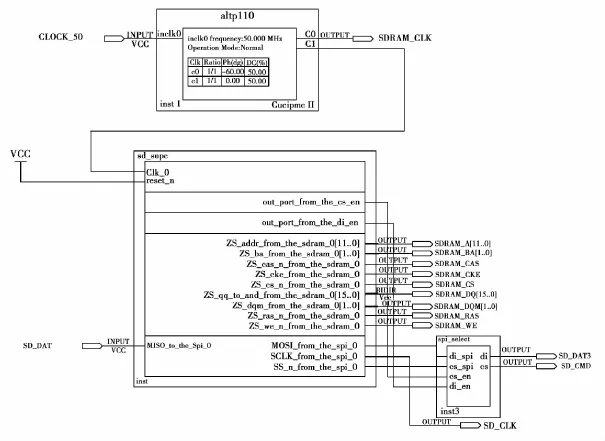

1.1.2 控制模块的硬件设计

NiosⅡ嵌入式处理器系统包括NiosⅡ处理器(含JTAG调试模块)、Avalon交换结构总线和外围设备(存储、接口及功能模块)等,均由FPGA内部的逻辑单元和RAM资源来实现。

根据系统功能确定系统组件。打开QuartusⅡ9.0软件,建立新工程,选择目标板CycloneⅡEP2C8Q208C8,建立顶层设计文件。启动SOPC builder工具软件,输入新系统名称,添加NiosⅡCPU核,选择 NiosⅡ/s型,主频50MHz,为整个硬件平台的控制核心。添加片内RAM、JTAG UART IP、PIO(实现对外围通用 I/O口的控制)、UART(通用串行收发器)、LCD和DIP IP(DIP用于模拟键盘输入)、控制与Ethernet PHY&MAC芯片通信的 Ethernet Interface等;添加SDRAM控制器IP、CFI接口IP(FLASH接口组件)及Avalon Tristate Bridge,根据访问要求分配组件地址空间、数据宽度与中断优先级;添加锁相环组件PLL,设定固定偏移相位。最后,通过Avalon总线通过端口完成各IP组件之间的互连,通过指定时序,部件之间就可以进行通讯了。控制模块设计硬件系统整体连接如图3所示。

图3 控制模块顶层硬件设计图

利用QuartusⅡ9.0对以上硬件系统进行编译,将.sof文件下载到FPGA芯片中,系统每次上电,便可对FPGA进行配置。

1.2 控制模块通信接口电路设计

接口设计主要涉及控制模块与基带处理模块、上位机间的接口设计。为提高系统可靠性和适应性,控制模块与上位机系统之间采用USB接口、RS232接口以及RJ45三种通信接口,实现嵌入式控制模块与PC的通信,采用USB HOST接口来实现控制模块对基带处理模块的控制。

1.2.1 控制模块与上位机系统接口设计

1)RS232串口电路

RS232是应用最为广泛的UART接口,可以方便地实现与计算机的数据通信。选取EP1C12Q240C8的任意四个引脚与电平转换器MAX3232CSE相连。通过MAX3232CSE接标准串行接口DB9,即可与PC机进行串口通信。

2)USB接口电路

考虑到操作的简洁性,选择国产USB接口芯片CH375。CH375内置有标准的USB通讯协议,用户无需编写驱动程序,具有8位数据总线和地址读、写、片选控制线及中断输出,可方便地挂接到 NiosⅡ嵌入式处理器系统总线上[6]。CH375所需外围电路十分简单,只需要一个晶振和两个电容,芯片的D+、D-引脚可直接与计算机USB接口的D+、D-信号线相连。USB接口电路框图如图4所示。

3)以太网接口电路

NiosⅡ开发系统中提供了LAN91C111网络芯片的控制逻辑,因此PHY/MAC芯片选LAN91C111,接口采用RJ45标准以太网接口,接口变压器选用 H1102芯片,NiosⅡ通过Avalon总线以及三态桥上的以太网控制逻辑控制以太网口的数据收发。原理框图如图5所示。

图4 USB接口电路框图

图5 以太网接口硬件原理框图

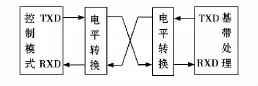

1.2.2 控制模块与基带处理模块的通信接口

控制模块与基带处理模块的通信接口采用UART(通用异步收发器)接口,是一种短距离串行传输接口,通信成本低,抗干扰性强,使用广泛。接口框图如图6所示。

在FPGA中用Verilog实现了 UART模块[7],主要完成RS232电平到TTL/CMOS电平的转换,对接收数据的串并转换,实现串口通信。在QuartusⅡ中,生成的UART通信接口模块如图7所示。

图6 UART接口组成框图

图7 UART通信接口模块图

1.3 控制模块软件设计

软件设计采用NiosⅡIDE基于μC/OS-Ⅱ多任务实时操作系统实现。NiosⅡIDE是NiosⅡ系列嵌入式处理器的基本开发工具,可完成整个软件工程的编辑、编译、运行管理、调试和下载等过程[8]。NiosⅡIDE包含uC/OS-Ⅱ实时操作系统,通过μC/OS-Ⅱ可实现控制模块的收发控制、防碰撞算法和防冲突协议,驱动并管理外围接口,对应用软件进行任务调度。

1.3.1 控制模块主控程序设计

控制模块主控程序就是NiosⅡ处理器内存放的一段C语言控制程序,它通过数据总线控制基带处理模块、射频收发模块的工作状态以及与上位机应用程序通信,包括完成NiosⅡ处理器及其相应外围模块接口所需的初始化,配置控制模块和FPGA、开中断、启动PLL、设定发射功率和接收比较电平、发送寻标签命令、防冲突处理、读标签命令、处理接收信息、控制发射功率的大小,与计算机进行通信等[9]。主控软件设计流程如图8所示。

图8 读写器主控软件设计流程图

1.3.2 基于NiosⅡIDE的软件设计

打开NiosⅡIDE工具软件,创建并运行一个新的NiosⅡIDE工程,根据程序流程图编写C语言用户应用程序,并添加到新工程中。uC/OS-Ⅱ多任务实时操作系统提供了任务创建和消息队列创建、处理函数,通过这些函数可以很方便地创建多个任务,并通过消息队列完成任务间通信[5]。用户应用程序添加完毕后编译整个工程,将编译生成的文件下载到FPGA进行软件程序调试。

2 结束语

本文完成了基于NiosⅡ处理器的UHF RFID读写器控制模块的SOPC设计及与控制模块相关的通信接口设计,实现了所需控制信号的产生和传输、协议解析、时序控制、状态转换及防碰撞等功能。与传统方法相比,该方法在降低控制模块设计复杂性、缩短开发周期、降低开发成本、保证系统可靠性等方面具有明显优势,基于NiosⅡ处理器结合相应软件实现的控制模块具有强大的实时控制能力、较高的稳定性,功耗更低,外围电路更简单,系统更小型化。

[1]张江波.基于NIOSⅡ的RFID读写器设计[D].郑州:郑州大学,2011.4.

[2]赵明全,杜军梅,梁飞宇,等.UHF RFID系统的读写器设计[J].现代仪器,2012,18(6):48 -50,58.

[3]康文轩,李斌,屈巍,等.基于NIOSⅡ的嵌入式网络接口设计[J].电脑开发与应用,2007,20(2):27 -28.

[4]马赛.基于SOPC的无刷直流电机控制器应用研究[D].重庆:重庆大学,2012.4.

[5]孟芳,于立佳,张文志.基于NiosⅡ的SOPC系统设计分析[J].无线电通信技术,2012,38(1):73 -76.

[6]杨全玖,张大伟,吕宗芳,等.基于CH375多通道USB接口与PC机通信的实现[J].微计算机信息,2006(32):80-82,105.

[7]王衍良.基于FPGA的超高频RFID读写器设计与实现[D].广州:广东工业大学,2011.5.

[8]王康佳.基于NiosⅡ嵌入式的温度传感器的设计与实现[J].河北北方学院学报(自然科学版),2011,27(2):44-47.

[9]王晓华,周晓光,孙百生.超高频射频识别读写器设计[J].电子测量技术,2007,30(2):158 -161.