某输出缓冲器的失效分析

蒲 林,高兴国,白 璐

(中国电子科技集团第24研究所,重庆 400060)

某输出缓冲器的失效分析

蒲 林,高兴国,白 璐

(中国电子科技集团第24研究所,重庆 400060)

本文通过对某输出缓冲器在质量一致性检验中的ESD考核环节失效的情况进行分析,找到了产品测试系统的异常情况,通过此次分析,进一步发现该产品的ESD保护设计一直以来存在的问题。文中不仅给出了失效机理,同时提出了改进措施并加以验证。此次失效分析对于同类器件的ESD保护设计,提高其可靠性具有一定的借鉴意义。

输出缓冲器;ESD;静电;失效分析

概述

近些年来,关于电子元器件的失效分析已逐渐发展成为一个专门的学科。作为模拟集成电路设计、生产单位,如何在分析仪器、设备有限的条件下,通过失效分析发现产品设计、测试、生产制造过程中存在的问题,以不断改进产品的设计水平和制造工艺,提高产品的可靠性。由于单片模拟集成电路,器件尺寸较小,因此难度较大。

某单位自行设计并生产的某型输出缓冲器是于2009年设计定型的老产品项目,从09年产品定型至今,其生产技术状态一直较为稳定,产品生产、测试成品率较高,自定型以来该产品在历次鉴定检验和质量一致性检验过程中均未发生过失效。

2011年9 月,某批次该型输出缓冲器在投入进行质量一致性检验的ESD考核试验后测试发现静态电流超出该产品详细规范中该电参数范围,即参数超差,被判为ESD考核失效。由于该产品从未发生过技术状态更改,而此前的批次在ESD考核时均未发生过类似现象,此次失效较为异常,因此对此次失效进行了较为详细的分析。

1 失效原因分析

此次异常的某输出缓冲器是多年前设计定型的老产品,从设计定型至今从未发生过技术状态更改,而同批芯片此前封装为成品进行的所有检验项目(含ESD考核试验项目)都未发生过失效,因此怀疑是测试系统出现异常,故对此次ESD考核试验后的电路使用的测试系统进行排查。

经询问生产线上测试人员,此次考核后的ESD试验电路测试时,由于测试系统在芯片测试间测试芯片(注:芯片与成品可使用同一测试盒,区别仅在于测试时使用的夹具不同),因此临时搭建了一个新的测试系统进行测试,即此次失效采用的测试系统与此前生产批产品采用的测试系统不同。

1.1 使用新测试系统对几种电路进行对比测试

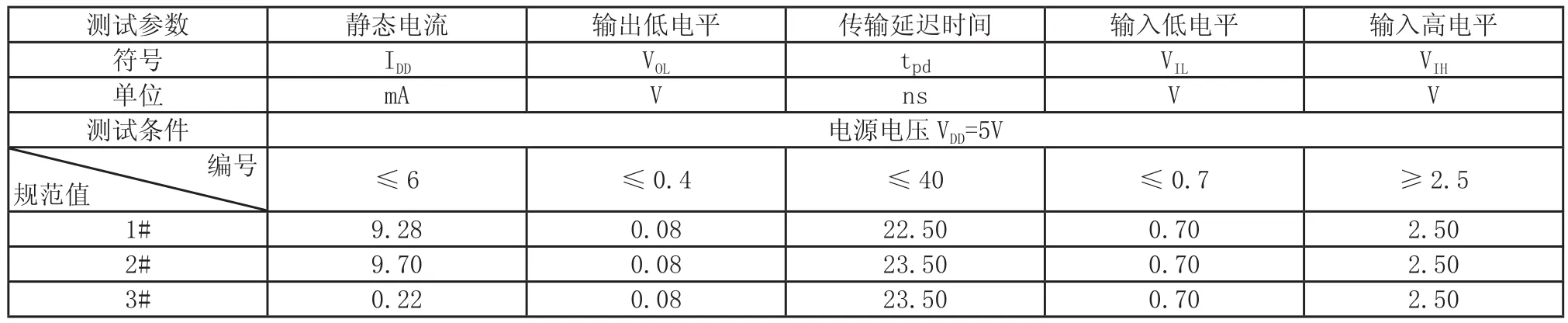

选择本次ESD考核失效电路(记为1#)、此前某批次ESD考核合格电路(记为2#)、及与此次考核同批次但未投入ESD试验的电路(记为3#)按照产品详细规范,使用新测试系统进行对比测试,测试结果如表1所示。

从对比测试结果可以看出:本次ESD考核失效电路(1#)、此前某批次ESD考核合格电路(2#)采用新测试系统测试,静态电流均超标,而未投入进行ESD试验的电路静态电流正常,说明ESD试验后电路确实存在损伤;而此前的某批次ESD考核合格电路(3#)采用新测试系统测试结果与其当时考核后测试结果不同,说明新测试系统与原测试系统存在差异。

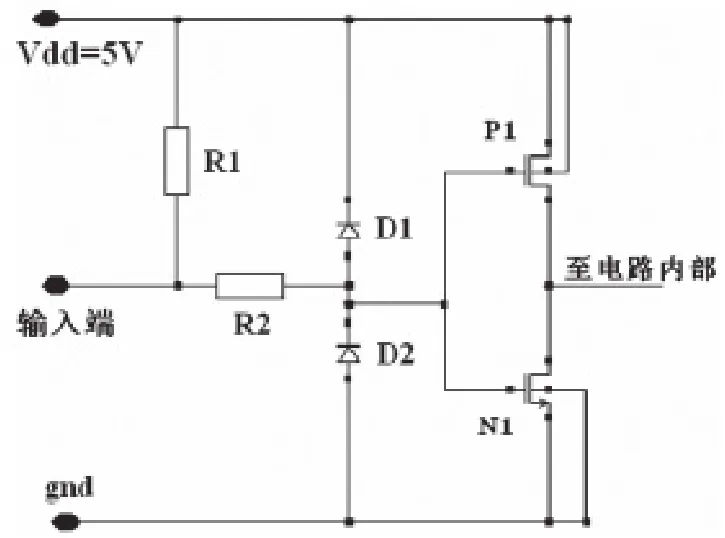

1.2 新、老测试系统对比

仔细检查该输出缓冲器的原(老)测试系统。原(老)测试系统在设计时由于认知不足,仅仅考虑到用户使用过程中,输出端通过1kΩ电阻与电源相连,因此为真实模拟用户实际使用情况,该缓冲器产品详细规范中IDD测试原理图如图1所示。而从图1中可以看出,输出端通过1kΩ电阻与5V电源端的电流表相连,输入端接5V保证了输出端1kΩ电阻几乎不会有 电流通过,保证负载电流不会影响静态电源电流的测试。而在图1所示测试条件下,未测试输入为低电平(即输入为0V)时的静态电流。

表1 电参数测试结果

将表1中的430#、835#、503#三只电路采用如图1所示的原测试系统进行测试,测试结果分别为0.38mA、0.45 mA、0.22 mA,均满足详细规范要求。也就是说,此次ESD考核异常的电路如果采用原测试系统测试,则满足详细规范要求,即判电路合格。

再仔细查看此次为测试ESD考核试验电路开发的新测试系统,该测试系统在测试静态电流时输入电压分别为0V(低电平)和5V(高电平),对两种情况下的电源电流测试结果进行对比,选择最大值作为最终输出结果。用新测试台对3只电路再次进行测试,结果3只电路在输入0V时电源电流分别为9.28mA、9.70mA、0.22mA,测试结果与表1一致。说明原测试系统存在设计不完善的问题。

1.3 小结

通过上述对比分析,可以发现,该输出缓冲器在ESD试验后其实一直存在静态电流超标的情况,而此前的测试系统在设计时未测试输入为低电平(即输入为0V)时的电源电流,因此一直未发现该产品ESD失效的问题。

图1 IDD测试电路原理图

2 ESD损伤情况分析

该缓冲器输入级原理图如图2所示。

该缓冲器输入端通过上拉电阻R1接到电源,当输入悬空时默认输入为高电平;R2、D1、D2为静电保护电路,为电路内部器件提供静电泄放通路。

根据表1所示测试结果,除电源电流外,电路其他参数均正常。如果电路内部及输出级存在损伤,那么输出低电平、传输延迟时间测试结果均会发生异常,因此可以判断ESD试验后电路输入级发生损伤。根据图2所示输入级电原理图,N1/P1为输入级反相器,如果这两个MOS管发生损伤,那么电路将无法接收外界信号、造成电路功能异常;而表1测试显示电路功能正常,仅静态电流超标。因此可以判断ESD损伤部位为R1、R2、D1或D2。

对3只电路进一步测试分析,输入端分别接0V和5V,测试输入端通过的电流。正常情况下,输入接5V时,R1两端压差为0,D1/D2均反相截止,此时输入端电流为0;输入接0V时,D1/D2均反相截止,R1两端压差为5V,R1阻值正常为100kΩ,因此输入端电流为0.05mA。实际测试时,输入为5V时,3只电路输入端电流均为0,说明静电后D2仍然处于反相截止的高阻状态;输入为0V时,3只电路输入端电流分别为9.01mA、9.35mA、0.06mA,因此可以进一步确定该输出缓冲器ESD损伤位于R1、R2、D1。

当电路进行ESD试验时,外界静电冲击从输入端引入器件内部,通过输入级R1、R2、D1或D2进行静电泄放,当静电冲击能量大于器件能够承受的范围时,R1、R2或D1发生损伤,导致输入端对电源阻抗下降,从而引起ESD试验后产品静态电流超标。

图2 某缓冲器输入级原理图

3 改进设计

ESD保护电路是集成电路芯片上专门用来做静电放电防护用的特殊电路,该保护电路提供ESD电流泄放路径,以避免在 ESD发生时静电电流流入集成电路内部而造成芯片损伤。

通常ESD保护电路设计时有两个基本原则:其一,为每一个I/O PAD缓冲区到邻近的键合点以及到电源网络(GND或VDD)提供一个良好的、均匀的、快速的大电流分流通道,该保护电路瞬间可通过大的电流,如安培量级的电流,且保护电路自身可以恢复不能被烧坏;其二,在需要保护的器件附近提供一个限流电路与电压箝位电路,以阻止高压进入器件使栅极和元件遭到破坏。

该缓冲器的输入级进行了全面的ESD保护设计,图1中D1/D2用于实现原理一的功能,主要实现静电泄放的功能;电阻R2用于实现原理二的功能,以限流电阻的形式阻止电路内部N1/P1栅极承受过高电压,保护MOS管栅极。

图3 输入级版图

此外,ESD 结构应该具有低阻抗的电流通道,即ESD 防护电路应该尽量靠近键合点。当外界静电冲击电路时,与内部线路相比,ESD防护电路应该具有更低的阻抗,这样外界静电冲击能量才会经过ESD保护电路进行泄放。本次失效电路输入级部分版图如图3所示。根据图3可知,其中R1为Pwell井电阻,该器件存在一个寄生二极管,其中二极管P极为电阻的Pwell部分,二极管N极为芯片N型衬底,N型衬底与电源Vdd相连。因此,当输入级收到外界对电源的静电冲击时,键合点内部存在两条静电泄放通路,一条为通过R1寄生二极管到电源Vdd,一条为通过R2相比静电泄放器件D1/D2到电源。两条泄放通路相比,上拉电阻通路阻抗相对更低,因此,此时静电冲击将主要通过R1的寄生二极管进行泄放。R1面积较小,静电泄放能力不高,在静电冲击过程中容易发生损伤,导致R1对电源有效阻值下降,引起静态电流超标。

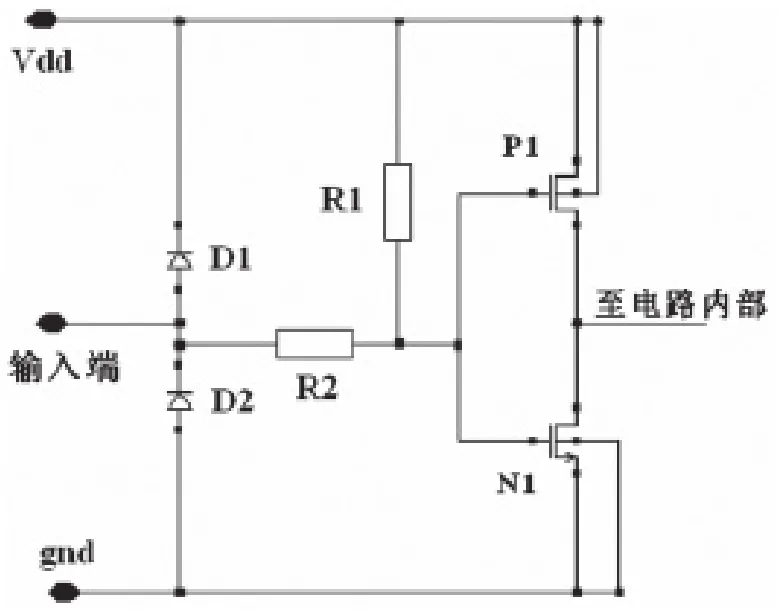

根据以上分析,我们对输入级线路及版图进行改进,改进后线路及版图如图4、图5所示。

对改进后电路进行重新流片验证,更改后电路常规电参数与更改前一致,但ESD试验后按照新测试台测试条件进行测试,静态电流与ESD试验前一致,没有再出现静态电流超标的情况,说明器件没有发生静电损伤,前期失效分析结论得到验证,更改方案有效。

图4 改进后输入级原理图

图5 改进后输入级版图

4 结论

此次通过一款老产品在ESD试验后测试的异常现象的失效分析,发现了原开发的测试系统一直存在的缺陷,该产品的ESD保护设计并不合理。通过此次分析,不仅改进了测试系统,同时对该产品的ESD保护设计进行了改进,经重新流片生产、测试验证,改进后的产品未再次发生同类异常现象,对后续同类产品的测试开发、ESD保护设计具有一定的借鉴意义。

[1] 郑廷圭,刘发,半导体器件失效机理及分析方法 [R].机械电子工业部第五研究所,1990,12.

[2] 刘恩科,朱秉升,罗晋生. 半导体物理学 [M].北京:电子工业出版社,2007.

[3] 陈星弼,张庆中,陈勇. 微电子器件 [M]. 北京:电子工业出版社,2011.

[4] (美)沃尔德曼. ESD电路与器件 [M]. 北京:电子工业出版社,2008.

蒲 林,中国电子科技集团第24研究所,第二事业部副部长,工程师,研究方向:IC设计、测试开发。

高兴国,中国电子科技集团第24研究所,第二事业部,工程师,研究方向:从事IC设计工作。

白 璐,中国电子科技集团第24研究所,第二事业部,高工,研究方向:从事电子元器件方面的失效分析以及IC可靠性设计工作。

The Failure Analysis on A Type of Output-Buffer

PU Lin,GAO Xing-guo,BAI Lu

(No.24 Research Institute of CETC, Chongqing 400060)

This paper is about the analysis of a type of output-buffer which is failure on ESD test of QCI. Through failure analysis, not only the abnormal condition that existing in the testing system but also the defect of ESD protect circuit design are found. The paper presents the failure mechanism, and gives the suggestions on the design of ESD protect circuit. The conclusions are instructive for the further improvement of reliability for the similar products.

output-buffer;ESD (electro-static discharge);static electricity;failure analysis

TN306

A

1004-7204(2014)01-0019-04