基于TD-LTE终端的连续时间ΣΔ ADC的设计*

黄 沫,陈弟虎,叶 晖,徐 肯,郭建平

(1.中山大学理工学院,广东 广州 510275 2.广州市广晟微电子有限公司,广东 广州 510006 3.广东顺德中山大学卡内基梅隆大学国际联合研究院,广东 佛山 528300)

然而,越来越多的报导显示,LTE智能机终端耗电非常惊人[2-5]。因此,未来很长一段时间内,TD-LTE终端都将以数据卡的形式出现(数据卡以USB供电,对功耗不敏感);而TD-LTE其功耗要达到目前3G手机的水平,则要到2014年下半年后。当然,终端功耗过大是个多方面的问题,涉及到通信系统、射频芯片的功耗、基带算法的复杂程度等方面。

本论文着力于解决TD-LTE终端射频芯片功耗的问题,基于0.13-μm CMOS工艺设计了一款低功耗TD-LTE射频终端芯片使用的连续时间ΣΔ ADC(CTDSM)。

1 系统设计

从文献[6-7]可知,传统接收机架构中(如图1(a)所示)的低通滤波器(LPF)功耗非常大。对于TD-LTE这种需要支持IQ正交混频和MIMO,也即是需要四个传统的LPF,功耗更大。若能省去(如图1(b)所示),必将有效降低TD-LTE终端射频芯片的功耗。

图1 (a) 传统接收机架构(b) 省去LPF的接收机结构

LPF在传统接收机架构中起两方面的作用:抗混叠滤波,以及抑制邻道干扰。若想省去LPF,则需要在系统架构上做相应的调整。出于此考虑,本文采用连续时间ΣΔ ADC。离散时间和连续时间ΣΔ ADC的结构如图2所示。可以看出,二者最大的区别在于离散时间ΣΔ ADC(DTDSM)是先采样,后进行环路滤波H(z);而对于CTDSM,是先经过环路滤波H(s),后进行采样。因此,采用CTDSM,利用其环路滤波H(s)的抗混叠滤波器效果,可以省去LPF。此外,从文献[8]的综述可以看出,CTDSM已经普遍可以达到10~12ENOB,10~100 Ms/s的水平,非常适合于TD-LTE这种高精度、中等带宽系统的应用。

对于省去LPF后邻道选择性的问题,本文采用的如文献[9]的方法,降低ADC前级电路的增益以满足要求。ADC动态范围的指标也由文献[9]得到:对于20 MHz信道带宽的情况下,所需动态范围为64.4 dB,其它带宽可以此类推。

图2 (a) DTDSM结构示意图 (b) CTDSM结构示意图

2 连续时间ΣΔ ADC的设计

2.1 过采样率(OSR)的选择

由ΣΔ的原理可知,对ΣΔ ADC过采样使量化噪声的功率分布在更宽的频带内,减少信道频带内的噪声;OSR率越高,带内噪声功率越小。但更高OSR必将导致电路工作更快,功耗急剧增加。在本论文采用的0.13-μm CMOS工艺下,电路采样速度的上限为500 MHz左右,而最宽的信道带宽为TD-LTE的20 MHz(30.72 Ms/s的转换率),因此最高不能超过16倍采样率,OSR不能超过8。

TD-LTE需要支持五种带宽,如果每种带宽都用一套单独的电路来实现,芯片面积将非常大,因此在此必须考虑设计复用。如表1所示,CTDSM将采用两套系数(10 MHz带宽以下的用Slow Mode系数,其他的用Fast Mode系数),OSR根据带宽不同发生改变(最宽带宽下的OSR不能超过8)。同时,为了保证输出接口速率符合系统定义的要求,ADC后级CIC滤波器的抽取系数、降频系数M都将相应的改变。

抽象美术于20世纪初产生于国外,在中国传统绘画中没有与之对应的作品。而中国的草书,则可以看作是一种抽象的艺术。

表1 ADC及后级参数设置

2.2 环路滤波器结构设计

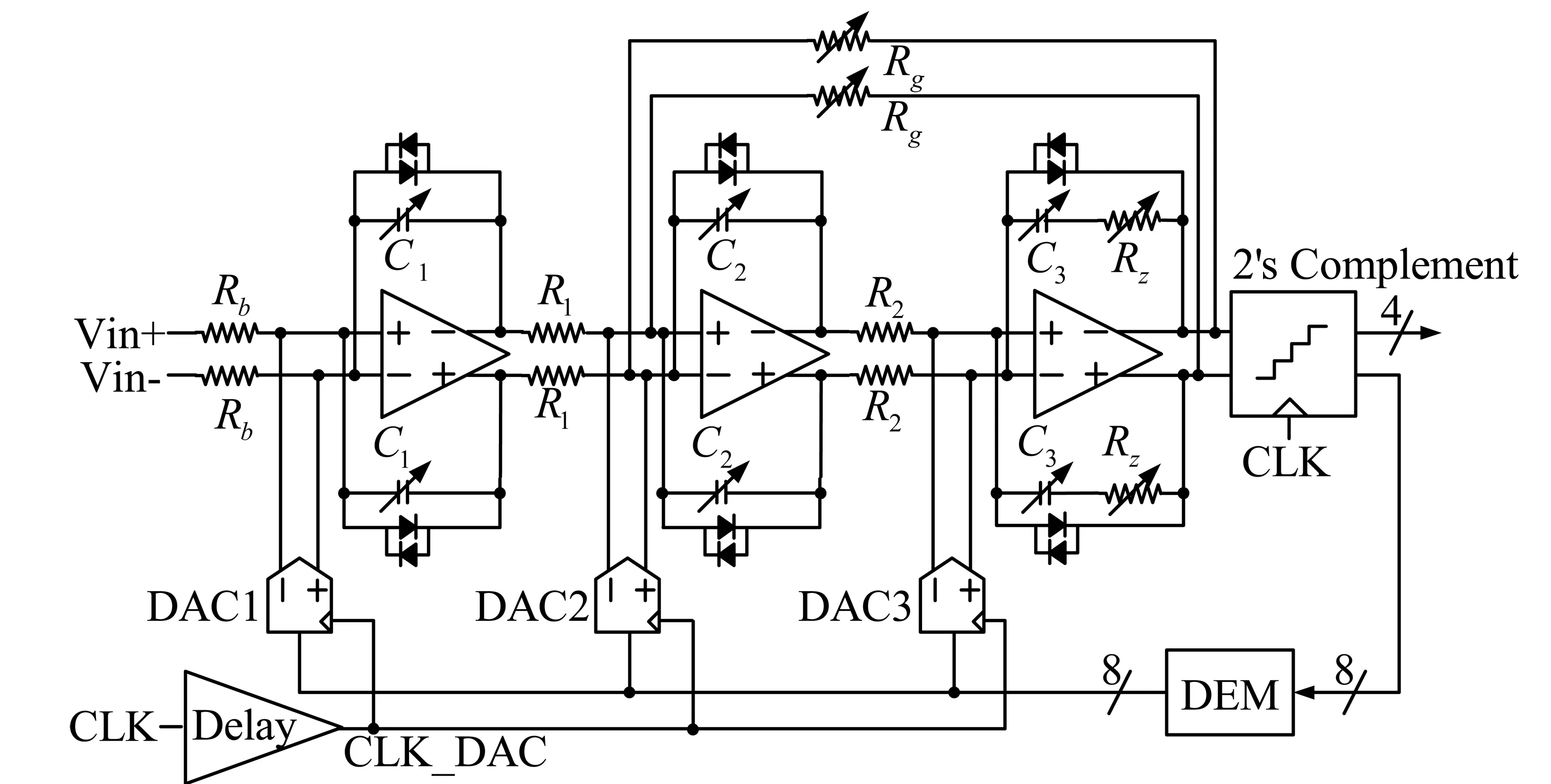

本文CTDSM的原理图如图3所示。为减小时钟抖动(clock jitter)对ADC的影响,ADC采用了3位量化的量化器,并采用了非归零码(NRZ)反馈波形的DAC。为了提高ADC的线性度,量化器量化后的数据将经由动态元素匹配(DEM)模块处理后输出。

单环和级联结构(MASH)是ΣΔ ADC中最常用的两种环路滤波器结构。较MASH结构,单环结构不需要数字和模拟部分的系数精确匹配来有效的抵消量化噪声,因此更适合连续时间ADC。而当单环环路滤波器超过了三阶时,较大的输入信号将使积分器出现过载,导致整个ADC系统的不稳定。综合考虑,本文将采用3阶环路滤波器的架构。为获得更好的抗混叠能力,本文采用了CIFB(Cascade of Integrators in FeedBack)环路结构。为了有效抑制量化噪声,环路滤波器采用切比雪夫(Chebyshev)II型滤波器,反馈电阻Rg为噪声传递函数(NTF)提供一个复数极点对,以保证在需要的带宽内信噪比(SNR)最大化。

图3 CTDSM的原理图

本文选用matlab中的cheby2函数来进行环路滤波器传输函数的设计,其代码如下:

[a,b]=cheby2(Order,AstopNTF,endBB*2*pi,′high′,′s′);NTF=tf(a,b);

图4 (a) Fast Mode和Slow Mode的NTF和STF (b) ELD补偿对STF带外尖峰的衰减

以Fast Mode为例,Order=3(3阶环路滤波器),AstopNTF = 45(阻带衰减45 dB),endBB=10e6*1.05(截止频率10 MHz,5%的带宽余量),‘high’的含义是高通滤波器,‘s’代表是模拟滤波器的设计。Slow Mode的传输函数也可以相应得到。图4(a)画出了Matlab仿真下Fast Mode和Slow Mode的信号传输函数STF和NTF。

2.3 ELD补偿

ELD即多余环路延迟(excess loop delay),定义为理想和真实反馈DAC脉冲之间的固定延时。如文献[10]所述,ELD使DAC的反馈脉冲延迟至下一采样周期,恶化了ADC的稳定性和SNR,因此需要对其进行补偿。学术界对ELD的补偿方法已有较多的论述[10-14]。本文采用文献[9]的方法,在环路传输函数分子加入一个零点外,起到直接反馈的作用,以抵消ELD的影响。上述的ELD补偿方法实现起来非常简单,只需要在第三级积分器上加入一个消零电阻Rz(如图3所示)。

经过ELD补偿的传输函数由Matlab计算,其代码如下:

fz = 1/(ELD*(360/45));

wz=fz*2*pi;

compen = tf([1 wz],[wz]);

L1p = OL * compen;

其中OL为上文所述未经补偿的开环传输函数,L1p为经过开环补偿的传输函数。用Matlab仿真得到STF带外尖峰如图4(b)所示。可以看出,ELD补偿有效的降低NTF带外尖峰11 dB,提高了系统的稳定性。

2.4 环路参数设计

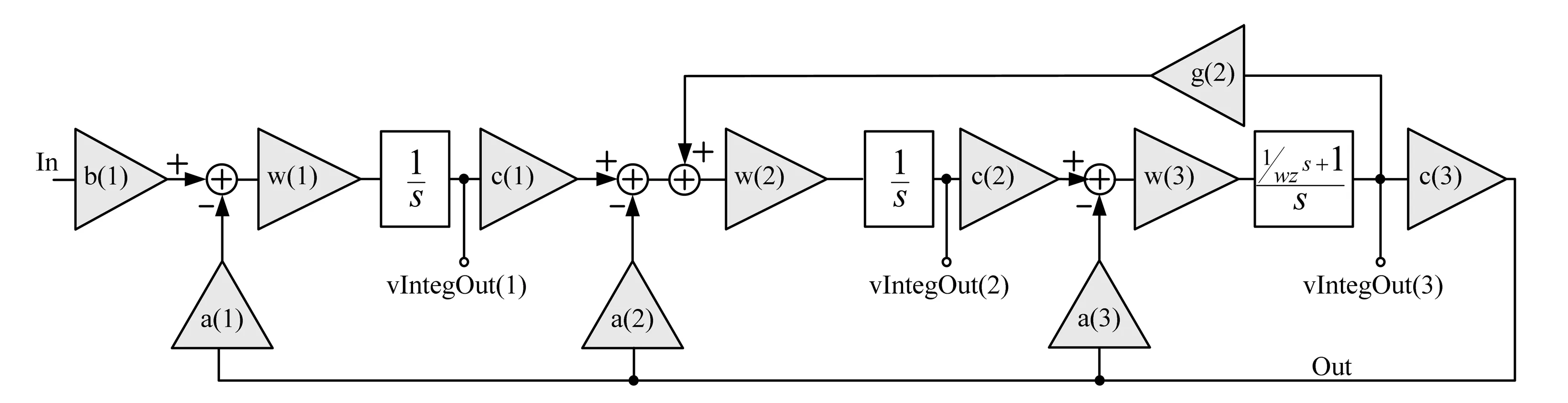

图5显示了CTDSM等效的模型,其中数组a<3∶1>等于DAC的电流,参数b为前馈电阻Rb的倒数,数组c<2∶1>为积分器电阻

图5 CTDSM的等效模型

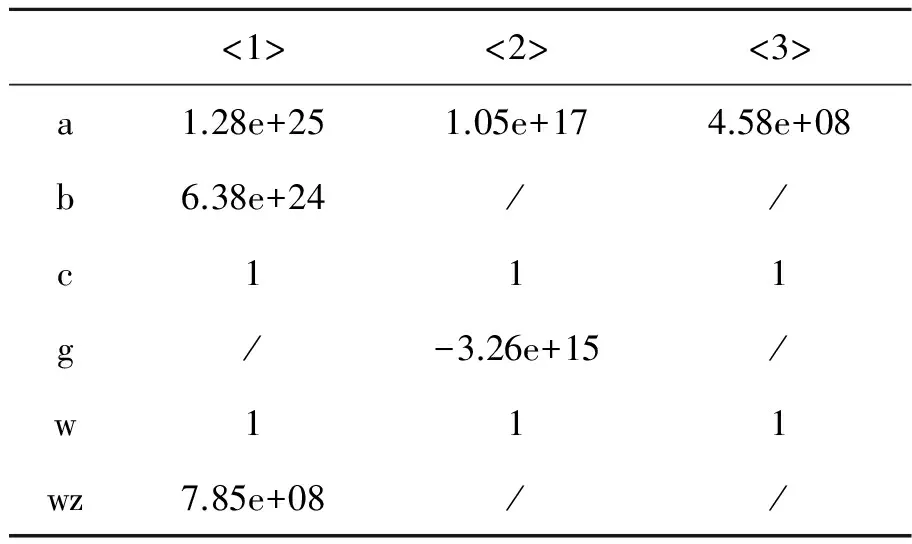

根据经过ELD补偿后的NTF和STF,先假定c和w全为1,可以得出图5中的各参数如表2所示。当然上述假定其中存在着各种不合理性(如ADC各级积分器输出摆幅过小、或超过限定范围,DAC的实际反馈电流达不到计算值,硅片上的电容达不到计算值,等)。采用Matlab的仿真工具Simulink,在输入加入满量程(0 dBFS)的正弦波信号,得到各级积分器输出的仿真结果如图6(a)所示。第一、二级积分器输出都异常大,显然都不是最优值,需要调整。调整的目标是每个DAC的反馈电流为320μA(考虑到功耗),积分器中电阻值在10 kΩ的数量级内(考虑到硅片实现的可靠性),并考虑到ADC采用0.13-μm工艺(电源电压1.3 V),各级输出的最大摆幅都控制在1 V以下(即差分2 V)更有利于实现。

表2 环路参数的实现(未经优化)

表3 环路参数优化关系

图6 (a) 优化参数前各级积分器输出波形;(b) 优化参数后各级积分器输出波形

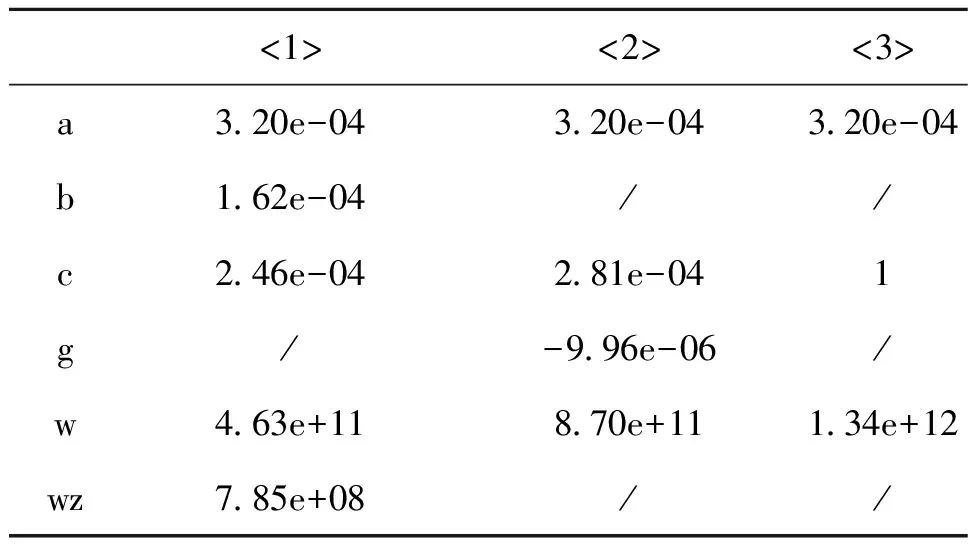

优化后的参数如表4所示。将其代入Simulink模型,仿真出来的各级积分器输出幅度均为2 V(如图6(b)所示),且DAC电流、电容电阻值均合理,证明达到了预期效果。

表4 环路参数的实现(经优化)

2.5 电路设计

CTDSM中的运算放大器需要有足够的直流增益(通常是60 dB),以及400 MHz的增益带宽积(GBW)以减小相移。为降低功耗,本文采用带前馈Gm-C补偿的4级运算放大器(如图7(a)所示)代替传统Miller补偿的二级运算放大器。该结构放大器能够取得更大的信号带内增益和更好的带内线性度:图7(b)显示了对其仿真的波特图,静态电流为1.3 mA,实现了70.8 dB的低频增益,483.1 MHz的增益带宽积和88.8°相位裕度。

图7 (a) CTDSM运算放大器架构;(b) 运算放大器仿真波特图

CTDSM中反馈DAC的原理图如图8所示。输入信号被同步至时钟clk_dac,该时钟相对于量化器的时钟存在延时,其主要的作用有四个:① 重新同步DAC的控制码;② 消除量化器中比较器电路的亚稳态输出;③ 使得DEM模块有足够时间完成量化器控制码的处理;④ 使得环路的ELD是一个确定的量,其值等于两个时钟之间的延时,而ELD补偿的电路参数可根据此延时来确定。

图8 反馈DAC原理图

由于DAC噪声主要受尾电流MOS管闪烁噪声的影响,本文采用poly电阻形式的尾电流(图8中虚线圈),使得DAC更加简洁,面积更小。此外,poly电阻在生产中具有较好的一致性,较MOS管更容易获得好的匹配性能,因而能获得更好的DAC电流之间的匹配。

3 测试结果

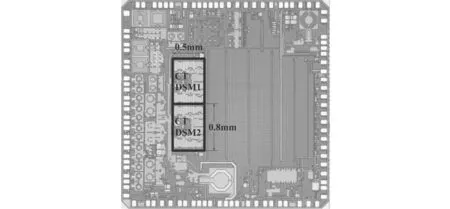

本文TD-LTE终端射频芯片采用0.13-μm CMOS工艺进行流片,其裸片如图9所示。其中CTDSM所在区域如图标示,每组CTDSM(包括I和Q路所用的两个ADC)占用面积0.5 mm ×0.8 mm。对CTDSM进行单独测试,每组ADC消耗电流为25.1 mA。

图9 TD-LTE终端射频芯片裸片照片

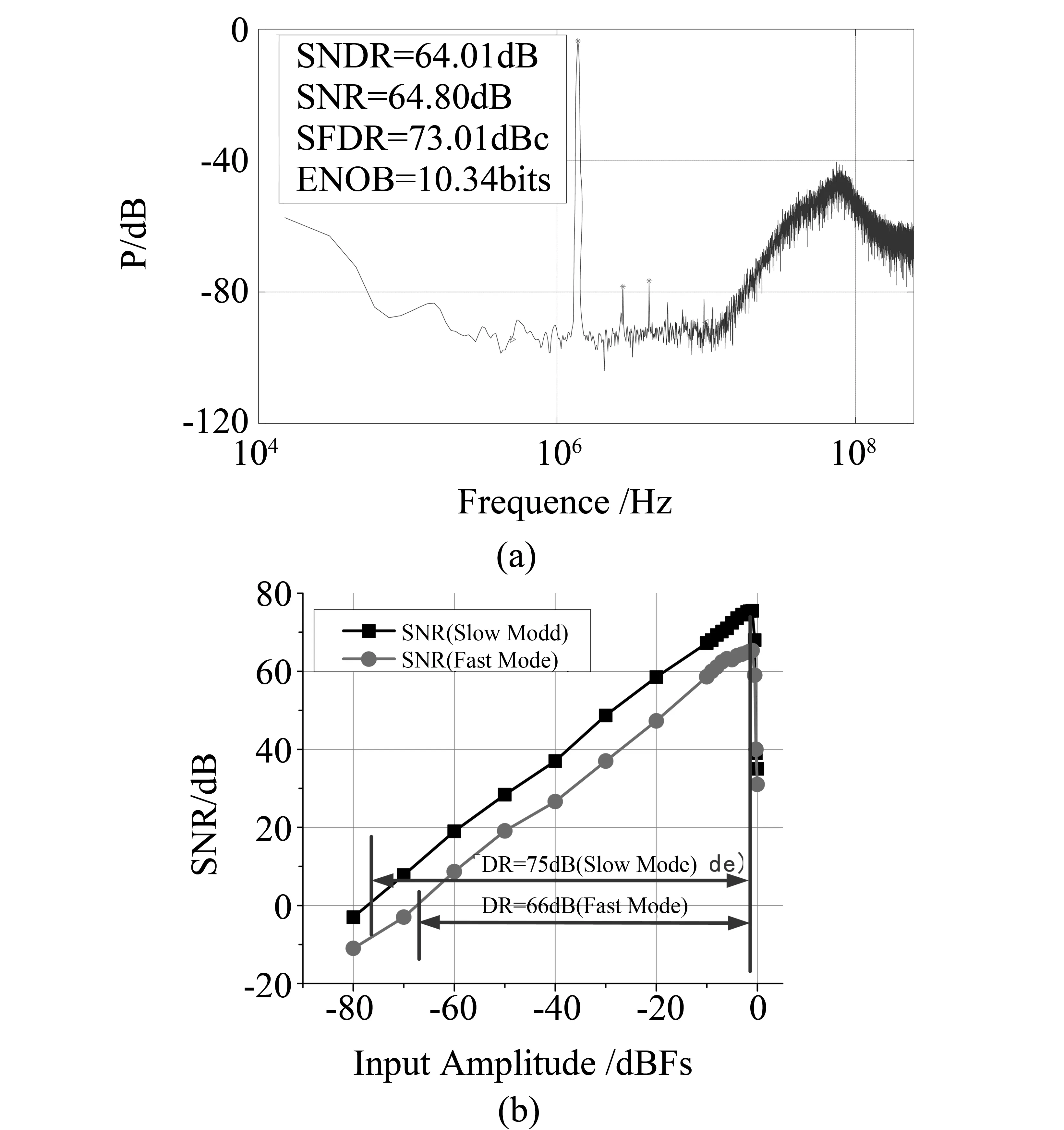

图10 (a) 20 MHz带宽,Fast Mode下,1.38 MHz,-2 dBFS输入信号时CTDSM输出的FFT分析;(b) Fast Mode和Slow Mode下SNR随输入幅度的变化情况

在20 MHz带宽,Fast Mode参数下,在CTDSM输入加入一个1.38 MHz,-2 dBFS的单音信号。用矢量分析仪采集其输出数据,并用Hann窗进行FFT,其结果如图10(a)所示。图10(b)显示了Fast Mode和Slow Mode情况下SNR随输入幅度变化的情况。可以看出,Fast Mode和Slow Mode分别实现了66 dB和75 dB的动态范围,符合了TD-LTE系统的要求。

4 小 结

本文从TD-LTE系统角度,阐述了采用连续时间ΣΔ ADC以节省TD-LTE终端功耗的原理,并进一步讲述了ADC系统构架选择、ELD补偿策略、系数优化的方法,及关键电路的实现。该ADC经过0.13-μm CMOS工艺流片,硅片测试结果显示在其性能满足TD-LTE的系统要求。

参考文献:

[1]周冬跃,胡斌杰.一种空间复用MIMOOFDM联合量化反馈预编码[J].中山大学学报:自然科学版,2013,52(5):39-44.

[2]JOWITT T.LTE power consumption triggers battery worry[DB/OL].[2012-02-20].http://www.techweekeurope.co.uk/news/lte-power-consumption-triggers-battery-worry-61769.

[3]Fitchard K.Why LTE sucks (your battery,that is)[DB/OL].[2012-02-17].http://gigaom.com/why-lte-sucks-your-battery-that-is/.

[4]GUPTA M,KOC A T,VANNITHAMBY R.Analyzing mobile applications and power consumption on smartphone over LTE network[C]∥ International Conference on Energy Aware Computing 2011:1-4.

[5]MUSIIGE D,VINCENT L,ANTON F,et al.LTE RF subsystem power consumption modeling [C]∥Global Conference on Consumer Electronics,2012:645-649.

[6]KOUSAI S,HAMADA M,ITO R ,et al.A 19.7 MHz,fifth-order active-RC Chebyshev LPF for draft IEEE802.11n with automatic quality-factor tuning scheme[J].IEEE J.Solid-State Circuits 2007,42(11):2326-2337.

[7]JO J-G,YOO C,JEONG C,et al.A 1.2 V,10 MHz,low-pass Gm-C filter with Gm-cells based on triode-biased MOS and passive resistor in 0.13μm CMOS technology[C]∥IEEE Custom Integrated Circuits Conference (CICC) 2005:195-198.

[8]PARK M J,A 4th Order Continuous-Time ΔΣ ADC with VCO-Based Integrator and Quantizer[C]∥PHD thesis at the Massachusetts Institute of Technology,2009.

[9]HUANG M,CHEN D H,WANG Z,et al.A power-area-efficient,3-band,2-RX MIMO,TD-LTE receiver with direct-coupled ADC[C]∥International Journal of Circuit Theory and Applications,first published online:7 FEB 2014 | DOI:10.1002/cta.1978.

[10]PAVAN S,Excess loop delay compensation in continuous-time delta-sigma modulators[J].IEEE Trans on Circuits and Systems II:Express Briefs 2008,55(11):1119-1123.

[11]KELLER M,BUHMANN A,SAUERBREY J,et al.A comparative study on excess-loop-delay compensation techniques for continuous-time sigma-delta modulators[J].IEEE Trans.on Circuits and Systems I:Regular Papers 2008,55(11):3480-3487.

[12]ALAMDARI H H,El-SANKARY K,El-MASRY E.Excess loop delay compensation for continuous-time ΔΣ modulators using interpolation[J].Electronics Letters 2009; 45(12):609-610.

[13]DAGHER E H,STUBBERUD P A,MASENTEN W K,et al.A 2-GHz analog-to-digital delta-sigma modulator for CDMA receivers with 79-dB signal-to-noise ratio in 1.23-MHz bandwidth[J] IEEE J.Solid-State Circuits 2004; 39(11):1819-1828.

[14]MITTEREGGER G,EBNER C,MECHING S,et al.A 20-mW 640-MHz CMOS continuous-time ADC with 20-MHz signal bandwidth,80-dB dynamic range and 12-bit ENOB[J] IEEE J.Solid-State Circuits,2006,41(12):2641-2649.