基于SOPC的全彩LED显示系统

李 新,王 雪

(沈阳工业大学,辽宁沈阳 110870)

0 引言

LED显示屏作为一种大型显示设备,具有亮度高、色彩级别高、价格低廉等优点,因此得到了广泛的应用。目前全彩LED显示屏控制系统多采用ARM、单片机等来完成整个系统的功能,这种控制系统在数据处理速度上存在很大的局限,影响显示效果的连续性,不能播放高质量的视频信号[1-2]。目前,LED显示系统一般作为独立的系统或者通过RS232、RS485方式与计算机近距离进行传输,不能满足远距离控制使用的要求[3]。基于以上缺点,采用运行速度更快的FPGA处理器,通过以太网进行数据传输。同时,还增加了脱机显示的功能,增加了SD卡功能的设计。采用Nios II软核嵌入到FPGA的SOPC的方法来实现全彩功耗LED数据包的接收和数据显示的功能。Nios II嵌入式处理器是FPGA生产的CPU,Nios II以软核提供给用户,并专门为Altera的FPGA上实现了优化,用于SOPC集成,最后在FPGA上实现[4]。

1 系统功能描述

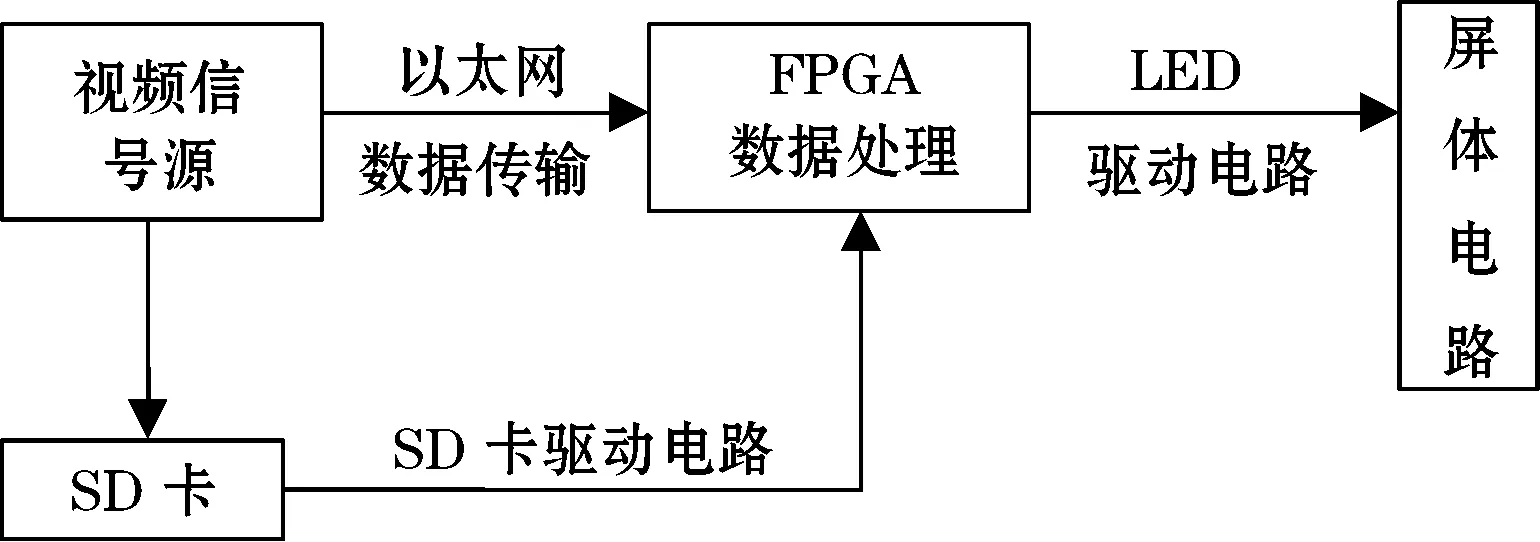

系统实现了主控计算机的实时同步显示和SD卡内部存储异步显示两个部分。系统的功能描述如图1所示,主控计算机的实时同步显示主要包括视频信号源、FPGA数据处理以及屏体电路三部分构成。首先,主控计算产生一个连续的视频信号源,通过上位机经由以太网进行数据的传输,选择合适的通信协议进行数据的传输,存储到的FPGA外部存储器,进行数据的处理,FPGA控制LED的驱动电路,实现屏体电路的实时显示。

图1 系统功能框图

SD卡内部存储异步显示主要由SD卡、FPGA数据处理以及屏体电路三部分构成,首先将动态的视频信号经由特定的软件转化成静态的图片(为了保证视频的效果,这里将1s钟的视频转化为20张图片)。再将图片以bin的形式进行转化,并连续的储存在SD卡内。最后FPGA控制SD卡驱动,然后进行屏体电路的显示。

2 系统设计

2.1系统内硬件设计

系统硬件主要包括FPGA的内部处理系统和FPGA的外设,如图2所示。Nios II是一个可配置的软核处理器,设计主要是基于Avalon总线的NIOS II处理器,对PIO口,定时器,分频器,Flash控制器,SDRAM控制器,JTAG UART,SD卡控制器,LED显示控制器,DM9000A IP核等接口电路进行设计。FPGA外设部分包括外接SDRAM存储器、Flash存储器及SD卡组成。

对Nios II系统的设置需通过Quartus II的SOPC Builder组件来进行设计,正确配置后,生成作为原件备用的原理图模块。SOPC整体框架,包括以太网传输模块、SD卡存储模块、LED显示模块、分频模块以及系统时钟。

1.2DM9000AIP核

图2 系统硬件设计框图

该设计采用Verilog硬件描述语言完成DM9000A IP核的定制,输入输出信号包括Avalon总线,内部寄存器,时钟信号,以及中断请求等。采用IP核设置便于核的移植,方便快捷,使用时将IP核进行移植,在Nois II中进行软件编译即可使用,在Quartus II中完成DM9000A IP核测试。

DM9000A可以和微处理器以8位或16位的总线方式进行连接,可进行单工或者全双工方式进行运行。DM9000A的初始化功能是通过处理器对DM9000A内的网络控制寄存器(NCR)、中断寄存器(ISR)等进行控制来实现的。初始化后芯片进入等待数据收发的状态。接收数据时,首先检测数据帧的合法性,如果校验错误将该帧数据丢弃;如果校验正确将数据帧缓存到内部RAM,通过中断将数据读出。

1.3SD卡设计

SD卡需要高速的读写,同时也要满足嵌入式设备的方便使用。SD卡一般有两种模式构成,SD卡模式和SPI模式,两者的区别是SD卡模式较SPI模式进行数据传输时数据运行速度快,SD卡模式采用6线制方式进行数据通信,SPI模式采用4线制方式进行通信。设计采用SPI模式,SD卡所用系统为FAT32,采用单块读写模式。SD卡的工作模块如图3所示。

图3 SD卡工作流程图

1.4LED显示

设计的模块中每个像素点有16位的数据(即两字节长度),来表示该点的RGB信息。在以太网同步显示中,采用16位真彩RGB565形式将视频截取的BWM图片进行取模,如图4所示。这些取模数据通过上位机进行发送,经过FPGA进行数据处理,然后在LED上进行显示。

图4 RBG565取模显示

2 系统软件设计

2.1数据接收

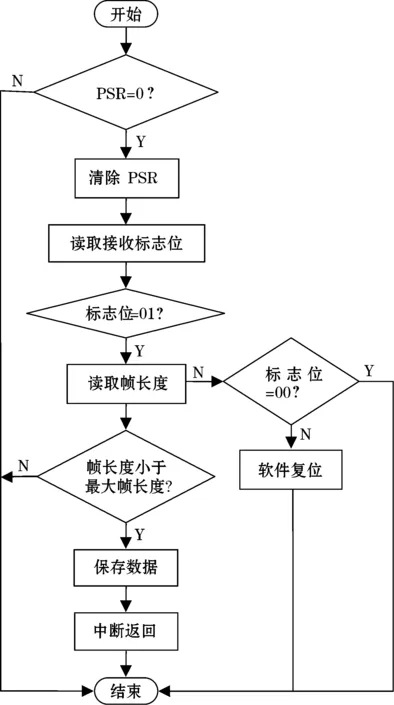

设计用直连网线将计算机与开发板上的网口相连,通过计算机的上位机将数据包发送给DM9000A,DM9000A接收到数据之后会检查数据包是否符合,如果不符合则丢弃,如果符合则核对每个数据包的目的MAC地址和目的IP地址。如果IP地址正确且这个MAC地址是个广播地址或者和该DM9000A的地址完全一致,则这个数据包会被DM9000A保存下来,并给Nios II CPU产生一个中断信号,然后在Nios II CPU中将数据包进行数据处理,接着将数据放入缓冲区,传送给LED显示屏进行显示。读取数据流程如图5所示。

图5 读取数据流程图

图6 网络协议流程图

2.2网络协议

网络接口层利用以太网控制芯片DM9000A和ARP协议实现,网际层采用IP协议和ICMP协议实现,传输层采用UDP协议实现,应用层采用用户自定义协议实现。

传输层采用UDP协议是考虑到两点:(1)基于UDP协议的网络应用程序,实现起来比较简单,并且网络应用程序在运行时,UDP受到环境影响较小。(2)UDP协议占用网络资源较少,数据处理较快。虽然UDP易丢弃数据,但是对于那些丢失若干数据包也不影响整体性的数据,如音频数据,视频数据等,采用 UDP协议要优于TCP协议。网络协议流程如图6所示。

3 实验结果

如图7所示为系统ping结果,搭建完测试计平台后主控计算机发送了4个回显请求,收到了4个回显应答,丢包率为0%,最小返回时间为14 ms,最大返回时间为14 ms,平均时间为14 ms,表明计算机与FPGA开发板网络畅通。如图8所示为全彩LED显示的图片,对网络传输的数据通过TCP/IP测试工具进行速度测试为213B/S.

图7 ping程序测试

图8 图片显示效果

4 结论

系统采用NIOS II软核,结合FPGA进行全彩LED显示的设计,实现了实时以太网的数据通信,通过以太网数据传输和SD卡的数据存储可以实现全彩LED异步视频显示。

参考文献:

[1]马游春,王军辉,李锦明.基于FPGA和以太网接口的光栅解调应用.仪表技术与传感器,2013(2):107-200.

[2]李娟,刘艳滢.基于FPGA的图像采集模块的设计.仪表技术与传感器,2012(10):27-30.

[3]季长红,张斌珍,张剑.基于FPGA的高速实时数据采集处理系统.仪表技术与传感器,2013(6):93-95.

[4]薛飞,宁铎,黄建兵.基于SOPC图像采集系统的设计.仪表技术与传感器,2011(12):49-52.