光接口高速数据采集系统设计与实现

应 斌,严济鸿,何子述

(电子科技大学电子工程学院,四川成都 611731)

0 引言

随着电子学技术的飞速发展,信息科学实验的种类和数量以及科学实验所产生的数据量不断增加。在通信领域,为了实现高速数据中继和测距、测速,必须首先解决传输速率高所带来的问题。现在高速数据采集系统存在许多技术瓶颈,如数据存储深度、数据高效和突发传输、实时处理、数据重复回放等[1]。文中提出了一种高速数据采集方案以满足这些需求。

1 系统方案

硬件系统采用光接口输入原始数据,使用FPGA进行数据的转移以及命令的控制。使用大容量DDR2进行数据在硬件部分的缓存。由cPCI芯片作为硬件板卡与上位机连接的接口芯片负责上位机与硬件板卡的指令以及数据的交互。

整个系统由计算机软件控制,当计算机发送采集命令后,FPGA接收来自光模块的数据然后存入DDR2中,当接收到的数据量满足命令的需求时再由DDR2读出通过PCI总线发回计算机中进行保存和显示。系统结构如图1所示。

图1 数据采集系统框图

2 硬件电路设计

2.1板级电路设计

光收发电路采用单模和多模两种接口,单模器件US0T22D224,单模输入时接口最高数据率2.5 Gpbs,参考时钟125 MHz;多模器件使用MXT-488SIT-F,多模输入时接口最高数据率2G pbs,参考时钟100 MHz.DDR2芯片采用MT47H64M16。系统中,FPGA作为整个系统的控制芯片,不仅仅需要配置芯片CY7C09449完成复杂的PCI总线接口协议,还必须控制高速缓冲器DDR2 SDRAM,设计采用Stratix II GX系列FPGA,型号为EP2SGX90F1508。cPCI芯片使用PCI总线接口控制芯片CY7C09449。该芯片符合PCI 2.2总线规范,满足33MHz,32位的PCI总线,主要资源是一个大小为128kb的双口SRAM,它是本地微处理器如FPGA与PCI总线端的共享存储区。在芯片内部通信时,该共享存储区能够同时被本地总线与PCI总线访问。无论是对于本地总线还是PCI总线,CY7C09449都可以成为总线主设备去控制共享存储区中数据的流入与流出,这种方式称为DMA传输[2]。利用DMA传输方式,可以突发传输大块数据。信息传输单元是CY7C09449芯片另一个重要的组成单元,该单元包括4个32位的FIFO,用来实现消息阵列和中断请求功能。

2.2FPGA内部逻辑设计

FPGA是整个硬件系统的核心,它需要控制光接口接收数据并存入DDR2以及从DDR2中读出并转移至cPCI芯片中并使用DMA方式传输至上位机中。这里主要介绍光接口数据接收模块和cPCI数据传输控制模块,DDR2的读写按时序进行即可。

系统设计中光纤数据格式为4个通道采样数据打入一根光纤,数据格式如图2所示。

图2 一根光纤中的数据格式

其中每路光纤数据有包头控制字7CB5 7CB5,数据间隔中间插入K码BC95,数据尾有包尾控制字9CD5 9CD5。

光接口数据接收控制模块实际就是一个高速收发器,而设计高速收发器关键的步骤就是根据系统要求配置收发器的IP核ALT2GXB.

光口控制模块中可以在ALT2GXB内部把rx_cruclk和pll_inclk相连,使得2个时钟管脚使用1个参考时钟;cal_blk_clk是高速收发器内部终端电阻校准电路的参考时钟输入端,参考时钟频率范围为10~125 MHz,该设计采用频率为30MHz由内部的锁相环产生;tx_ctrlenable是发射通道的控制码(K码)指示信号,指示发射端的输入信号是数据码还是控制码(K码),当tx_ctrlenable=0时,代表输入的信号为数据码,当tx_ctrlenable=1时,代表输入信号为控制码[3]。

值得一提的是由于收发器自身原因,有时候会产生一个字节的拼接错误如图3所示。

拼接正确的数据

拼接错误的数据

发生这种字节错位现象是高速收发器内部原因导致的,而且是随机的,系统每次上电后的情况会不同,有时候会发生拼接错误,因此必须设计一个数据接收校准模块来校准数据,高速收发器接收端有个rx_ctrldetect[1..0]指示信号可以用来指示接收端输出的数据是否存在拼接错位,当rx_ctrldetect[1..0]=1表明拼接正确,当rx_ctrldetect[1..0]=2是表明拼接错误,需要进行校准。数据校准的基本思路是把接收数据datain[15..0]打两拍,存入内部寄存器reg1和reg2中,如果rx_ctrldetect[1..0]=2则把reg2的低字节与reg1的高字节进行重新拼接。

cPCI控制模块中,主要工作分为两部分,第一部分是上位机向FPGA发送配置参数,上位机通过寄存器HLDATA,向FPGA发送配置参数指令;FPGA通过寄存器LHDATA,向上位机返回相应指令表明已经准备好接受配置参数;然后上位机开始向FPGA发送需要配置的参数,当FPGA收到配置参数后会向上位机返回完成配置的响应,如果没有返回响应则从新发送配置参数。发送配置参数流程图如图4所示。

图4 发送配置参数的流程图

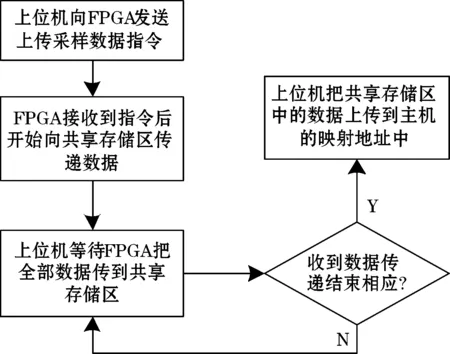

第二部分是FPGA向上位机发送采样数据。上位机通过寄存器HLDATA,向FPGA发送上传采样数据指令,FPGA收到指令后向共享存储区传递采集数据;当数据传输完毕后,FPGA会向上位机发送响应告诉其数据传输结束;上位机收到响应后向CY7C09449发送指令要求把共享存储区中的数据传到主机的映射内存中,然后上位机再把映射内存地址中的数据传到目标地址中。采集数据的流程图如图5所示。

图5 采集数据的流程图

3 软件设计

3.1驱动方案

在官方提供的开发套件中,DRIVER目录下的PCIDP.sys文件即为设备驱动,相应的安装文件Setup.inf在SETUP目录。此驱动是为WINDOWS 2000设计的,但同时它也是WDM驱动,可以从WINDOWS 2000中直接移植到WINDOWS XP中。利用此驱动可以加快项目的开发速度,并减轻开发难度。需要注意的是设备号dwPCINumber与驱动密切相关,必须在应用程序初始化的时候置零,否则驱动无法正常运行。

3.2应用程序设计

应用程序使用跨平台变成软件CodeBlocks,由VC++编写,利用wxWidgets实现框架的设计。整个软件分为:接口控制模块,数据流控制模块,图形绘制模块等。

接口控制模块主要控制上位机与硬件板卡的指令发送。CYPRESS公司提供了驱动相关的动态链接库,也就是DLLs目录下的PCIDP_IF.dll文件,它提供了通过驱动程序操控设备的一切API函数,利用这些函数可以方便的实现与设备的信息交互。配套相应的PCIDP_IF.H和PCIDP_IF.LIB就可以用来开发上位机程序,API函数的具体名称都可以在PCIDP_IF.H查看到,编写上位机时利用PCIDP_IF.LIB就可以实现上位机软件与设备动态链接库的链接。根据软件的需要,将基本API函数封装成硬件检测函数、参数配置函数和数据接收函数,硬件检测函数主要负责板卡初始化连接时确定硬件以及驱动的正确性,需在应用程序开启时首先调用。参数配置函数用于控制硬件板卡的缓冲区长度以及数据通道连接等,在确定硬件及驱动正常运行后立即配置相关参数以确保软硬件在设置上的一致性。如图6示为参数配置窗口,打开软件时立即弹出。图中左上角显示板卡类型即为硬件检测后确定的板卡信息。

图6 上位机应用软件初始化重要参数配置窗口

数据接收函数起到接口控制模块和数据流控制模块的连接的作用,是软件从硬件接收数据的重要函数,将配合数据流控制模块的使用一起介绍。

为了实现引言中提到的数据的重复回放以及实时处理功能,数据流模块必须能够具备一定数据量的缓存以及实时提取的能力,根据上述重要参数配置窗口中获取的缓冲区长度信息,使用数据接收函数一次性获取10个缓冲区长度的数据量,接收上来的循环的A、B、C、D 4路通道的IQ数据,按4个通道分别归类IQ数据,并能单独获取IQ路数据,方便在后续制图和性能指标计算过程中对进行I路数据或Q路数据调用。

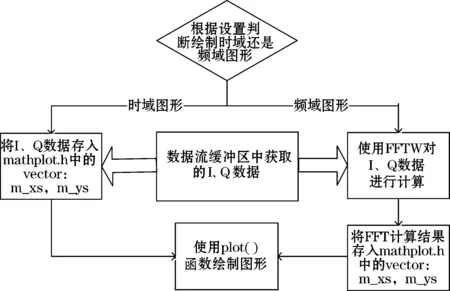

制图模块使用了wxWidgets中的制图类mpWindow,并以此为基类派生一个符合程序具体使用要求的派生类mpPlotwindow集成了所有对制图窗口操作的函数,其中包括图形窗口的右键快捷菜单响应函数、获取缓冲区中数据进行制图函数等。制图函数中需要使用头文件mathplot.h[4]。绘图流程如图7所示。

4 测试结果及分析

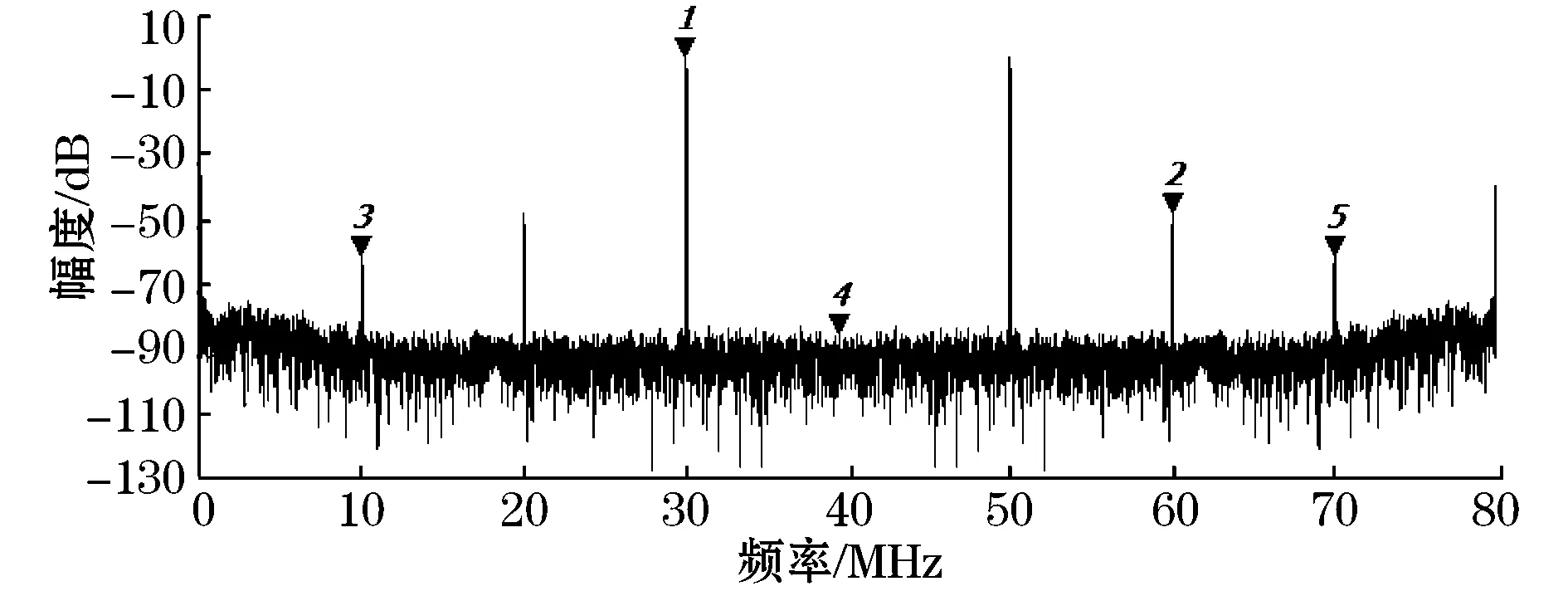

信号源产生中心频率为30 MHz的正弦信号,在80 MHz的采样率下采集该信号,缓冲区长度设置为64 K,数据传至上位机绘制以半采样频率为中心的频谱,如图8所示。

从频谱以及右边的参数显示中可以看出该系统能够正确显示有效信号的频率并准确的寻找到2到5次谐波。由于信号频率较大,信号频率的整数倍大于采样率因此产生了频谱搬移,因此产生了图中3次和4次谐波频率低于2次谐波的现象。

信号源产生28.1 MHz信号,在4 MHz采样率下采集信号并经过下变频处理后产生中心频率为1MHz的IQ正交信号如图9示为上述信号的频谱,图10所示为上述信号的时域波形。

图7 绘图流程

图8 80 M采样率下采集30 M正弦信号所绘制的频谱

图9 4MHz采样频率下采集0.1 MHz正弦信号所绘制的频谱

图10 I、Q两路正交信号时域波形

从图10可以看出幅度一致性误差仅有0.042dB,相位一致性误差0.01°,检测结果说明系统正确传输了经过下变频后产生的正交信号并精确计算出相位一致性误差等参数,也从另一个角度说明了数字前端成功进行了下变频处理。

5 结束语

从测试结果可以看出基于FPGA、DDR2、cPCI的硬件构架可以很好的实现高速采集,上位机中使用wxWidgets以及FFTW库函数可以精确分析信号参数。但是由于计算机硬件运算速度的限制,在大数据量FFT计算过程中会消耗过多的CPU资源,计算机无法实现持续大数据量的高速计算。当今计算机技术高速发展,相信在不久的将来,随着CPU运算速度的不断提高,实现对大数据量数据进行快速的频谱分析和运算不是难事。

参考文献:

[1]张琴,马游春,李锦明.基于PCIExpress高速数据采集卡接口的设计.测控技术,2011,29(2):63-66.

[2]CY7C09449PV-AC Data Sheet.Cypress Semiconduct or Corporation,2002.

[3]ALTERA Corporation.Stratix II GX Device Handbook[EB/OL].www.altera.com.

[4]朱丙立,熊江,跨平台框架程序wxWidgets的应用.电脑知识与技术,2006(5):132-133.