基于“魂芯一号”的雷达信号处理机边扫设计∗

王凤驰,陈常青,李正东

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

雷达信号带宽、接收通道数量及工作模式种类等的不断增长,对雷达信号处理机的实时处理能力、运算密集度、高速数据传输等性能提出更高的要求,高性能DSP处理器已经成为雷达中的一个重要部件。目前,国内雷达装备的信号处理机都采用国外DSP处理器,如ADI的TS20x系列、TI的TMS320Cx系列等,由中国电子科技集团公司第三十八研究所研制的BWDSP100芯片填补了这一空白,在国防安全和战略上具有重大的意义[1]。

BWDSP100芯片是一款性能优越的高端DSP处理器,适合于雷达信号处理、电子对抗、精确制导武器、通信保障等领域。而以BWDSP100芯片为基础的某雷达信号处理机更是已在雷达信号处理上推广应用[2]。该信号处理机采用了CPCI 6U板卡标准,由4片BWDSP100处理器构成核心运算单元,每个处理器外接一组DDR2 SDRAM存储器,容量为1 GB。4片BWDSP100处理器之间通过Link链路口和并行接口共享外部FLASH存储器资源。在对外接口方面,处理机采用两片Altera公司的大规模FPGA器件构成符合CPCI总线标准要求的各种通用接口,可支持PCI总线、LVDS以及高速光纤总线等。

1 可测试性分析

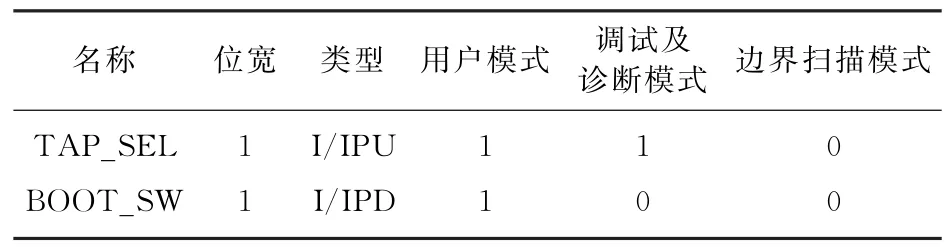

BWDSP100芯片的边界扫描系统基于JTAG标准协议(IEEE-1149.1-2001)来实现[3],除了TCK、TMS、TDI、TDO、TRST_n 这些标准的JTAG信号外,还增加了TCK_RET、TAP_SEL和BOOT_SW等辅助信号,用于更好地实现DSP芯片的在线调试功能。其中,TCK_RET(Test Clock Return)是TDO信号的随路时钟,为在线调试时使用,当边界扫描测试时,可以不用理会。而TAP_SEL和BOOT_SW两个信号则共同定义了BWDSP100芯片的工作模式,其具体设置如表1所示。

表1 BWDSP100芯片的工作模式设置表

BWDSP100芯片在边界扫描模式下,支持EXTEST、BYPASS、SAMPLE、PRELOAD、HIGHZ和CLAMP六种指令,指令长度为4 bit,扫描链的长度为369。同时,BWDSP100芯片有大量的差分对设计,在边界扫描测试时可以充分加以利用[4]。例如:

另外,BWDSP100芯片的边扫单元设计采用了较多的BC_7和BC_4单元,其中BC_7单元是一个支持双向系统引脚的数据单元,它能够提供数据给输出驱动的同时,还能实时监控输出的引脚。这是一个很重要的特性,因为它可以发现输出引脚短路的情况。BC_4单元是一个简单的,既没有“更新”寄存器又没有多路选择器的电路结构,它的特点是减少了可能出现的系统信号的传输延迟。BC_4单元不支持INTEST指令,因此除了时钟信号的输入引脚外,BC_4单元不能用在其他输入引脚上。BWDSP100芯片因为采用了较多的BC_4单元,所以也不支持INTEST指令。

2 边界扫描TPS设计

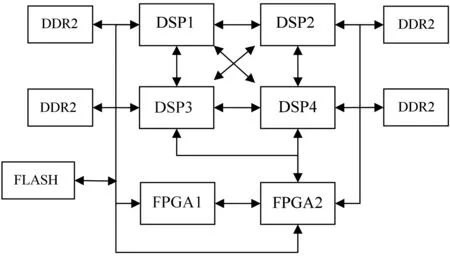

该雷达信号处理机由于使用的BWDSP100芯片、FPGA芯片以及4片DDR2芯片均是BGA封装,且板卡设计集成度很高,采用边界扫描测试是较为合适的方法,参见图1。通过比较,我们选择了ASSET公司的Scanworks工具作为边界扫描的开发工具。ASSET公司是一家专业从事边界扫描技术开发与研究的公司,它参与了IEEE1149.1、IEEE1149.4、1532、1149.6 等有关JTAG标准的制定。其开发的边界扫描工具Scanworks在销售市场的占有率第一,并且与摩托罗拉、诺基亚、思科、Aglient等知名公司有着长期良好的深度合作关系,如Aglient研制的i3070,采用针床测试同时嵌入Scanworks作为边界扫描的工具。Scanworks软件在国内是有多家用户,其中不乏知名度很高的企业,如华为、14所、41所、北京航天测控公司等。

图1 某雷达信号处理机架构图

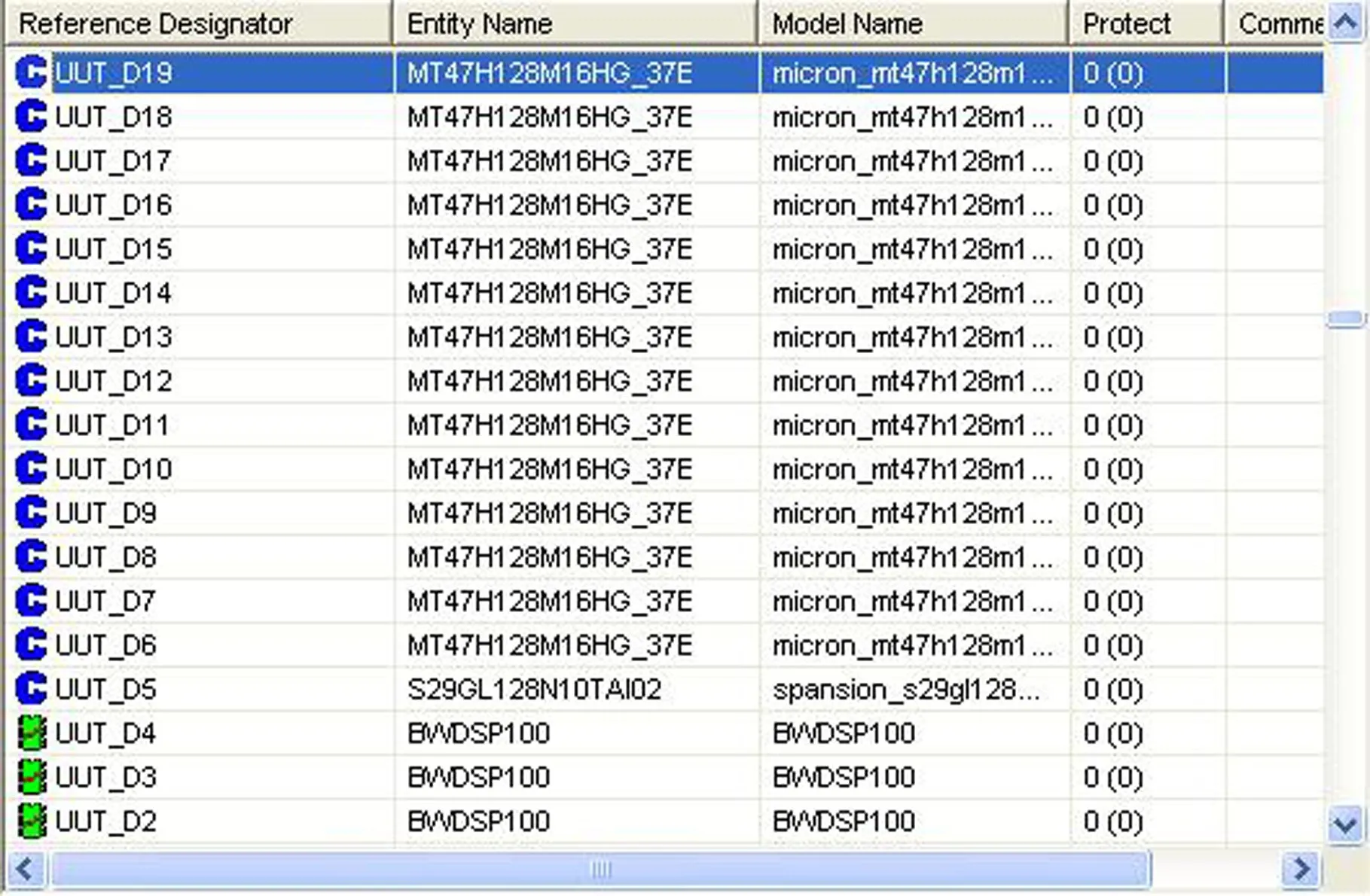

使用Scanworks工具对文中叙述的雷达信号处理机进行边界扫描测试开发时,需要结合其电路的互联结构进行TPS(Test Project Set)设计,该雷达信号处理机的2片FPGA和4片BWDSP100芯片都植入了边界扫描链结构,在设计时除了对这六个芯片进行互联测试外,还要以它们产生测试激励,对外围的DDR2芯片和FLASH芯片进行测试。其设计完成后的测试列表截图见图2。

图2 某雷达信号处理机在Scanworks工具中的测试列表

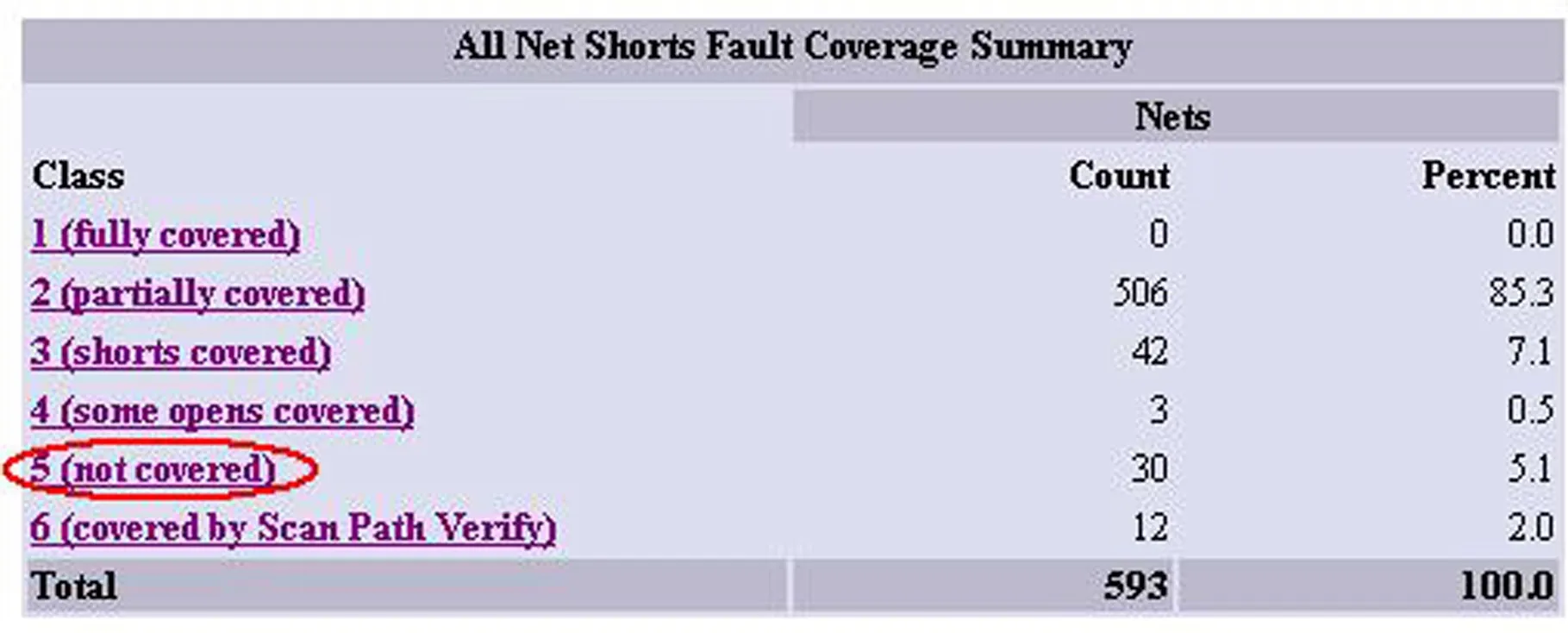

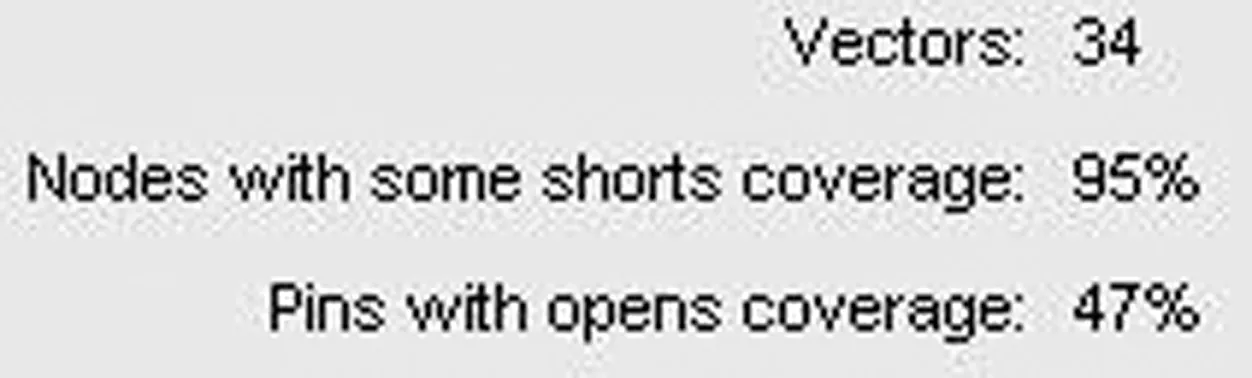

由于边界扫描测试速率目前最高只有40 MHz,很难匹配信号处理机数百兆的工作频率,因此只能用于检测板卡的硬件焊接连接性,对于高速信号中的隔直电容电路,只能通过功能测试的方法。这部分高速电路涉及的信号网络在该雷达信号处理机的信号网络中只占很少的一部分。通过网络分析,该雷达信号处理机共有网络593个,边界扫描测试未能覆盖的仅30个,占比5.1%,如图3所示。

图3 信号网络故障覆盖分析

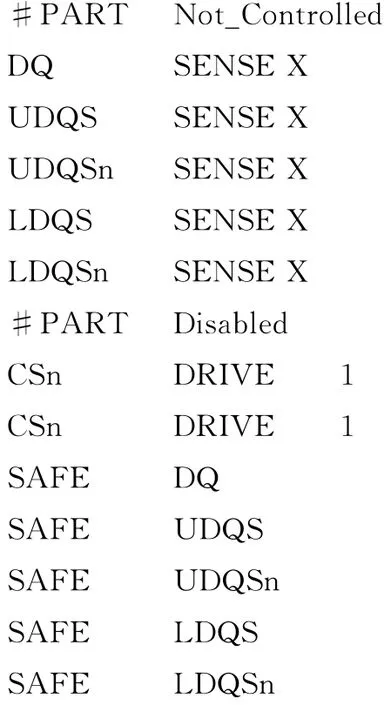

边界扫描测试可以通过边界扫描单元的互联进行短路、开路的测试,简称为“互联测试”,也可以通过访问存储器,对存储器的地址、数据总线以及内部存储单元进行测试,简称为“存储器测试”。在互联测试时,需要对不相关的器件进行屏蔽,消除功能性的影响,这个时候就需要设计各种器件的模型,根据器件的要求给相关管脚施加“0”或“1”信号,从而起到屏蔽的效果,例如针对该雷达信号处理机的DDR2存储器(型号为MT47H128M16)设计模型如下:

在测试算法上可以有很多选择,例如全“0”、全“1”,走步“0”和走步“1”等,全“0”、全“1”算法在测试准确性上明显不足,而走步“0”和走步“1”算法是指“0”或“1”信号在所有测试节点上逐个移位。该算法能有效排除短路、开路故障,准确度很高,但是在节点数量巨大、信号复杂的电路板上,走步算法显然效率不高。相比之下,瓦格纳算法则是一个较好的选择,瓦格纳算法优化了测试向量的种类,在保证覆盖率达到99%以上的情况下,所需测试向量仅为log2(2∗n+1)个,其中n为信号网络的数量。例如1 000个信号网络只需要11个测试向量,5 000个信号网络只需要14个测试向量,大幅度提高了测试效率。

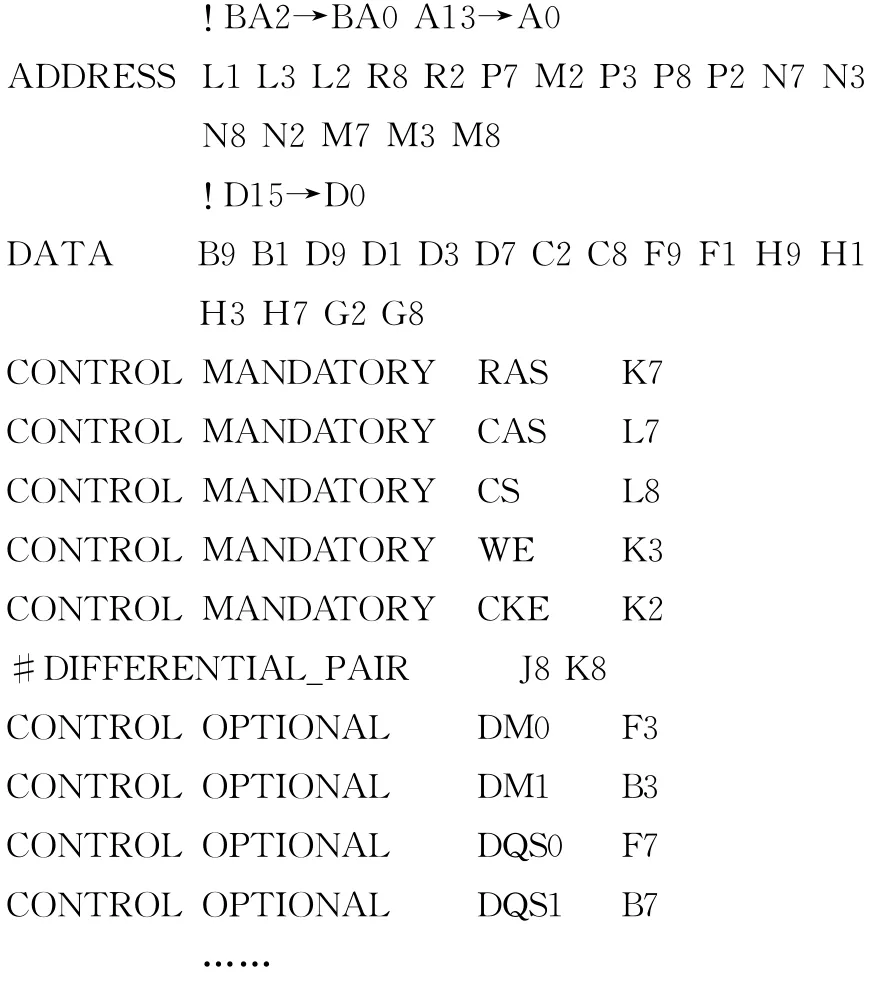

互联测试已经能够解决大部分的硬件故障,除了互联测试之外,还进行了专门的存储器测试,以提高故障覆盖率。存储器测试也需要设计相应的测试模型,仍以DDR2存储器(MT47 H128M16)为例,设计模型如下:

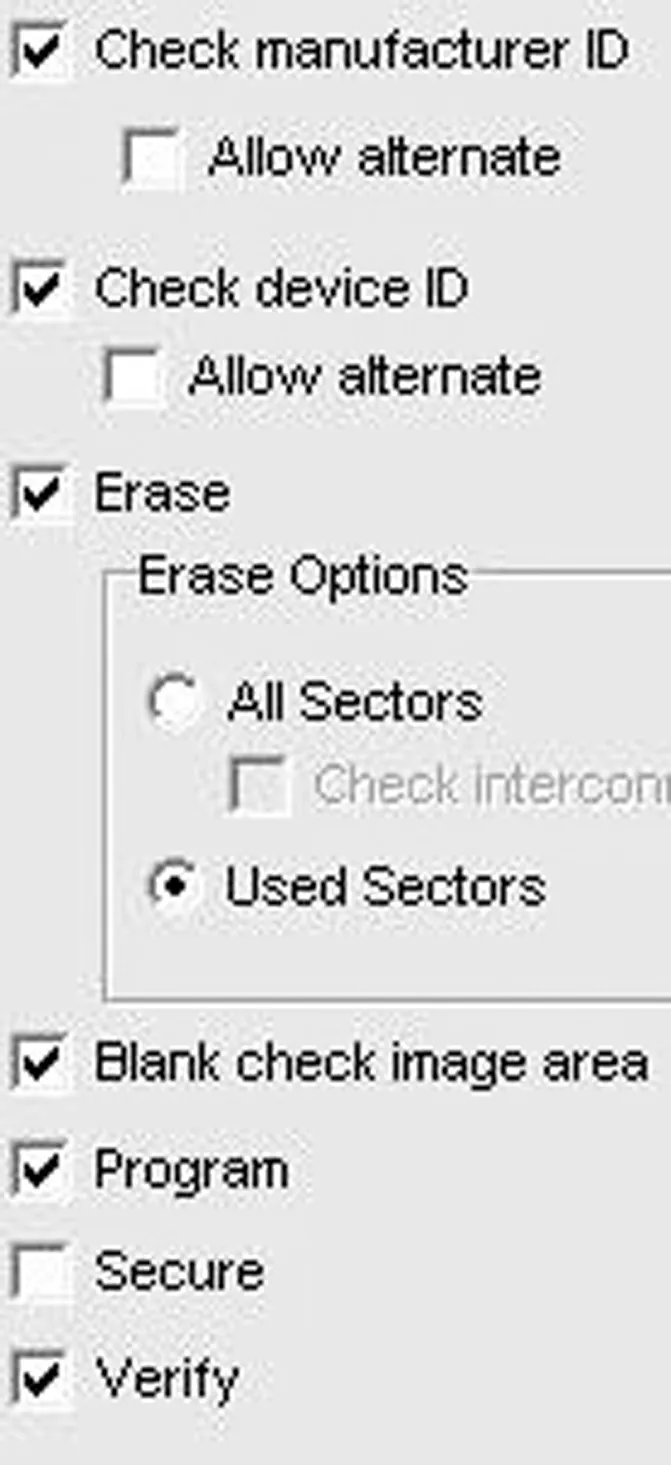

除了存储器之外,FLASH也是一种专门的测试,但不同的是FLASH只需要提供协议,如读写地址、读写序列、ID号、单元大小等信息,边界扫描测试可以对FLASH进行擦除、写入、加密、比较等一系列操作,如图4所示。

另外,还有自定义测试,即通过脚本语言,人为地定义测试方式。这种方法针对LED、数码管等简单功能测试非常有效。常用的脚本语言如TCL语言,是一种使用便捷的不需要编译的执行语言,只需要根据语句逐条的执行即可。

图4 FLASH操作

经过边界扫描测试的TPS设计,该雷达信号处理机在互联测试中短路故障覆盖率高达95%以上,经过试用也的确能够在调试过程中发挥重要的作用,例如常见的小电阻虚焊、细间距芯片管脚粘连等肉眼难以发现的故障,基本都能通过边扫测试予以排除。这在一定程度上不仅挽救了这些动辄数十万的昂贵的雷达信号处理机,也进一步排除了故障隐患,提升了产品可靠性。其故障覆盖率如下:

3 结束语

由于BWDSP100芯片被越来越广泛地使用,其良好的可测试性设计,使测试工程师在TPS开发中能够放心地使用。经过对某雷达信号处理机的TPS开发,其最终的故障覆盖率超过90%,也充分验证了这一点。在DDR2存储器和FLASH测试上,则充分考虑模型的设计和测试激励的选择,模型的设计要符合被测存储器的自身特点,测试激励则可以从相连边界扫描管脚中任意选择,有较大的灵活性。

[1]穆文争,史鸿声,刘丽.国产高性能通用数字信号处理器的DEMO板设计[J].火控雷达技术,2012,41(3):33-36.

[2]史鸿声,穆文争,刘丽.基于“魂芯一号”的雷达信号处理机设计[J].雷达科学与技术,2012,10(2):161-164.SHI Hong-sheng,MU Wen-zheng,LIU Li.Design of Radar Signal Processor Based on Hun Xin-1 Chip[J].Radar Science and Technology,2012,10(2):161-164.(in Chinese)

[3]中国电子科技集团公司第三十八研究所.BWDSP100硬件用户手册[M].合肥:中国电子科技集团公司第三十八研究所,2011.

[4]谭剑波,尤路,黄新,等.边界扫描测试技术[M].北京:国防工业出版社,2013.

——信号处理