基于MicroTCA的EPICS控制系统研究

雷碧峰,王春红,刘正同,吕慧慧

(中国科学院 高能物理研究所,北京 100049)

随着加速器系统的快速发展,对控制系统的高数据传输率、低延时提出了更高的要求。同时,更加智能化和数字化的控制器在加速器中的大量采用,也要求新控制系统具有更好 的 智 能 化 和 灵 活 性[1]。传 统 的VME 和CompactPCI系统在传输速度方面均有一定限制,新型的MicroTCA 系统是一种全新的基于机箱式的模块化设计,具有高可用性、高扩展性、高数据传输速率、支持热插拔等优点[2]。

相比于传统的控制技术,MicroTCA 技术具有智能化高、灵活性强、性能好、性价比高等优势,这些优势使其非常适合在有高数据传输率、低延时要求的控制系统中使用。目前,在国际加速器控制领域研究中,MicroTCA技术正逐渐成为一热门研究课题。EPICS 平台是一种集成的开发环境,能有效提高系统的开发和运行维护效率。目前,EPICS在各种类型的加速器中得到了广泛使用,基于EPICS平台的控制系统的研究已是国内外加速器控制技术中非常重要的一个方面。本文使用Heytec公司的硬件建立一套基于MicroTCA 总线的EPICS控制系统,对MicroTCA 总线及硬件接入EPICS系统进行研究。

1 系统开发

1.1 系统硬件结构

本工作开发了一套完整的单宽尺寸的MicroTCA系统,外部通过信号调理端子形成理想的现场回路,使用基于PCI-e x16 协议的背板总线来模拟信号的控制和反馈。MicroTCA系统的结构如图1所示。该系统的基本组件包括:1块CPU 模块;1块硬盘模块;2块Hytec-AMC载板卡;1块N.A.T MCH 模块;1块夹层总线模数转换板ADC-IP 卡;1 块夹层总线数模转换板DAC-IP卡。该系统的硬件实物图如图2所示。

图1 MicroTCA 系统的结构Fig.1 Architecture of MicroTCA system

图2 MicroTCA 系统的实物图Fig.2 Prototype of developed MicroTCA system

1.2 基于EPICS的软件架构及开发

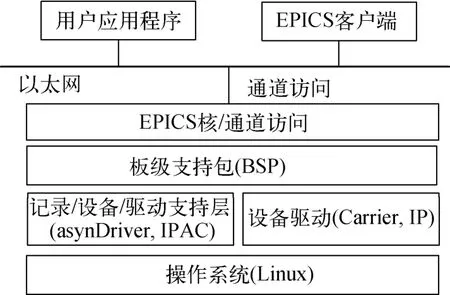

基于EPICS的应用程序架构如图3所示。本文以该结构为原型系统开发了软件系统,主要包括3 部分:设备驱动及其支持程序,EPICS IOC和实时监控系统(OPI)。

图3 基于EPICS的应用程序架构Fig.3 Architecture of software based on EPICS

1)设备驱动

设备驱动开发主要完成3 部分:PCI设备驱动开发、载板卡驱动开发和IP卡驱动开发。

PCI设备驱动将操作系统的BSP与EPICS中的载板卡驱动衔接起来,通过一个指向结构体指针在初始化时调用PCI设备注册函数以完成驱动程序的注册,并通过PCI层来完成载板卡设备的探测和支持热插拔操作。同时,该载板允许IP卡接入到其硬件的I/O 寄存器和内存空间。

本文基于IPAC 程序包开发了AMC 载板卡驱动程序,其用于将ADC-IP 和DAC-IP 卡与IP卡支持程序粘合在一起,通过实现IPAC定义的标准接口为IP 卡的访问提供一组标准的API。AMC载板卡驱动程序允许IP卡的驱动直接通过该API接入到底层设备中,从而屏蔽了载板卡和IP 卡的详细信息。无论是模拟IP卡还是数字IP 卡,均可使用该API接入到底层设备中。

本文基于asynDriver程序包开发了IP 卡驱动程序,其为IP 卡接入到EPICS系统中提供了接口,并兼容了OSI标准模型,包括ADC和DAC 两个IP 卡的驱动程序。IP 卡的驱动程序包括6部分:设备初始化程序、asynDriver接口函数实现、设备私有的操作程序块、浮点电压转化程序块、中断程序块和外部程序。

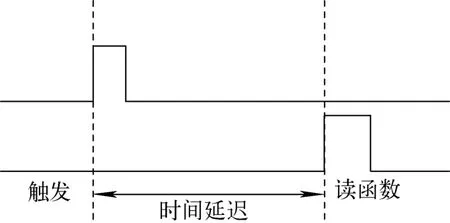

驱动程序的中断机制设计是决定系统响应时间的重要因素。本文利用PCI设备驱动和基于IPAC 的载板卡驱动共同构成完整的、能向载板卡和IP 卡驱动分发快速中断服务的中断处理机制。该机制通过一特定的结构体来实现,结构体包含设备句柄、唤醒排队句柄、中断向量等基本元素。图4 为PCI驱动的中断延迟示意图。

图4 PCI设备驱动的中断延迟Fig.4 Interrupt latency in PCI device driver

2)EPICS IOC及其记录支持开发

IOC输入输出控制器是EPICS 控制系统最重要的部分,为一常驻内存的实时数据库系统,用于存放来往于设备的实时数据,包括数据库开发和记录支持开发。

本文开发了EPICS数据库记录支持层,定义了两个用于数据读入/出的记录类型,并为每类设备开发了14个记录类型的通道控制操作,能满足EPICS基本应用要求。使用EPICS标准数据库定义文件、asyn.dbd 和drvIpac.dbd定义文件生成IOC 应用的数据库定义文件utca.dbd。使用VDCT 工具对数据库进行了开发,该数据库用于支持系统运行调试和性能测试。

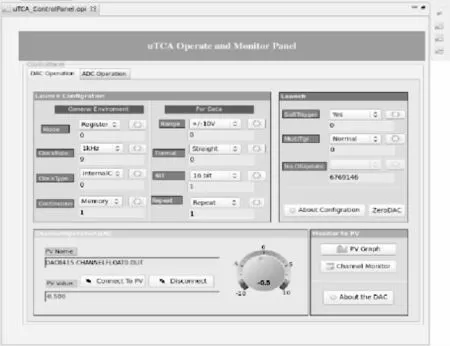

3)实时监控系统(OPI)开发

本文使用CSS 工具包开发了独立的实时监控系统,如图5所示,其主要功能包括:系统启动与关闭;系统实时状态监控;系统运行参数设置;ADC/DAC通道操作与监控;PV 实时与历史数据浏览等。

2 系统测试

2.1 操作系统级硬中断响应时间测试

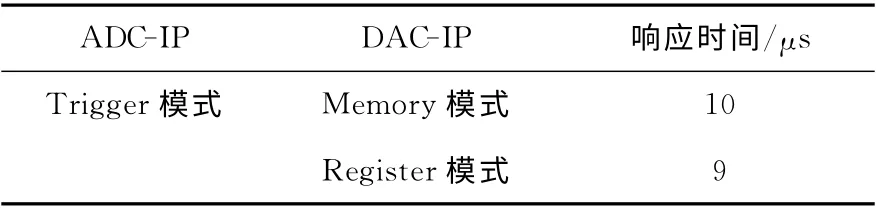

主要测试MicroTCA 系统运行过程中,Linux层的PCI设备驱动对外部触发的中断响应时间。该测试需在Linux 操作系统的PCI设备驱动层展开,分别利用Memory 和Register模式下的DAC-IP 触发一个中断,测试Linux 操作系统对处于Trigger 模式下的ADC-IP的中断响应时间。在PCI设备驱动的中断进程中加入时间标记点,该标记点位于中断触发后和进入中断处理前,通过计算对应的时间差得到相应的ADC-IP在Trigger模式下的中断响应延时。Linux操作系统中断延时如图4所示,测试结果列于表1。从测试结果可看出,外部信号的细节并不会影响测试结果,这说明该测试并未涉及到PCI上层的应用系统。所以,该时间差能很好地反映出系统核级中断响应的实际延时。

图5 MicroTCA 系统控制与运行监测界面Fig.5 Control and monitor OPI of MicroTCA

表1 操作系统级的中断响应时间测试结果Table 1 Test result of response time in Linux kernel level

2.2 EPICS应用级的响应时间测试

该测试主要用于测试该系统对外部中断的响应时间,需在IP 卡驱动层的中断程序中展开。本文分别在ADC-IP和DAC-IP卡异步驱动程序的中断进程中加入时间标记点,该标记点位于中断响应开始后和进入中断处理前,通过计算对应的时间差,可得到EPICS应用系统的中断响应延时,测试结果列于表2。从表2可看出,本次测试得到的响应时间远大于操作系统级中断响应时间。

表2 系统EPICS应用级的响应时间测试结果Table 2 Test result of response time in EPICS application level

2.3 测试结果分析

通过上述测试结果可看出,系统在Linux核内的硬中断响应时间优于10μs,而传统的VME 系统在VxWorks核内的硬中断响应时间约为20μs级,因此,该系统对10μs级高速通讯的系统具有非常好的应用价值。

从测试结果可看出,本系统在EPICS应用级的中断响应时间延迟相对较大,说明该系统的应用软件具有较大的优化空间,可通过进一步的优化使系统的性能得到提升,从而使其具有非常好的应用价值。

3 结论

本文基于MicroTCA 硬件开发了一个Linux/EPICS控制系统原型,完成了底层驱动开 发、EPICS 支 持 层 驱 动 开 发、EPICS IOC 和数据库及其支持层驱动开发、基于CSS的客户端开发。通过对Linux 操作系统的硬中断和EPICS应用级的中断响应时间的测试,可得出系统在Linux 内核中板卡级硬中断响应优于10μs,即对10μs级高速通讯的系统有应用价值。另外,本工作使用的Linux为非实时操作系统,也是影响响应时间的一个因素。若采用RTLinux,MicroTCA 系统在内核中的响应时间将会进一步提高。所以,MicroTCA 系统在低延时及灵活性和智能化要求较高的系统中具有较好的应用价值。

[1] LARSEN R S.Advances in developing next-generation electronics standards for physics[C]∥Real Time Conference.Beijing:IEEE,2009.

[2] VERSTOVŠEK I,AMAND F,PLEŠKO M,et al.THXA01:Recent trends in accelerator control systems[C]∥Proceedings of IPAC.San Sebastián,Spain:IPAC,2011.