基于FPGA的K计数环路滤波器的设计

黄保瑞,杨世平

(延安大学物理与电子信息学院,陕西延安716000)

基于FPGA的K计数环路滤波器的设计

黄保瑞,杨世平

(延安大学物理与电子信息学院,陕西延安716000)

介绍了K计数环路滤波器的基本结构和工作原理,提出了一种基于FPGA的K计数环路滤波器的设计方法,采用Verilog硬件描述语言进行编程,Xilinx ISE软件进行综合及时序模拟。

FPGA;环路滤波器;Verilog

滤波电路是对于信号频率具有选择性的电路,使特定频率范围内的信号顺利通过,而阻止其它频率信号通过,按照滤波电路的工作频率带为其命名,分为低通滤波器、高通滤波器、带通滤波器、带阻滤波器等[1],按信号类型可分为模拟滤波器和数字滤波器。随着数字技术的发展,滤波电路是也向数字化方向发展。目前数字滤波器可以通过现场可编程门阵列(FPGA)、专用集成电路和数字信号处理等器件进行设计,由于FPGA器件结构体系的日益完善,运行速度的大幅度提高,利用FPGA器件的现场可编程特性,既可缩短设计周期,又可反复修改调试,成本较低[2]。鉴于FPGA的众多优点,本文也采用FPGA的方法设计一个K计数环路滤波器。

1 工作原理

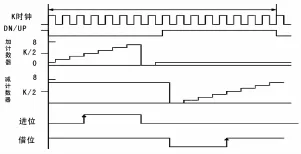

全数字锁相环滤波电路中,K计数环路滤波器是最重要的数字环路滤波器之一,它通常和异或门鉴相器或JK触发鉴相器一起工作,K计数环路滤波器由两个相互独立的计数器组成,一个称为“加(UP)计数器”另一个称为“减(DN)计数器[3]”,其模块结构如图1所示,在实际应用中,两个计数器都是向上计数的,K为这两个计数器的模,计数范围都是[0,K-1],其K值可根据具体电路要求通过模K控制进行设定,K的取值一般为2的整数次幂。K计数环路滤波器根据鉴相器输入的相位差信号来控制K计数器的加减运算,当输入信号为低电平时,加计数器对K时钟信号进行计数,减计数器保持不变,加计数器的值为[K/2,K-1]时进位端输出高电平。当输入信号为高电平时,减计数器对K时钟信号进行计数,加计数器保持不变,减计数器的值为[0,K/2]时借位端输出低电平。根据加减计数器的工作特点,当输入信号有高频信号或随机信号干扰时,计数器加减的数目基本相等,计数结果在初始值处上下徘徊,不会产生进位和借位脉冲,即可滤除鉴相器输出的相位差信号中的高频成分,保证环路的性能稳定,防止因随机噪声引起的相位抖动。

图1 K计数环路滤波器模块图

2 K计数环路滤波器的设计

2.1 设计要求

K计数环路滤波器主体是两个计数器,信号输入由鉴相器的输入信号控制,使用的是JK鉴相器,其输入信号是占空比为50%的方波,它在半个周期内为低电平,另外半个周期内为高电平,要求K时钟频率是中心频率的16倍,计数器的模为8,根据K计数环路滤波器的工作原理,可以得到加计数器在前8个K时钟脉冲里计数,当计数达到4时开始输出进位信号,计数达到8时,加计数器归零,进位信号终止。减计数器在接下来的8个脉冲里计数,在第一个脉冲后开始输出借位信号,减计数值为4时借位信号终止。这样在输入信号的每个周期内恰好都会产生一个脉冲宽度相同的进位和借位脉冲,其理论波形如图2。

图2 理论波形

2.2 程序编写与仿真

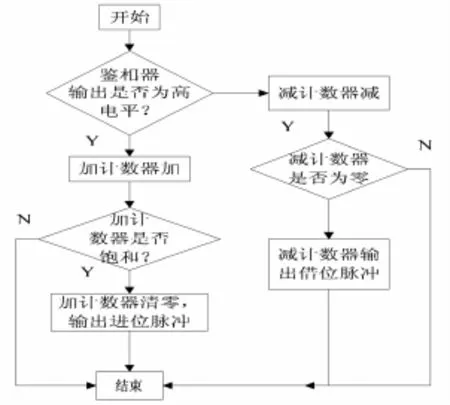

图3 设计流程图

FPGA系统设计流程包括需求分析、器件选择、设计输入、功能仿真、综合优化、后仿真、布局布线、板级验证和调试几个步骤[4]。滤波器设计按照流程逐步实现,由于Xilinx公司开发的ISE软件主要功能包括设计输入、综合、仿真、编程文件生产和下载[5],几乎涵盖了整个PFGA开发的全部流程,所以采用ISE13.1集成开发环境进行设计。设计输入环节将整个滤波器系统划分为若干个子模块,模块首先进行初始复位,判断鉴相器输出电平,加计数器和减计数器判断是否达到极限值,然后输出进位或借位脉冲,整个K计数环路滤波器程序编写设计流程如图3。

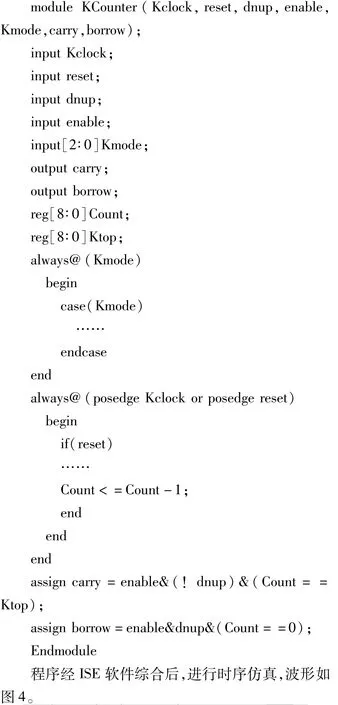

根据图3的流程,使用Verilog硬件编程语言编写程序,部分设计程序如下:

图4 时序仿真波形

3 结束语

本文主要研究了基于FPGA的K计数环路滤波器的设计,其仿真波形与理论波形相吻合,证实了采用该方法设计滤波器的可行性。基于FPGA的设计方法可以对程序进行反复的修改测试,能有效地缩短滤波器的设计周期,并通过简单的改写现有程序代码即可设计出满足实际需求的K计数环路滤波器来,也能为全数字锁相环作为现成模块被调用,具有很好的应用前景。

[1]童诗白,华成英.模拟电子技术基础[M].北京:高等教育出版社,2005.

[2]包本刚.基于FPGA的FIR滤波器的设计[J].湖南科技学院学报,2005(11),67-70.

[3]Roland E.Best锁相环设计、仿真与应用[M].李永明译.北京:清华大学出版社,2007.

[4]赵吉成.Xilinx FPGA设计与实践教程[M].西安电子科技大学出版社,2012.

[5]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[责任编辑 贺小林]

Design of the Count of K Loop Filter Based on FPGA

HUANG Bao-rui,YANG Shi-ping

(College of Physics and Electronic Information,Yanan University,Yanan 716000,China)

This paper introduces the basic structure and working principle of the count of K loop filter,proposes a design method of the count of K loop filter based on FPGA,using Verilog hardware description language for designing,the Xilinx ISE software synthesis and timing simulation.

FPGA;loop filter;verilog

TN492

A

1004-602X(2014)04-0023-03

10.3969/J.ISSN.1004-602X.2014.04.023

2014-09-15

黄保瑞(1982—),男,陕西横山人,延安大学实验师。