宽带小步进频综的小数分频PLL解决方案

高杰

(中国电子科技集团公司第54研究所 河北 石家庄 050081)

小步进、低相躁、宽频带是锁相环设计中相互矛盾的几个指标,小步进要求低鉴相频率、低鉴相频率导致分频值的增大从而恶化相位噪声,宽频带意味着VCO的品质因数低,导致VCO开环相位噪声的恶化[1]。解决这一矛盾的方案有DDS+PLL、混频环、小数分频等。对于极小的频率步进要求,混频环方案不再可行。小数分频方案因为其固有的杂散问题长期以来并没有在高性能宽带频综中得到应用。Hittite公司48bit∑-Δ调制PLL套片HMC983、HMC984的推出,使得小数分频方案在小步进、高解析度、宽频带频率综合器中的应用成为可能。

1 几种小步进宽带频率合成方案的优缺点比较

1)DDS+PLL的方案

优点:频率步进小、切换时间短、相位噪声指标高、频率解析度高。

缺点:成本高,结构复杂、DDS本身需要配置高性能的时钟环路做参考入,DDS无杂散频率范围窄,需引入混频器扩展频率范围,需要滤波器滤除组合频率干扰。

2)混频环的方案

优点:相位噪声指标高、功耗低;

缺点:频率解析度低、需要多个混频器、需要高性能滤波器滤除组合频率干扰。

3)小数分频方案

优点:成本低,结构简单、频率解析度高,输出只需要谐波滤波器,切换时间短;

缺点:存在鉴相频率的整数边界点杂散。

2 小数分频杂散来源

1)鉴相器产生的杂散:低鉴相频率下由电荷泵的漏电流产生,高鉴相频率下由电荷泵的源电流(Source current)和汇电流(Sink current)的适配程度决定;

2)小数频率步进杂散:瞬时相位突变调制VCO后会产生小数部分的整数倍或整分数倍的杂散,可以通过使用∑-Δ调制、增加环路滤波器的级数和添加随机性来解决;

3)整数边界点杂散:鉴相频率的谐波和VCO之间的交叉调制产生,距离整数频点越近杂波抑制越高。

3 使用可调参考源扩展无整数边界点杂散的频率范围

整数边界点杂散会影响到输出的频率的无杂散范围。如果我们使用50 MHz频率作为鉴相频率,在50 MHz的整数倍的附近都会产生整数边界点杂散,距离整数边界点越近杂散越高。使用可调参考源可以扩展无杂散的频率范围。

1)可调参考源的选择和实现方法

交替使用不同的参考源可以在较大的范围内避开整数边界点杂散。试验表明距离整数边界的2 MHz以外的频点自身交调出的杂散较小,另外环路滤波器对其的抑制也大幅增加,可以不再考虑。输出无杂散的最大范围是可调频率的最小公倍数。表1给出了几种可调参考源的组合和适用范围。在小数分频频率芯片N(整数分频数)最小值允许的情况下应该选择尽可能高的鉴相频率,因为∑-Δ调制产生的噪声随鉴相频率的升高会大幅降低,较高的鉴相频率有利于取得更好的远端相位噪声。

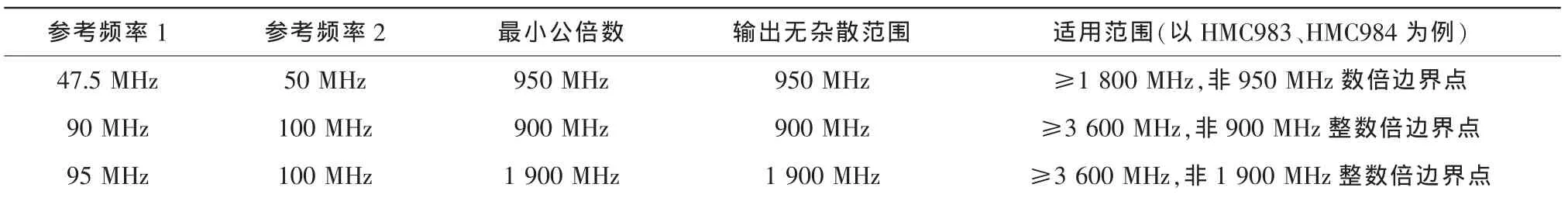

表1 可调参考频率与输出无杂范围的关系Tab.1 The relation of a tunable reference and spur free boundary

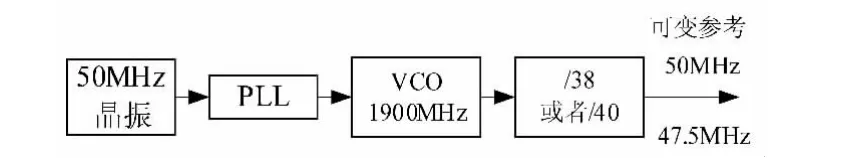

可调参考源使用Hittite公司的宽带VCO+PLL的锁相环芯片HMC830来实现[2-3],图1给出了实现47.5 MHz、50 MHz可调参考源的原理框图,在HMC830外围添加电源和环路滤波器即可实现上述方案。

图1 使用HMC830实现可变参考Fig.1 A tunable reference based on HMC830

2)可调参考源的使用对输出相位噪声的恶化

对晶振频率倍频后再分频实现可调参考的过程中,由于PLL的引入,不可避免的会恶化参考源的相位噪声。以下使用Hittite PLL Design工具分析了参考源相噪恶化的程度以及这种恶化对最终输出的相位噪声的影响。

仿真输入条件:

①使用图1中的方案产生可调参考频率,50MHz晶振的相位噪声如表2所示。

表2 使用可调参考源输出相位噪声恶化仿真结果Tab.2 Phase noise deterioration of a tunable reference

②假设最终输出频率为1 900 MHz频率;

③使用无源环路滤波器。

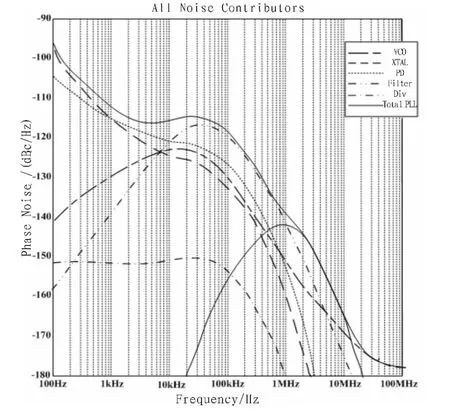

图2给出了直接将50 MHz晶振倍频到1 900 MHz附近的相位噪声曲线(芯片工作在整数模式)。

图3给出了分频后再通过FPLL倍频到1 900 MHz附近的相位噪声曲线(芯片工作在小数模式)。

表2中列举了使用可调参考与未使用可调参考的相位噪声的对比值。

根据仿真结果知道,使用可调环路会造成1~100 kHz间的最终输出的相位噪声值的恶化,但是恶化的程度不大,用轻微的相位噪声的恶化来换取输出频率的范围的大幅扩展是不错的选择,在相位噪声要求更为严格的应用中,可以通过使用更低基底噪声的PLL的芯片(eg:HMC704),配合超低相位噪声的CRO、和分频器来实现相位噪声更低的可调参考源。

3)可调参考源与小数分频环路的隔离问题

图2 晶振直接倍频后相噪曲线Fig.2 PLL of crystal oscillator phase noise

图3 使用可调参考源相噪曲线Fig.3 FPLL of a tunable reference phase noise

设计中如果可调参考源与小数分频环路的隔离不佳会导致产生可调参考源的整数PLL环路中的鉴相频率泄漏到小数分频环路中与VCO交调产生相应的杂散,导致在鉴相频率整数倍的边界点处仍然会有较高的杂散出现。增加隔离两个环路之间的隔离可以解决以上问题。需要重点考虑以下方面的问题:

①电源隔离:可调参考源环路与小数分频使用各自独立的稳压块,增加能够抑制可调参考环鉴相频率的EMC滤波器,尽量使用穿芯电容馈电;

②控制线隔离:可调参考源环路与小数分频使用各自独立的微控制器,在微控制器间之间的连线上增加能够抑制可调参考环路鉴相频率的EMC滤波器;

③空间隔离:加密隔腔之间的盖板钉,腔体间的射频信号采用同轴电缆连接。

4 小数分频的频率解析度

小数分频模式输出小数部分频率的表达式如下[4-5]:

Ffrac:小数部分的输出频率;

Nfrac:∑-Δ调制的位数的取值;

N:芯片中∑-Δ调制的最大位数;

根据上面的公式知道,输出的频率的解析度取决于鉴相频率和N值,频率越低、调制的位数越高频率解析度就越高。以100 MHz的鉴相频率为例,表3中列举了不同小数分频芯片能够达到的解析度。表3给出的解析度需要对Nfrac做四舍五入的处理,如果直接取整,频率精度会恶化一倍。

表3 小数分频的频率解析度Tab.3 Frequency resolution based on FPLL

5 小数分频的锁定检测窗口设置

温度的变化对于小数分频模式下锁定指示有一定的影响,常温下锁定的环路,在高、低温下有可能会出现锁定报失锁的情况,这就需要的合理的设置锁定检测窗口(Lock Detect Window)的值。只有当Average Phase Offset的设置值满足锁定指示发生的条件在锁定检测窗口 (Lock Detect Window)的时间内发生,锁定指示功能才能正常运行[5-6]。

下面以鉴相频率为100 MHz,输出频率为6 000 MHz左右,Icp=2 500 mA为例进行计算合理检测窗口设置;

TVCO=VCO输出周期(VCO period at the PLL feedback into the prescaler)

Fcomp=鉴 相 频 率 (The comparison frequency in the Phase Detector(PD))

PDperiod=鉴相周期(The Phase Detector period)

CPO=CP 偏置电流(Charge Pump offset current)

ICP=CP 电流(Charge Pump gain current)

Offsetavg=Average Phase Offset

Offsetnominal=Nominal Phase Offset

Geometricmean=Geometric mean calculation of optimal lock detect window

LDwindow=Lock Detect Window size

步骤1:计算最优的CPO

已知:TVCO=1/6 GHz=0.1167ns;Fcomp=100 MHz;ICP=2 500μA;

CPO=(2 ns+4·TVCO)·(Fcomp)(ICP)=666.7 μA;

根据手册CPO的最大值为635μA;

步骤2:根据CPO的设置值,计算 Offsetavg、Offsetnominal、Geometricmean

Offsetavg=(CPO/ICP)· PDperiod= (635/2500)·10ns=2.54

The nominal phase offset and geometric mean calculations take into account changes that occur in temperature(+25%for 85°C or-25%for-40°C)range and are therefore used for optimal lock detect window size selection

Offsetnominal=Offsetavg·25%=3.175ns

Geometricmean=Offsetnominal×PDperiod =5.63ns

步骤3:查表确定数字锁定窗口的设置宽度

对照表4中时间值选择6.5 ns作为锁定检测窗口的宽度。

步骤4:核实设置的窗口宽度是否满足要求

表4 HMC984小数模式下锁定指示窗口的选择Tab.4 Selecting lock detect window at FPLL mode of HMC984

高温下窗口的偏移量小于鉴相周期

LDwindow×1.25=6.5×1.25=8.125< PDperiod=10ns

低温下窗口的偏移量大于鉴相周期

LDwindow ×0.75=6.5×0.75=4.875 > Offsetnominal=3.175ns

6 试验结果

使用上述方案在6 GHz左右做带宽为600 MHz,步进为1 kHz的锁相锁,相位噪声和杂散如表5所示。

表5 C波段频综实测相位噪声和杂散Tab.5 C band Frequency Synthesizer phase noise and spur

7 结论

该设计方案简化了宽频带小步进频率综合器的设计方案,减少了传统DDS混频方案中滤波器的大量使用,给出了避免整数边界的点杂散的方法,同时由于使用了较高的鉴相频率使得环路滤波器的带宽可以适当放宽,使用普通的VCO也可以达到接近YIG振荡器的PLL相噪指标。对低成本实现高性能宽带小步进频率综合器是一种有益的探索。环境试验和实际联试考机表明该设计方案工作稳定可靠,满足设计指标要求。

[1]Alexander Chenakin.Frequency Synthesizers Concept to Product[M].Massachusetts:ARTECH HOUSE,2011.

[2]Hittite Integrated Products.HMC830 Datasheet[EB/OL].[2011-12].http://www.hittite.com/content/documents/data_sheet/hmc8301p6g.pdf.

[3]Hittite Integrated Products.HMC983 Datasheet[EB/OL].(2011-03).[2012-01].http://www.hittite.com/content/documents/data_sheet/hmc983lp5.pdf.

[4]Hittite Product Application Note.PLLs WITH INTEGRATED VCO-RF APPLICATIONS PRODUCT&OPERATING GUIDE[EB/OL].[2011-03].http://www.hittite.com/content/documents/operating_guide/synth_operating_guide_rf_vcos.pdf.

[5]Hittite Integrated Products.HMC984 Datasheet[EB/OL].[2012-01].http://www.hittite.com/content/documents/data_sheet//hmc984lp4e.pdf.

[6]Hittite Product Application Note.Lock Detect Control of PLLs-VCOs[EB/OL].[2011-03].http://www.hittite.com/content/documents/application_notes/Lock_Detet_Control_of_PLLs-VCOs_v01.0311.pdf.