DC-DC降压芯片使能保护电路的设计

张 睿

(无锡商业职业技术学院,江苏 无锡214000)

本研究涉及的DC-DC降压芯片由保护电路、第一级LDO(3.6 V)模拟供电电路、二阶温度补偿基准电路、LDO(5 V)数字供电电路、误差放大器、振荡器、高端功率管电流采样放大器、PWM比较器、PWM逻辑电路、驱动电路、低端功率管过零电流比较电路等电路单元构成。本文主要介绍了芯片的使能保护电路模块的设计。

1 使能保护电路

使能模块输入使能控制信号,控制内部各个模块工作。本设计中使能控制有两个比较判据,一个是1.5 V比较点,另一个是2.5 V比较点。电路系统启动,使能端的电位渐渐上升。当UEN小于1.5 V,整个芯片关断。当UEN超过1.5 V但小于2.5 V时,使能逻辑先使LDO(3.6 V)工作,接着第二级(带二阶温度补偿)基准电路工作,输出1.2 V的基准参考电位。1.2 V参考电位输入LDO(5V)使之工作。除了误差放大器输出COMP脚电位和SS软启动脚电位被拉到低电位,所有单元的电源供电都正常。当使能UEN大于2.5 V后误差放大器输出COMP脚电位和SS软启动脚电位释放,整个芯片正常工作。

2 1.5 V比较点的使能逻辑电路

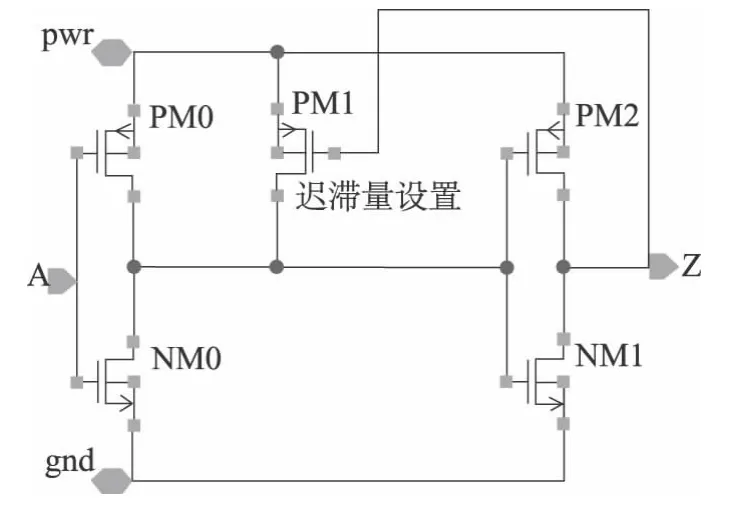

1.5 V比较点的使能逻辑电路如图1所示。设UIN=12 V,施密特触发器(如图2)I109在J351提供的7 V夹断电压下工作。当使能EN电压从0上升到1.5 V时,施密特触发器I109翻转为高电位,迟滞量为210 mV。

图1 1.5 V比较点的使能逻辑电路

施密特触发器I109输出为高电平,EN2也为高电平,去开启3.6 V和5 V的LDO。5 V的LDO给电平转换电路供电,EN1输出为高电平。EN1经过反相器X23输出L3低电平到RS_NOR触发器,锁定RS_NOR触发器,稳定EN2。

这里X23输出电平摆率为0~5 V,而RS_NOR触发器的X70供电为7 V,这会导致X23去驱动X70发生驱动电平不匹配。当芯片正常工作状态时,使能Ven肯定是高电平,X23输出为低电平,不会出现X70(nor)上下管都导通状态。而在EN电位下降到1.3 V以下,X70内部出现上下MOS管都导通的状态。如果X23输出高电平对于X70来说还是低电平,那么整个芯片就不会正常关断。设计上必需确保X23输出高电平对X70来说也是高电平。

该问题的解决方法是使电平转换电路和反相器X23都给7 V供电。

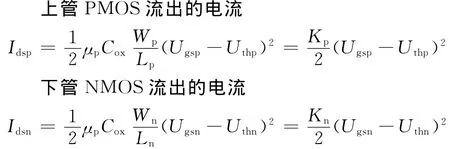

图2 施密特触发器

施密特触发器电路分析:A点高电位时,输出Z也为高电位,PM1截止。第一级反相器由PM0和NM0组成,其宽长比决定翻转电压UTF。当A点低电位时,输出Z为低电位,PM1导通。第一级反相器由PM0、PM1和NM0组成,其宽长比决定翻转电压UTR,且UTR>UTF。施密特触发器在翻转过程瞬间需要消耗较大的电流。翻转点的计算公式如下:

当Idsp>Idsn时,反相器输出高电平,当Idsp<Idsn时,反相器输出低电平。当Idsp=Idsn时,定义这时的输入电压为反相器的翻转电压。

当上管PMOS的W/L增加,Kp增大,分母变小,UA增大。当下管NMOS的W/L增加,Kn增大,分母增大,UA减小。

3 2.5 V比较点的使能逻辑电路

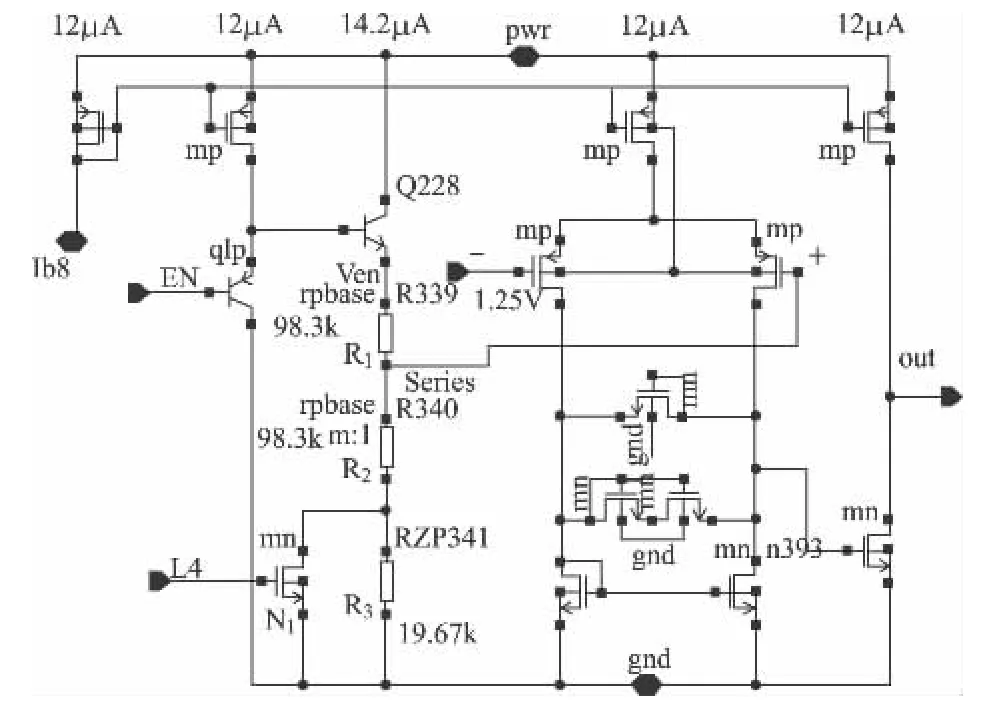

2.5 V比较点的使能逻辑电路如图3所示。2.5 V使能比较器的输出经过施密特触发器后送入与非门X89,与非门的另外两个输入信号是温度保护和欠压保护。与非门输出L4一路去保护逻辑I116,另外一路去改变2.5 V使能比较器的比较点,产生迟滞量。

图3 2.5 V比较点的使能逻辑电路

当UEN电压从1.5 V上升,内部的 LDO(3.6 V)、二阶温度补偿基准、LDO(5 V)等电路建立,使能2.5 V比较器还没有翻转,图3中的 N1(N384)开启,屏蔽掉R3。则有

设UEN关闭比较电位为2.3 V,R1=R2=100 kΩ,可以求出R3=20 kΩ。这里要注意的是,实际N1管开启时,不会将R3的压降完全拉到0,所以要求N1管的开启导通电阻小,或者是电阻支路的偏置电流小。

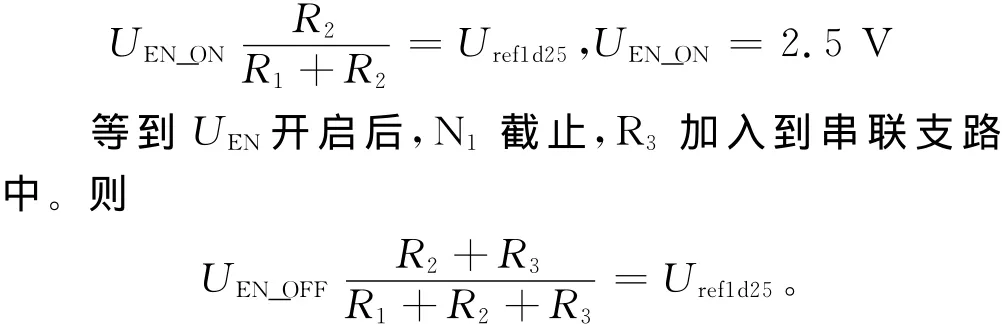

4 使能逻辑电路仿真

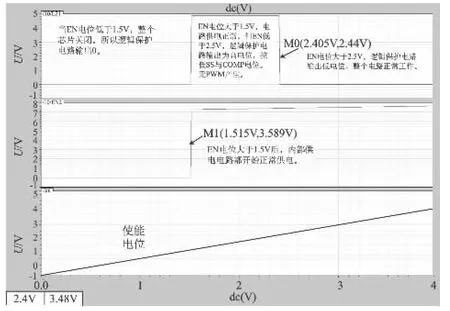

使能逻辑电路功能仿真条件:UIN=12 V,UEN电压直流扫描从0~4 V。使能逻辑电路功能仿真结果如图4所示。从图中可以看出当EN电位低于1.5 V,整个芯片关闭,逻辑保护电路输出0;当EN电位大于1.5 V,电路供电正常,但EN低于2.5 V,逻辑保护电路输出为高电位,拉低SS与COMP电位,无PWM产生;EN电位大于2.5 V后,逻辑保护电路输出低电位,整个电路正常工作。

图4 使能逻辑电路功能仿真结果

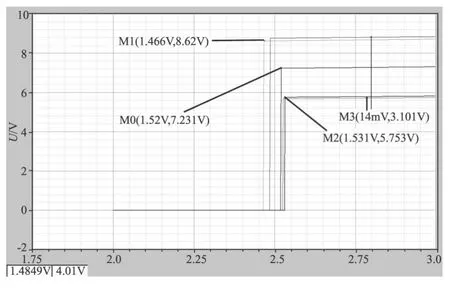

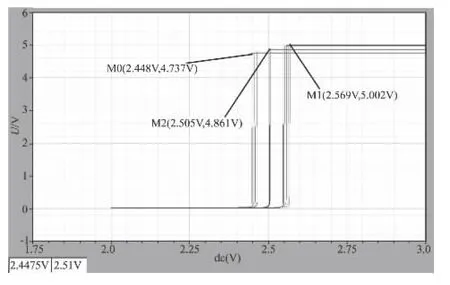

工艺角Corner仿真条件:UIN=12 V,EN电压从1~2 V按照1 mV的步进扫描。侦测使能EN=1.5 V和2.5 V开启点的范围分别如图5和图6所示。

图5 UEN=1.5 V开启点的Corner仿真

图6 UEN=2.5 V开启点的Corner仿真

5 结 论

本文主要对DC-DC降压芯片中的使能保护电路模块进行了设计,并对设计机理进行了详细阐述;针对使能电压UEN设计了1.5 V和2.5 V两个使能比较电压点,在小于1.5 V、1.5 V~2.5 V和2.5 V以上这三个电压段中分别实现芯片关断、电源供电开启和整个芯片开启等功能,同时解决了一些设计上的具体问题;最后利用1μm5 V/40 V HVCMOS工艺中的5 V低压工艺模型,在Cadence软件下验证了使能保护机理。

[1] 陈 君.电流模式DC_DC降压芯片的设计与实现[D].成都:电子科技大学,2006.

[2] 何金国.PWM DC-DC降压变换IC研究与设计[D].成都:电子科技大学,2007.

[3] 徐静萍.功率因数校正控制器过压保护电路的设计[J].西安邮电学院学报,2011,(s1):26-30.

[4] 余倩玮.单片多功能DC_DC变换器芯片设计[D].西安:西安电子科技大学,2008.