一种低功耗CMOS晶振电路设计*

彭伟娣,张文杰,谢 亮,金湘亮

(湘潭大学材料与光电物理学院,湖南湘潭411105)

随着信息科学技术的迅猛发展,低功耗设计成为集成电路发展的趋势。石英晶振振荡器作为频率标准和频率选择的“心脏”元件,被广泛应用于航天和电子技术设备中,市场对石英晶体振荡器的小型化、低功耗等指标要求也在不断提高。

传统的晶振电路采用的放大器是反相器并联大电阻模型。反相器在电源电压为P管和N管的总阈值之和、且P管和N管同时偏置在饱和区时的工作状态最佳,只消耗较低的电流。一旦电压超过这个值,电路工作状态将变差,整体电路将消耗更多的电流;一旦电压低于这个值,晶振电路将停止振荡[1-2]。

本文致力于设计一种低功耗晶振电路,晶振内部的反相器在电源电压低于P管和N管的总阈值之和时也能正常工作,P管和N管同时偏置在饱和区。整体电路消耗的电流低于传统晶振电路消耗的电流。

1 电路分析

1.1 传统晶体振荡电路的设计与分析

1.1.1 石英晶体的等效电路

石英晶体的等效电路如图1所示。

图1 石英晶体的等效模型

当等效电路中的L、C、R支路产生串联谐振时,该支路呈阻性,等效电阻为R,谐振频率为

当f<fs时,C0和C电抗较大,起主导作用。石英晶体呈容性。当f>fs时,L、C、R支路呈感性,将与C0产生并联谐振,石英晶体呈纯阻性,谐振频率

当f>fp时,电抗主要决定于C0。石英晶体电抗的频率如图2所示,只有在fs<f<fp的情况下,石英晶体才呈感性。

图2 石英晶体的电抗频率特性

1.1.2 传统Pierce CMOS晶振电路

传统的Pierce CMOS晶振电路如图3所示,在反相器的输入、输出端并联反馈电阻。反馈电阻将反相器钳制在放大区,此时的反相器等效为放大器,同时引进直流偏置。将石英晶体作为高Q值谐振回路元件接入正反馈电路中,组成晶振电路。Pierce CMOS晶振电路采用石英晶体决定晶振电路的频率。因为石英晶体的高标准性和高品质,可以使石英晶振电路获得极高的频率稳定性。

图3 Pierce CMOS晶振电路

对于选定的频率,晶振电路必须满足“巴克豪森”准则才能起振。“巴克豪森”准则表示为

当环路总相位移为360°的整数倍,环路增益大于或等于1为晶振电路的起振条件。图3中的等效放大器提供180°相位移,石英晶体和两个微调电容组成反馈电路,它们提供剩下的180°相位移,满足条件(4)。由于等效放大器的作用,振幅开始增大,但振荡幅值的增长过程不会无止境地延续下去,因为放大器的线性范围有限,随着振幅的增大,放大器逐渐由放大区进入饱和区或截止区,工作在非线性的甲乙类状态,其增益逐渐下降。当放大器增益下降导致环路增益下降到1时,振幅的增长过程停止,振荡器达到平衡状态,即进入等幅振荡状态。

对于Pierce CMOS晶振电路,反相器中P管和N管的跨导gm之和必须满足在一定的范围内,晶振电路才能起振。可以根据晶体等效模型参数设计P管和N管的宽长比,使gm值在相应的起振范围之内[3]。

2 低功耗晶振电路设计

2.1 加串联电容的晶振电路

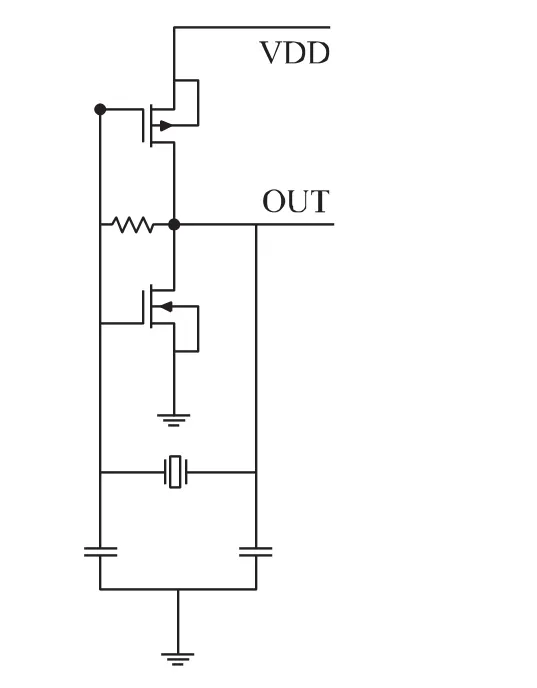

如图4所示,新型晶振电路在传统Pierce CMOS晶振电路中添加电路1、电阻R2和串联电容C0。

图4 加串联电容的晶振电路

传统的反相器,P管的栅端与N管的栅端相连,两者的栅端电压相等。反相器在电源电压等于P管和N管的阈值电压之和、P管和N管同时偏置在饱和区时的工作状态最佳,且消耗的电流较小。P管和N管的栅端加入串联电容C0后,P管和N管的栅端电压一直相等的条件则不存在,两管的偏置相对独立。N管的漏端和栅端之间连接大电阻,相当于二极管连接,所以N管被一个N管的阈值电压偏置。如果此时P管恰好被一个P管的阈值电压偏置,则P管和N管可以同时偏置在饱和区,同时电源电压小于P管和N管的阈值电压之和。

电路1为一个常见的基准电路,相当于电流镜模块,只需要较小的开启电流。I1、I2分别为P1管和P2管的漏电流。从本质而言,I1被“自举”到I2,从而确定I1。因为每个二极管方式连接的器件都是由一个电流源驱动的,所以相对来说,I1和I2与VDD无关。所以VDD在2.7 V~5 V间变化时,I1和I2变化范围不大,在设计低功耗晶振电路时,设计相应的参数,保证电路1部分消耗的电流最小,提供稳定的偏压偏置后续电路。

N2管的漏电流I2将P2管的源漏电压钳制为一个P管的阈值电压。P2管的栅端电压通过大电阻R2连接P3管的栅端,所以P3管也被一个P管的阈值电压偏置。同时N3管由于R3的作用,被一个N管的阈值电压钳制在饱和区。在VDD的值小于P管、N管的阈值电压之和时,P3管和N3管都能钳制在饱和区,且消耗最低的电流。

2.2 低功耗晶振电路设计

低功耗晶振电路在前述电路模块中加入缓冲模块和滤波电容保证其稳定性和高效性,设计电路如图5所示。在镜像电路模块和晶振模块之间用缓冲器模块连接,P4和N4组成反相缓冲器,由镜像电流开启。C3电容有滤波的作用,防止晶振起振后P4管栅端电压的快速变化对P3管的影响。R4和R5分别连接P3管和N3管的源端,这些电阻起到限制漏电流的作用,在一定程度降低晶振电路的功耗。P4的源端连接P3的源端,所以P3管的偏置电压值也为一个P管的阈值电压,同时R3偏置N3管,N3管的偏置电压值等于N管的阈值电压。所以P3管和N3管都被偏置在饱和区。设置合适的R4和R5,在减小漏电流的同时使P3管的源端和N3管源端之间的电压小于P管和N管的阈值之和,使整体电路的功耗降低。

图5 低功耗晶振电路

设置合理的P3管和N3管的宽长比,使其的gm值之和在起振范围之内。在仿真此低功耗晶振电路时,需要提供一个外界的干扰作用才能起振。一般将高电源以上电的形式实现,或者在组成晶振电路的电感模型中加入初始电流。

3 版图

低功耗晶振电路的版图如图6所示,为了防止静电对芯片造成伤害,在高电源、低电源、输入、输出四个端口分别加上相应的ESD保护电路。

图6 晶振电路版图

4 仿真结果

以晶振频率为32.768 kHz的晶振电路为例,整体功耗如表1。在VDD在2.7 V~5 V之间,晶振电路能正常工作,而且消耗的功耗电流低于750 nA。

表1 晶振电路功耗电流

在高电源VDD为2.7 V、常温、TT的情况下,低功耗晶振电路的仿真曲线如图7所示。图7中上栏曲线表示高电源VDD的电流幅度变化曲线,下栏曲线表示晶振电路输出端口XTO的输出波形曲线。

由图7可知,晶振电路起振时间为1 s左右,高电源VDD的电流幅度最大值不超过1 μA。

图7 晶振电路的仿真波形

5 结论

本文提出的低功耗晶振电路,在电源电压在2.7 V~5 V之间都能够起振,而且整体功耗电流小于750 nA。低功耗晶振电路可提高产品性能、降低使用成本、提高市场竞争力,所以低功耗晶振的电路提出和研究具有较高的实用价值。

[1]Werner Thommen.An Improved Low Power Crystal Oscillator[C]//Proc ESSCIRC’99,1999,146-149.

[2]Daniel Aebischer,Henri J Oguey,Vincent R von Kaenel.A 2.1 MHz Crystal Oscillator Time Base with a Current Consumption under 500 nA[J].IEEE J Solid-State Circuits,1997,32:999-1005.

[3]Andreas Rusznyak.Start-up Time of Cmos Oscillators[J].IEEE Transactions on Circuits and Systems,1987,cas-34(3):- .

[4]Vittoz E,Fellrath J.CMOS Analog Circuits Based on Weak Inversion Operation[J].IEEE J Solid-State Circuits,1977,sc-12:224-231.

[5]Vittoz E,Degrauwe M,Bitz S.High-Performance Crystal Oscillator Circuits:Theory and Applications[J].IEEE J Solid-State Circuits,1988,sc-23:774-783.

[6]Eric Vittoz.Low-Power Crystal and Mems Oscillators[M].Springer,2010.

[7]曾健平,王阆,何先良.石英晶体振荡器的集成化设计[J].微电子学与计算机,2009,26(2):30-32.

[8]赵声衡.晶体振荡器[M].科学出版社,2008.

[9]赵旭昊,安凌凌,孟令琴.0.18 μm 12 GHz CMOS八分频电路设计[J].现代雷达,2007,29(8):109-111.

[10]Jankovic M,Brannon A,Breitbarth J,et al.Design Method for Low-Power,Low Phase Noise Voltage-Controlled Oscillators[J].Microwave Integrated Circuit Conference,2007:199-202.

[11]Wan Wengang,Zheng Wen-qiang,Ye Lin.Development of Minitype Low-Power Consumption Quartz Crystal Oscillators[J].Piezoelectricity,Acoustic Waves,and Device Applications(SPAWDA).2009:121.

[12]ElBarkouky M,Wambacq P,Rolain Y.A Low-Power 6.3 GHz FBAR Overtone-Based Oscillator in 90 nm CMOS Technology[C]//Microelectronics and Electronics Conference,2007:61-64.