0.13 μm铜互连工艺鼓包状缺陷问题的解决

张 磊 ,朱亦鸣

(1. 上海交通大学微电子学院,上海 200240;2. 中芯国际半导体制造有限公司工艺集成部,上海 201203;3. 上海理工大学上海市现代光学系统重点实验室,上海 200093)

1 引言

随着半导体技术日新月异的发展,晶体管的尺寸变得越来越小,因此铜互连技术在半导体制造中的应用也越来越普遍[1]。铜互连有很多优点:铜的电阻率仅为1.67 μΩ.cm,远小于铝的2.66 μΩ.cm,同时能减少互连层的厚度,通过降低电容达到了减少信号延时的效果[2]。因此,如果配合采用低K电介质材料,可以降低信号之间的耦合电容,信号的转换速度也随之加快,即进一步降低了信号的延时[3]。

半导体制程中会有各种各样的鼓包状缺陷(bubble defect),这种缺陷通常都是由于薄膜鼓起形成一个鼓包状的东西而得名的,而鼓起的鼓包薄膜一般比较薄,如二氧化硅或是氮化硅薄膜,而最常见的是光阻剥除过程中产生的。这种鼓包状缺陷通常被发现在有源区的两端,缺陷尺寸从0.2~8 μm不等。造成鼓包状缺陷的原因是由于硅片上面的一层薄氧化层的膨胀引起的空洞缺陷。它不仅会使金属连线断裂,而且会由于空洞的形成而产生压力空洞。这个在金属和电介质层间的界面鼓包会产生较大的机械压力。金属会沿着晶格边缘来释放压力。这个压力空洞会导致电路开路或是由电迁移引起的连线失效。在亚微米制程中,鼓包状缺陷除了会引起金属层的失效外还会造成可靠性的问题[4],因此具有很大的研究价值。

在实际的生产过程中,我们在0.13 μm及以上制程的产品出货前的目检中发现,顶层金属层会出现一种鼓包状的缺陷,这种缺陷会造成金属层的断裂,因而会造成产品可靠性的问题。进一步的研究表明,这种鼓包状的缺陷是由于顶层金属层下面蚀刻阻挡层氮化硅从界面掀起而造成的,它会导致电路金属连线的失效和可靠性问题。

在之前的研究中,0.13 μm制程中发现的出现在顶层金属层的鼓包状缺陷,通过切片可以看到是由于金属层下面的介质层的顶起所造成的,而经过铜的淀积之后,会使这种鼓包状缺陷突显放大出来,从而在光学显微镜下(OM)就能很容易看到[5]。之前的研究发现出现鼓包状缺陷的电介质层已经被蚀刻变形,因此认为是由于沟槽蚀刻过程中的蚀刻率太大,破坏了通孔的形状而引起的,最终导致在连线层中鼓起一个鼓包状的缺陷[6]。因此针对这一现象和原因,可以通过调整蚀刻率来解决。但是,在之后的研究中发现,单纯地调节蚀刻率并不能从根本上防止鼓包状缺陷的产生,鼓包状缺陷仍然会不时出现,并且如果为了解决这种缺陷而把蚀刻率调得较低的话会引起其他的缺陷效应,比如在晶圆边缘不够蚀刻的现象[7]。因此,为了完全解决这种鼓包状缺陷,需要结合制程中其他步骤一起来考虑它的产生机理,找到真正的原因,从而从源头上解决这种缺陷。

本文通过进一步的研究发现,这种鼓包状的缺陷是由蚀刻阻挡层氮化硅薄膜的凸起而产生的,蚀刻率只是引起它产生的其中一个因素,同时它还和电路图形的分布、有机介质(BARC)的涂布有关,因此根据它的产生机理和原因,再结合工艺过程的实际情况,可以通过调整并控制铜金属连线层间氧化电介质层的蚀刻速率,改变有机介质层的沉积方法,以及改进产品电路设计的检验规则(DRC)这三种方法来防止这种鼓包状缺陷的产生,从而根本上解决铜互连工艺中鼓包状缺陷的问题,最终提高产品的可靠性和成品率。

2 问题分析

2.1 问题描述

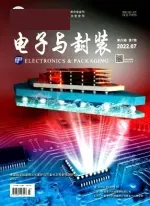

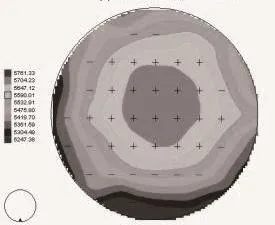

在0.13 μm及以上制程中,一般采用铜大马士革互连工艺。大马士革工艺是首先在电介质层上刻蚀出金属导线用的图形,然后再填充金属,再对金属进行金属机械抛光,重复上述工序,进行多层金属叠加。铜大马士革工艺中的电介质蚀刻采用的是等离子体蚀刻,等离子体蚀刻的优点之一在于它运用光学系统自动为刻蚀制程订立刻蚀终点。在铜制程中,氮化硅薄膜就是被用来作为刻蚀的终止层而沉积的。在对顶层金属层进行电介质层蚀刻并淀积铜后,对晶圆进行缺陷扫描,会在晶圆的中心发现一种凸起的鼓包状缺陷,如图1所示。

图1 金属淀积后缺陷扫描图和显微镜照片

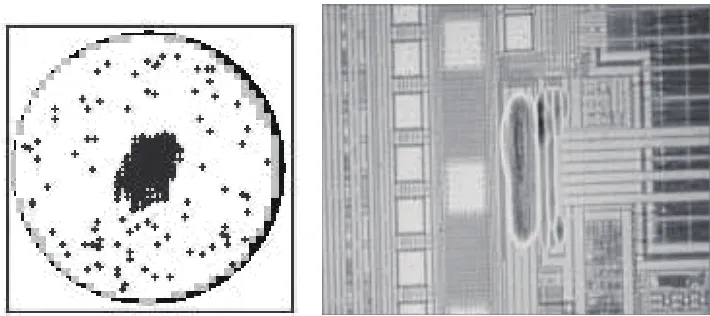

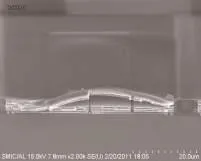

进一步使用电子扫描显微镜(SEM)和聚焦离子束(FIB)对金属表面的鼓包进行切片观察,了解其结构。图2是金属表面鼓包在SEM切片下的照片,图3是在FIB切片下的照片。

图2 金属鼓包状缺陷SEM照片

图3 金属鼓包状缺陷FIB照片

在电子扫描显微镜下可以看到金属表面的鼓包是由金属层下面的介质层掀起造成的,由FIB的照片可以更清晰地看到,这其实是由氮化硅薄膜从界面掀起形成的鼓包,而且可以看到,氮化硅层掀起的地方都是在通孔图形的密集区域。氮化硅薄膜具有很强的扩张应力,在工艺制程中的热反应会加剧应力的扩张,从而也会促使氮化硅层与下面界面的分离。同时,我们还发现这种鼓包状缺陷固定出现在晶圆的中心,这与铜制程蚀刻中晶圆中心的蚀刻率会比边缘要快的效应是相一致的。由此我们可知,当高密集的通孔图形区域加上氮化硅层热效应的累积以及蚀刻速率的不均匀性就会形成这种会导致金属互连层间的断裂、从而使金属连线失效的鼓包状缺陷。

2.2 铜大马士革制程结构的分析

铜互连工艺最早是在1997年9月由IBM提出来的,被称为是镶嵌工艺(也称大马士革)。它采用对电介材料的腐蚀来代替对金属的腐蚀以确定连线的线宽和间距[8]。大马士革工艺最大的特点是不需要金属层的蚀刻。氮化硅薄膜已经被研究并用作降低铜制程中的电容干扰材料[9]。铜大马士革工艺首先是在半导体上沉积一层30~70 nm厚的氮化硅作为铜扩散阻挡层和刻蚀终止层,然后沉积一层厚度在300~800 nm的电介质层,接着在上面沉积32 nm的二氧化硅作为光刻曝光的抗反射层,然后依靠光刻、显影、等离子体蚀刻定义出通孔形状。在已形成的通孔内及电介质层表面涂布一层底层抗反射层作为金属线槽介质层的蚀刻终止层,对其进行烘烤、蚀刻使其达到需要形成的大马士革上层金属导线槽介质层的厚度并停在大马士革通孔介质层表面,再通过光刻、显影、等离子蚀刻和光阻剥离最终形成大马士革上层金属导线槽介质层。最后通过铜的电镀和平坦化处理,最终实现铜互连,大马士革结构如图4所示。

铜制程中,氮化硅材料薄膜因其特殊的性能在半导体制造中担任着很重要的角色,对其性能的研究可以很好地帮助我们解决铜互连生产中所遇到的问题[10]。本论文所要研究的铜制程中鼓包状缺陷的产生,与氮化硅材料密不可分。

图4 铜大马士革结构图

2.3 鼓包状缺陷形成原因的分析

高密集的通孔图形区域加上氮化硅层热效应的累积以及蚀刻速率的不均匀性是形成这种会导致金属互连层间的断裂从而造成金属连线失效的鼓包状缺陷的机理,而在半导体制造中以下三个过程是这种缺陷形成的原因所在。

2.3.1 有机介质层涂布的不均匀性

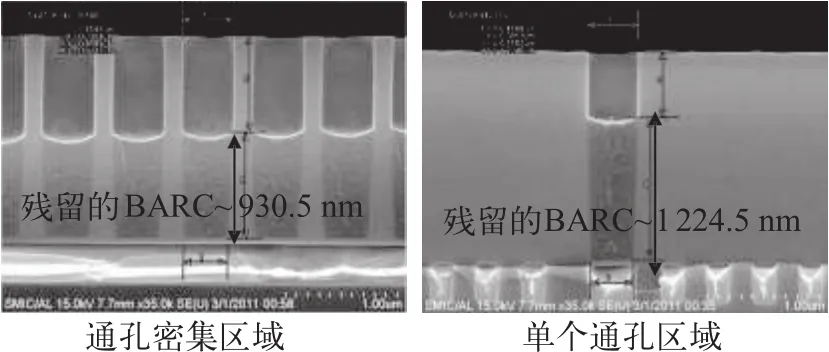

首先在氧化电介质层通孔蚀刻后,需要涂布一层有机介质层作为沟槽蚀刻的阻挡层。由于通孔图形的疏密性分布,在通孔比较密集的区域,BARC涂布的厚度会比通孔图形少的区域薄。这样,在BARC回蚀后,在通孔密集的区域残留的BARC要远远少于通孔稀疏的区域,如图5所示。

图5 在通孔的疏密不同区域有机介质层的不均匀性涂布

这样,在BARC蚀刻之后,通孔密集区域中残留的BARC就会比单个通孔区域中的少。

2.3.2 蚀刻率的不均匀性

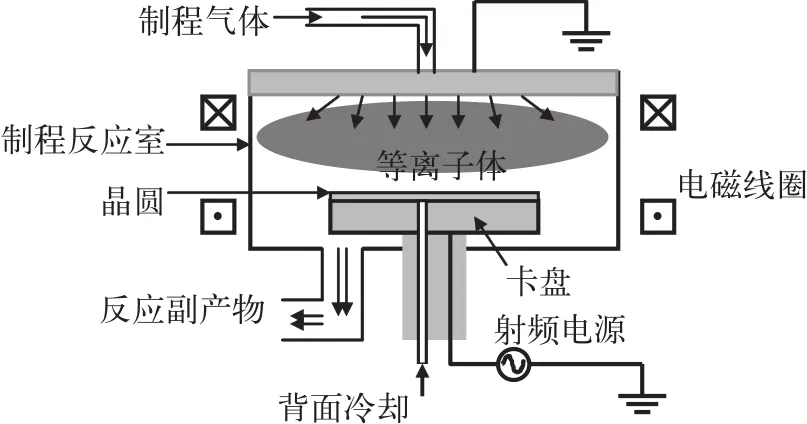

20世纪80年代以后,当图形尺寸小于3 μm时,等离子体刻蚀就逐渐取代了湿法刻蚀而成为所有图案化刻蚀制程所采用的技术[11]。所以,在0.13 μm制程中的电介质层采用的是等离子体(干法)刻蚀[12]。在等离子体刻蚀制程中,首先将刻蚀气体注入真空反应室中。当压力趋稳后再利用射频功率产生辉光放电的等离子体。部分的刻蚀剂分子在受到高速电子的撞击后会分解而产生自由基(Radicals)。接着自由基就会扩散到边界层下的晶圆表面并被吸附[13]。在离子冲击的帮助下,这些自由基很快会和表面的分子或原子发生反应并且形成气态的副产品。从晶圆表面脱附而出的易挥发性副产品又会扩散穿过边界层而进入对流气体中,并从反应室中排出。图6所示为等离子刻蚀系统示意图。

图6 等离子刻蚀系统示意图

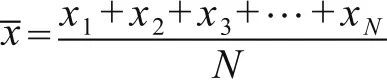

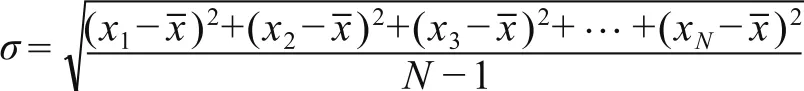

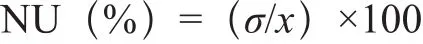

随着元件尺寸的不断缩小,在单片晶圆上对刻蚀均匀性的标准也越来越高。一般来说,晶圆内均匀性是在晶圆上由测量刻蚀制程前后特定点的厚度,并计算这些点的刻蚀速率而得的。若它们是 x1、x2、x3、…xN,则所测量点的平均值为:

标准的测量偏差为:

标准的偏差不均匀性(百分比)可定义为:

而刻蚀速率由下式来计算:

刻蚀速率x=(蚀刻前厚度-刻蚀后厚度)/刻蚀时间0.13 μm制程中的电介质刻蚀制程,主要是二氧化硅和氮化硅的刻蚀制程,通常采用的是损伤机制的等离子体刻蚀[14]。它们是较为倾向物理刻蚀的反应式离子刻蚀(Reactive Ion Etch,RIE)制程。而使用损伤机制的刻蚀制程若要增进其非等向性的刻蚀轮廓就必须增加离子轰击[15]。在低压和高射频功率下采用重度离子轰击,我们能得到接近理想的垂直刻蚀轮廓。从图7的等离子刻蚀系统示意图中可以看出,等离子体(Plasma)在反应室中的分布以反应室中心最为密集,从而会使得刻蚀的蚀刻率呈现晶圆比边缘快的现象,如图8所示。

图7 等离子刻蚀率分布图

由2.3.1可知,由于BARC涂布的不均匀性,在BARC回蚀刻后,密集通孔区域中残留的BARC一定会比稀疏通孔区域的少。结合等离子体蚀刻具有中心蚀刻率比边缘快的特点,当中心蚀刻率太大以致密集通孔区域内残留的有机介质层BARC不够阻挡而蚀刻到电介质层,从而会导致沟槽蚀刻后密集通孔区域的通孔形状发生异常,如图8所示。最终就会在淀积铜之后,导致氮化硅层承受不住过大的应力而从界面剥落,形成鼓包状缺陷。

图8 沟槽蚀刻后通孔在疏密不同区域的形状

2.3.3 氮化硅层的大应力效应

氮化硅(Si3N4)薄膜主要起腐蚀布线沟槽时腐蚀阻挡层作用,也可以阻挡铜的热扩散,在铝互连线中,金属或介质层的蚀刻停止在阻挡材料层上,通过适当的过蚀刻可以使刻蚀均匀。而在大马士革工艺中,如果不在穿通孔和布线介质层间加入蚀刻阻挡层,蚀刻深度难以控制。蚀刻过度会引起空洞,即穿透介质层;蚀刻不足又会影响铜的淀积[16]。有了氮化硅阻挡层后,通过过蚀刻,就可以获得较均匀的刻蚀深度,但是氮化硅的介电常数很高,所以应尽可能的薄,以免增加层间的电容。

在0.13 μm制程中,一般采用等离子体增强化学气相沉积方法(Plasma-enhanced Chemical Vapor Deposition,PECVD)来沉积氮化硅薄膜。等离子体增强化学气相沉积(PECVD)氮化硅薄膜具有良好的绝缘性、致密性、稳定性和对杂质离子的掩蔽能力,所以被广泛地当作阻挡层和刻蚀终止层运用在0.13 μm铜互连半导体制程中[17]。

氮化硅-氧化硅-氮化物-氧化物的堆叠层在铜制程大马士革工艺中,可以在一个以硅烷为基础的反应室中以临场沉积的方式在一个程序中完成[18]。藉着输入硅烷(SiH4)、氨气(NH3)、氮气(N2)以及激发等离子体,我们可以沉积一个很薄的氮化硅密封层(Seal Layer)(50~100 nm)。形成这个密闭层是很重要的,它可以防止铜扩散进入氧化层和最终进入硅基片而造成晶体管性能的不稳定。密封的氮化硅层也可以在氧化物沉积期间防止铜的氧化。不像铝金属,铜的氧化物是一种松散膜层,它无法自行停止铜的氧化步骤(这与铁的生锈相似)[19]。

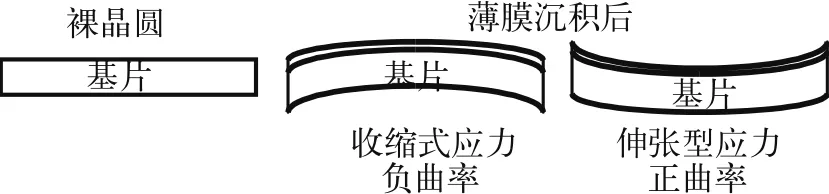

氮化硅薄膜是一种物理、化学性能均非常优秀的半导体薄膜,具有高的介电常数,可靠的耐热抗腐蚀性能和优异的机械性能等。因此,在半导体制造中常被用作密封层、刻蚀终止层和表面钝化层等。而目前用等离子体增强化学气相沉积(PECVD)的氮化硅薄膜,都会使氮化硅薄膜处于某种应力状态。当氮化硅薄膜处于过大的伸张型应力(Tensile(positive)Stress)状态时,就会引起开裂;处于过大的收缩式应力(Compressive(negative)Stress)状态时,会引起褶皱或剥落。这些应力问题不仅会削弱氮化硅薄膜原有的绝缘、钝化、密封效果,而且还会直接影响到半导体器件的机械性能[20]。

图9 收缩式应力和伸张型应力的定义

从前文2.3.1和2.3.2所述的鼓包状缺陷产生的原因可知:当在通孔疏密不同的区域BARC涂布会有不均匀现象,从而使得在BARC蚀刻之后,通孔密集区域内残留的BARC会较少。同时,结合沟槽蚀刻有晶圆中心比边缘蚀刻率快的效应,导致沟槽蚀刻后密集区域内通孔的形状发生异常。最后在淀积铜之后,如图10所示,由于通孔密集区域通孔形状发生了异常,致使在此区域中淀积大块的长条状的铜之后,氮化硅层会因承受过大的应力,从而引起氮化硅层从界面剥落和断裂,即在晶圆表面形成鼓包状缺陷。

图10 通孔疏密不同区域淀积铜示意图

3 鼓包状缺陷问题的解决

3.1 提高BARC涂布的均匀性

由于有机介质层在通孔疏密不同区域涂布的不均匀性,结合沟槽蚀刻率的不均匀性,导致在电介质层的沟槽刻蚀后影响密集通孔区域的图形形状,从而导致鼓包状缺陷问题的产生。所以,通过设计BARC涂布实验,发现了一种优化BARC涂布的方法——BARC两次涂布法,即重复涂布两次BARC。两次涂布的程序完全一样是为了更大化地均匀BARC涂布的厚度,从而使得在密集通孔区域残留的BARC能有效地阻挡沟槽刻蚀,以使在刻蚀后能保持通孔图形的形状,最终抑制和改善鼓包状缺陷问题的出现。

BARC两步法的步骤:BARC涂布→BARC回蚀刻→再BARC涂布→BARC回蚀刻。

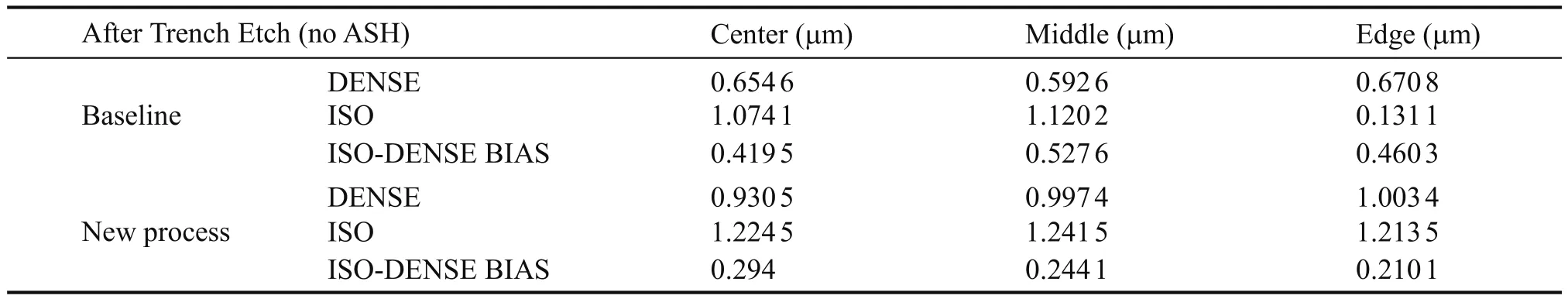

实验内容:选取两片有相同通孔图形的晶圆,一片涂布一次BARC,另一片用两次BARC涂布法涂布,然后在晶圆的中心、中间和边缘三个位置分别对密集通孔,单个通孔测量残留在通孔中的BARC厚度,实验数据如表1所示。

表1 新旧BARC涂布方法下在BARC回蚀刻后通孔内残留的BARC厚度数据表

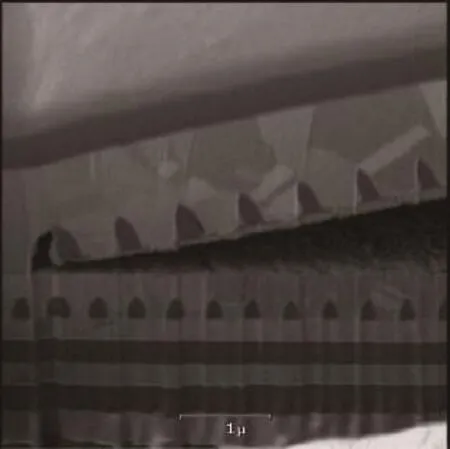

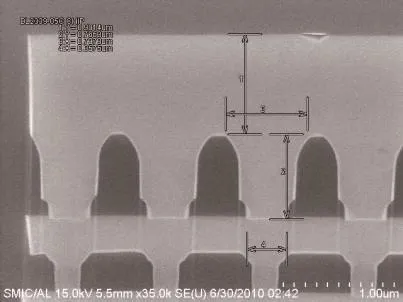

从表1可以看出,用两次BARC涂布方法能有效将在疏密不同区域通孔内BARC的残留厚度之间的差异从0.419 μm改善到0.294 μm,从而大大地均匀化了BARC涂布的厚度,进而在沟槽蚀刻后使得密集通孔区域内的BARC能有效保护通孔的形状不被刻蚀变形,这样就能防止Bubble defect的产生。图11所示为用两步BARC涂布之后的在通孔疏密不同区域内残留BARC厚度的电子扫描显微镜切片图。

3.2 改善蚀刻率

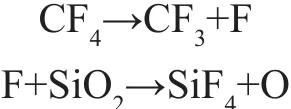

利用等离子体可在半导体制造中进行快速刻蚀,但其工艺参数射频功率、极板功率、自偏压、气体流量和气压对刻蚀率有很大影响[21]。藉由增加离子轰击可以提高刻蚀速率,并且更重要的是能改善方向性的刻蚀。而为了增加离子轰击,我们可以通过增强射频功率并降低气压来实现。大多数的电介质刻蚀制程都使用带有重度离子轰击的氟元素,利用破坏机制来完成非等向性刻蚀轮廓。电介质刻蚀最常用的气体是氟碳气体,在正常情况下,碳氟化物相当稳定且不会和二氧化硅或硅化物起反应。在等离子体中,碳氟化物会分解并产生会引起高度反应的氟元素自由基。这些自由基和二氧化硅或氮化硅产生化学反应,并在表面上形成具有挥发性的四氟化硒。等离子体刻蚀中的二氧化硅的化学反应式:

可以通过控制沟槽蚀刻的蚀刻速率来降低蚀刻对通孔图形形状的影响。由图7可见,一般蚀刻的蚀刻率在一片晶圆上分布是不同的,通常在晶圆中心的蚀刻率会较大,因而也更容易产生过蚀刻的现象。一旦有过蚀刻现象出现,就会破坏通孔的形状,最后导致在铜淀积后由于氮化硅阻挡层承受不了过大的应力而从铜界面掀起,在铜表面产生凸起状鼓包的缺陷。所以通过实验降低沟槽电介质层的蚀刻速率,使在晶圆中心不产生过蚀刻现象,就能很好地抑制凸起状鼓包缺陷的产生。

图11 两步法BARC回蚀后的厚度

在半导体等离子体蚀刻制程中,我们一般不会轻易去调整蚀刻率,因为一旦一个机台的蚀刻率改变后,在这个机台上跑货的所有产品都会受到影响,而为了不影响其他产品的跑货条件,我们可以通过按产品来调整蚀刻时间,当蚀刻率高时,我们可以减少蚀刻时间,而当蚀刻率太低时,可以增加蚀刻时间,从而达到预期的效果[22]。本论文涉及的鼓包状缺陷是由于蚀刻率太快引起的,所以可以通过降低蚀刻时间来解决。

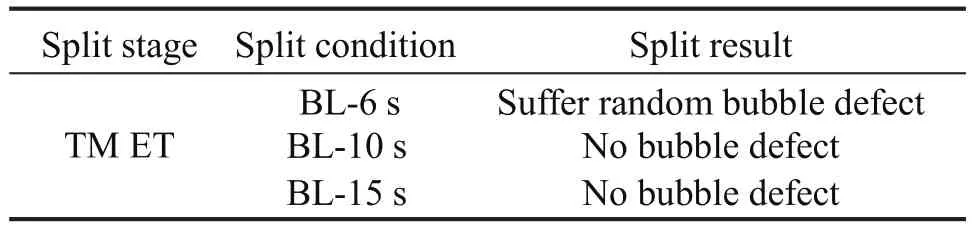

表2 顶层金属蚀刻主蚀刻时间实验表格和结果

表2是通过减少顶层沟槽电介质层的主蚀刻(OE)时间所得到的结果。可以看出,当降低顶层金属层沟槽的蚀刻时间至10 s时,就能有效阻止鼓包状缺陷的产生。通过进一步实验结果的比较和分析,如图12所示,减少顶层金属层的蚀刻时间10 s,能得到理想的通孔图形。

图12 减少10 s顶层金属层的蚀刻时间后的顶层通孔图形

3.3 从电路图形设计规则检验(DRC)方面来预防

DRC(Design Rule Check)是验证设计的几何规则的,它保证版图符合流片厂家的要求,可以保证版图在工艺线上确实可以做出来。事实上,如果不作这一步验证的话,就有可能发生线条在光刻过程中被刻断等情况,从而导致流片失败。

版图文件是可以直接交给半导体加工工厂生产的。但是,在交付厂商之前必须做DRC 验证。因为,为了保证版图能正确制出,流片厂家会根据工艺定义很多的设计规则,只有版图满足厂家所有的设计规则,才可能被正确地制出。一般说来,设计规则有很多,例如:最小间距、最小孔径等。不符合厂家提出的设计规则要求的版图在工艺线上是不可能被正确生产出来的。

本论文所要解决的鼓包状缺陷,总是出现在晶圆的特定图形位置上,而且只有某些有特殊电路图形的产品才会有这种现象,这就说明这种缺陷的发生是与产品的设计(Layout)有密切关系的,所以在做DRC验证时就制定出避免设计出会产生凸起状鼓包缺陷的特殊电路图形的设计规则,从源头上抑制这种鼓包状缺陷的产生。

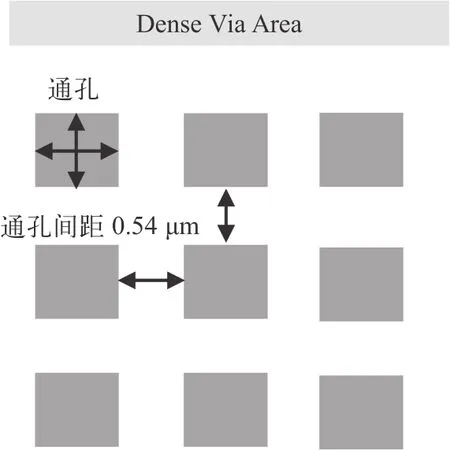

对本论文所要解决的鼓包状缺陷所出现的固定图形区域的电路图形进行归纳总结,发现有以下三点共同点:

(1)鼓包状缺陷都是出现在大块的顶层金属区下的密集通孔区域;

(2)顶层通孔区内通孔之间的距离都很小;

(3)顶层通孔区域内的通孔很多,百分比大于30%。

根据以上三个产生鼓包状缺陷的电路图形的共同点,我们制定如下检验规则:在顶层通孔阵列区域大于或等于3×3时,通孔与通孔间的最小距离为0.54 μm,如图13所示。

通过DRC定义出顶层通孔间的最小距离,即减小了单位面积上的通孔百分比,避免过于密集的通孔区域产生,从而使得BARC能较均匀地涂布在整片晶圆上,继而在后继的沟槽蚀刻过程中不会出现由于BARC不够挡的过蚀刻现象,保持了顶层通孔图形的形状,最终避免了鼓包状缺陷的产生。

图13 顶层通孔最小间距DRC规则

4 结论

造成0.13 μm铜制程中鼓包状缺陷问题的原因:一是由于有机介质层涂布在顶层通孔层的疏密不同区域会呈现不均匀性,会导致有机介质层蚀刻后,在密集通孔区域内作为阻挡沟槽蚀刻的残留的BARC较少;二是在晶圆中心,蚀刻的蚀刻率会比边缘快。这两个因素叠加在一起,就会导致在顶层沟槽蚀刻完后,顶层通孔层的密集通孔区域的通孔形状发生异常。在淀积铜之后,氮化硅阻挡层因承受不住过重的应力而从界面掀起,从而导致淀积在氮化硅之上的顶层金属层鼓出一个鼓包样的缺陷。

本文针对鼓包状缺陷的产生原理,根据工艺生产的实际情况,提出了均匀化顶层通孔内有机介质层BARC的厚度,尽可能地减少密集通孔和单个通孔内BARC厚度的差异性,并通过改变顶层沟槽电介质层蚀刻的时间来防止鼓包状缺陷的产生。在实验后得出BARC两步沉积法和减少10 s的顶层沟槽蚀刻时间的结果。并根据鼓包状缺陷产生的图形特点,制定出相应的DRC规则,规定出在顶层通孔密集通孔区内最小通孔间距离0.54 μm的结果,从电路设计上防止了鼓包状缺陷产生的可能性。鼓包状缺陷问题的解决使产品的成品率上升,取得了良好的经济效果。

[1] 王阳元,关旭东,马俊如. 集成电路工艺基础[M].1991.

[2] Michael Quirk, Julian Serda.半导体制造技术[M]. 北京:电子工业出版社,2004.

[3] 黄浩. 半导体金属互连集成技术的进展与趋势[J]. 金属热处理,2004,(8)∶ 26.

[4] K P Lin, C D Chang, K S Huang, S L Hsu. A Study of stress voiding effect on ALSiCu metal bank allowed lifetime for IC foundry fabs Proc[C]. IEEE International Integrated Reliability Workshop,1998.

[5] 宋登元,宋晓萍. 集成电路铜互连及相关问题的研究[J].半导体技术,2002,(2)∶ 29-30.

[6] de Bruin L, van Laarhoven J M F G. Advanced multiplestep resist etchback planarization [C]. International IEEE VLSI Multilevel Interconnection Conference, 1988∶404-410.

[7] Ciovacco F, Alba S, Fazio G, Somboli F. Real time evaluation of an air leak into a dry etching equipment by means of optical emission spectroscopy∶ evaluation and results in high volume production regime [J]. Advanced Semiconductor Manufacturing Conference and Workshop,IEEEI/SEMI, 2003∶ 73-74.

[8] 刘若冰. 铜工艺成功跨越IC技术的鸿沟[J]. 电子产品世界, 2002,(7)∶ 70-71.

[9] 王小泉,汪雷,席珍强,徐进,崔灿,杨德仁. PECVD淀积氮化硅薄膜性质研究[J]. 太阳能学报,2004, 25(3)∶ 341.

[10] Han G C, Luo P, Li KB. Growth and characterization of silicon nitride films on various underlying materials[J].Appl. Phys. A, 2002, 74∶ 243.

[11] Michael Quirk, Julian Serda. Semiconductor Manufacturing Technology [M]. 北京:电子工业出版社,2004. 412.

[12] Ryu C Lee H, Kwon K. Barriers for copper interconnections [J]. Solid State Technology, 1999, 42(5)∶ 43.

[13] 陈晓南,杨培林,庞宣明,袁丛清. 等离子体刻蚀中工艺参数对刻蚀速率影响的研究[J]. 西安交通大学学报,2004, 38(5)∶ 300-310.

[14] 高东岳,李莹,郭常厚,等. 高选择性的SIO2SI干法腐蚀工艺[J]. 微处理机,2003, 1(1):5-7.

[15] Hong Xiao. 半导体制程技术导论[M]. 台北:台湾培生教育出版股份有限公司,2002. 175.

[16] Barrett C R. Semiconductor manufacturing-the past and the future [C]. IEEE/SEMI International Semiconductor Manufacturing Science Symposium, 1989, 1.

[17] Mu-Huo Cheng, Huan-Shin L, Shin-Yeu Lin, Chun-Hung Liu, Wen-Yo Lee, Chia-Hung Tsai. Fault detection and isolation for plasma etching using model-based approach[C]. Advanced Semiconductor Manufacturing Conference and Workshop, IEEEI/SEMI, 2003∶ 208-214.

[18] M Bamal, S List, M Stucchi, A Verhulst, M Van Hove, R Cartuyvels, G.Beter, K Maex. IEEE IITC, P. 202(2006).

[19] Chen I C, Rodder M, Chatterjee A, eng C W. A trench isolation study for deep submicron CMOS technology VLSI Technology, Systems, and Applications [C].Proceedings of Technical Papers. International Symposium, 1993∶ 251-255.

[20] L S Fan, Y C Tai, R S Muller. Ic-processed Electrostatic Micro-motors [C]. IEEE Int. Electr. Devices Meeting, San Francisco, CA, December 11-14, 1988∶ 666-669.

[21] R S Muller, L S Fan, Y C Tai. Micromechanical Elements and Methods for Their Fabrication [J]. U.S. Patent 4740410, issued to the Regents of the University of California, 1988.

[22] Mangiagalli P, Chevolleau T, Posseme N, Frum C, Sabnani L, Sui Z, Assous M. Dual damascene trench depth control by Irm/spl trade/∶ a novel interferometric endpoint system[C]. Advanced Semiconductor Manufacturing Conference and Workshop, IEEEI/SEMI, 2003∶ 47-52.