体硅集成电路版图抗辐射加固设计技术研究

田海燕,胡永强

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 概述

随着人类对宇宙探索的不断深入,越来越多的电子设备被用于航空航天领域。而在太空环境应用中存在的大量高能质子、中子、α粒子、重离子等都会对电子设备中的半导体器件产生影响,继而严重威胁航天器的可靠性和寿命。因此,为满足不断扩大的航空航天领域的需求,增强半导体器件在辐射环境中工作的可靠性和稳定性,对半导体器件辐射效应的研究以及辐射效应加固已成为太空领域应用的研究热点。

目前,体硅CMOS工艺作为半导体器件制成的主流工艺,其特征尺寸已经进入深亚微米,甚至100 nm以下。由该工艺条件制成的半导体集成电路在太空领域应用时,会受到辐射引起的总剂量效应影响和单粒子效应影响。辐射效应对半导体集成电路的影响表现为器件阈值电压漂移、电路静态电流和动态电流增加、电路逻辑功能发生错误等。所以,采用普通的器件及电路设计方法已经不能满足太空及军事领域应用的需求,需要采用特殊的抗辐射加固设计技术。

本文首先分析了辐射效应对器件产生的影响,并从版图抗辐射设计加固的角度出发,介绍了几种抗辐射版图的设计方法,从而提高了电路的抗辐射性能,进而提高了电路的可靠性。失,在电路设计时可以忽略该机制对器件的影响。

2 辐射效应分析

2.1 总剂量效应对器件的影响

2.1.1 总剂量效应对器件栅氧化层的影响

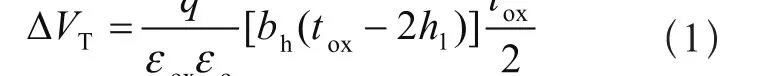

无论是硅栅还是金属栅器件,在栅与衬底间均有一层50~200 nm的SiO2层,在辐射条件下,在SiO2/Si界面处会引起正电荷的堆积。这样的正电荷堆积会引起器件阈值电压的漂移,最终影响器件的性能。同辐射引入的俘获空穴数量相对应的阈值电压变化可以表示为[1]:

式中:bh是氧化物中产生的空穴体密度被俘获后形成的固定正电荷部分;参数h1是从Si/SiO2界面指向氧化物的距离,在此距离内被俘获的空穴可以同衬底向栅隧穿的电子复合。只有当氧化物厚度小于2×h1(6 nm)时,才观察不到显著的空穴俘获[2]。

图1所示为典型的NMOS和PMOS管的I-V特性曲线随辐射电离总剂量的增加而逐渐漂移的过程。图中X轴为栅极电压VG,Y轴为漏极电流ID。0表示未辐照前器件的I-V特性曲线;1、2、3、4表示不同辐照剂量下器件的I-V特性曲线。随着时间的增加,电离总剂量增大,阈值电压漂移就越大。对于NMOS管,栅极所接的正电压大于阈值电压时,晶体管开始导通。对于PMOS晶体管,栅极所接的负电压小于阈值电压时,晶体管导通。根据图1(a),NMOS管随着电离总剂量的增大,阈值电压向负方向漂移,表现为阈值电压减小。本该截止的晶体管变为导通,原来该导通的晶体管需要截止时无法截止。同样,根据图1(b),PMOS管随着电离总剂量的增大,阈值电压向负方向漂移,表现为阈值电压增加。本该导通的晶体管变为截止,原来该截止的晶体管需要导通时无法导通。根据式(1),NMOS管与PMOS管的阈值电压漂移量近似与栅氧化层的厚度tox的平方成正比。

但值得庆幸的是,随着工艺关键尺寸的缩小,器件的栅氧化层厚度也随之减小,器件的I-V特性漂移量降低。进入0.18 μm之后,栅氧化层厚度低于12 nm,由辐射引起的阈值电压漂移明显减小甚至消

图1 NMOS管和PMOS管在辐照条件下的I-V特性漂移

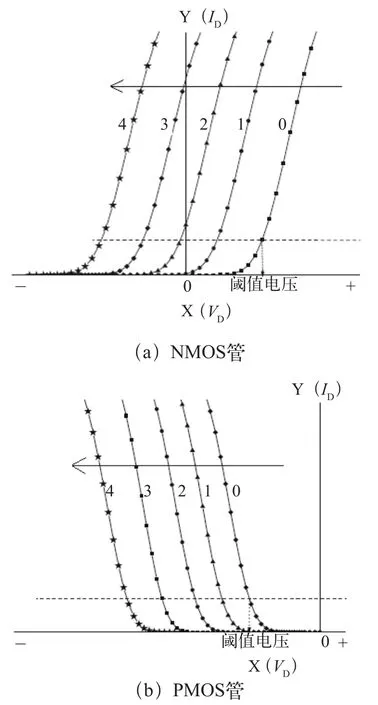

2.1.2 总剂量效应引起的器件源漏区域漏电

采用自对准工艺制作的NMOS管,多晶硅栅淀积在薄氧化层上,源/漏由没有被多晶硅覆盖的有源区注入形成,这种工艺制造出的电路密集度高,但使多晶硅栅在场氧和栅氧过渡区产生了边缘寄生晶体管,该寄生晶体管对总剂量效应十分敏感。在辐射条件下,SiO2场区边缘堆积的正电荷会使边缘寄生晶体管发生漏电。随着辐射剂量的增加,边缘寄生晶体管漏电流也迅速上升,当漏电流增加到接近本征晶体管的开态电流时,晶体管会永久开启,导致器件失效。图2(a)为该漏电机制顶面示意图,图2(b)为该漏电机制剖面示意图。

图2 源/漏区域漏电顶层与剖面示意图

2.1.3 总剂量效应引起的场氧下漏电

场氧化层本来是为相邻MOS管之间绝缘隔离的。但由于总剂量效应,在场氧中会电离电子-空穴对,空穴在Si/SiO2系统的SiO2一侧堆积形成的界面态会使场氧下反型,形成电子漏电通路。其漏电机制如图3所示。场氧下反型形成的漏电通路能延伸到邻近的MOS管源/漏区,这将增大VDD到VSS的静态漏电流。

图3 总剂量效应引起的场氧下漏电

2.2 单粒子翻转效应对器件的影响

单粒子翻转效应发生在含有存储结构的时序电路中,我们以锁存器为例,解释单粒子翻转效应发生的机理。图4为简单的锁存器结构。当输出节点受到单粒子入射形成“漏斗效应”,产生大量的电荷,如图5所示。在电场作用下,电离产生的电荷在器件中漂移,最终影响锁存器的状态。

图4 简单的锁存器输出节点受辐射影响

图5 单粒子入射在器件内部形成的“漏斗效应”

当存储的数据为“0”时,NMOS管对地处于导通。此时,PMOS管的漏端与N阱形成的P-N结处于反偏状态,形成的内建电场方向从N阱指向PMOS漏端。当PMOS漏端受到单粒子入射,电离出很多电子-空穴对。在电场的作用下,大量的空穴向PMOS的漏端漂移,而电子向N阱漂移。当正电荷漂移至PMOS漏端的数量达到一定量级时,就会改变原来存储“0”的状态,变为存储“1”。原理如图6(a)所示。

同样,当存储的数据为“1”时,PMOS管对电源处于导通。此时NMOS管的漏端与P-衬底形成的P-N结处于反偏状态,形成的内建电场方向从NMOS管的漏端指向P-衬底。当NMOS漏端受到单粒子入射,电离出很多的电子-空穴对。在电场的作用下,大量的电子向NMOS漏端漂移,而空穴向P-衬底漂移。当负电荷漂移至NMOS漏端的数量达到一定量级时,就会改变原来存储“1”的状态,变为存储“0”,其原理如图6(b)所示。

图6 存储的数据受单粒子效应的影响

从上面的分析我们不难发现,单粒子翻转效应发生的条件是在CMOS电路结构中存在反偏的P-N结,通过内建电场实现电荷的漂移,从而影响原有的逻辑状态。

3 版图加固方法

随着工艺尺寸的不断减小,体硅MOS器件栅氧化层的厚度也不断减薄。所以,总剂量效应引起的阈值电压漂移可以忽略。而总剂量效应引起的器件源/漏区域漏电及场氧下漏电只能通过版图设计进行抗辐射加固。而某些特定的单粒子效应也可以通过版图设计的手段进行加固。

3.1 总剂量效应版图加固方法

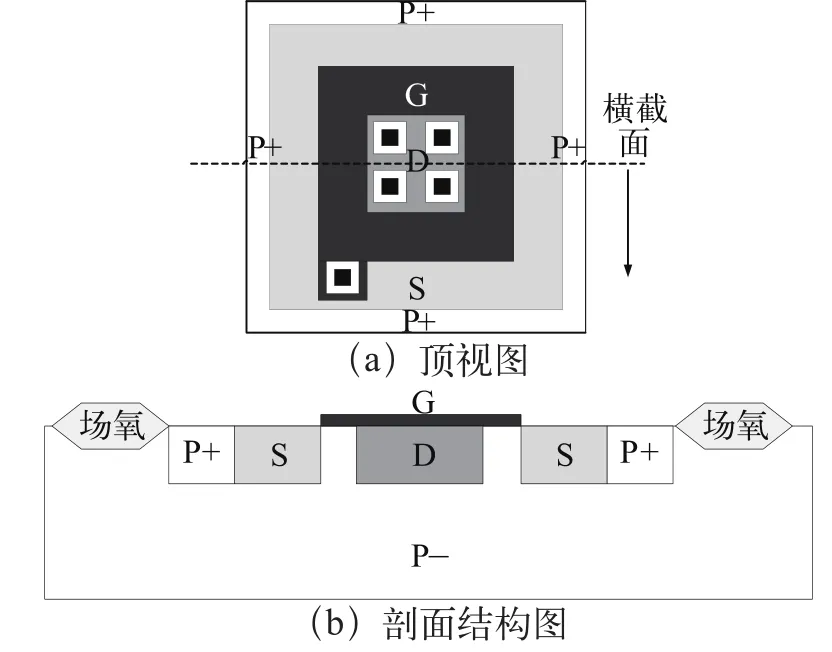

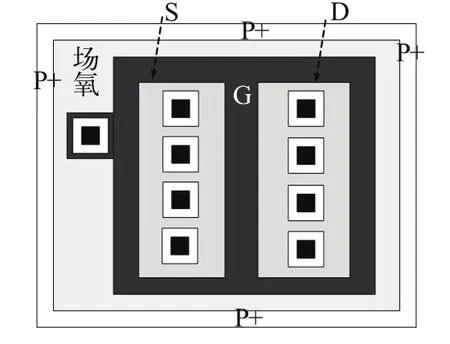

首先,可选择的器件版图结构是环形栅的结构,以NMOS管为例,如图7所示。图7(a)图中D端代表器件漏端区域,S端代表器件的源端区域,G为NMOS管的栅极,黑色方块为接触孔,外围为P+注入的保护环。利用该版图结构,消除了原始MOS器件在边缘处的寄生管,使MOS器件内源/漏端之间不存在漏电通路;并且,加入P+保护环后,对不同NMOS器件之间由于总剂量效应引起的场氧化层下反型后导致的电子漏电,能起到吸收的作用。其纵向的剖面图如图7(b)所示。从剖面图也可以看出,由于栅的隔离,使器件源/漏之间消除了侧边寄生管,进而消除了总剂量效应引起的漏电通路。

图7 环形栅 NMOS管示意图

虽然通过环形栅结构能够改善MOS管在总剂量辐照条件下的漏电,但采用环形栅之后,MOS管的W/L比例就受到了很大的限制,而且很耗费面积。一个环形栅的MOS器件最小W/L比为4∶1,用此结构去实现小比例或者倒比例MOS管几乎是不可能的。

当在抗辐射版图设计时遇到倒比例MOS管,可以采用如图8的版图结构。在此结构中,同样也是利用了栅极和栅氧化层,将MOS管的源端与漏端隔离,消除了原先存在的边缘寄生管,从而消除了总剂量条件下器件内部源/漏端之间的漏电。周围也是采用P+环将器件和周围器件隔离,保证了在总剂量辐射条件下不同器件之间不存在漏电。图9为类似倒比例管的MOS管加固结构。

在加固的单元结构中,为了避免总剂量效应引起的场区漏电,设计时采用了类似增强型PMOS管的结构,以隔离单元之间的漏电通路,原理如图10所示。此结构在场氧中加入了栅控结构,当栅接负电压,从衬底中吸收正电荷,从而吸收由辐射导致漏电通道中的电子,使漏电通道被带正电荷的区域隔离。与传统的有源区周边P+环隔离结构相比,该设计不但消除了N+有源区与P+有源区之间由工艺尺寸要求的最小间距限制,节省了单元面积,同时还可以通过调节产生负电压的负电荷泵级数,从而输出更负的电压,以应对由于不同辐射剂量而导致的漏电量不同。

图8 倒比例NMOS管示意图

图9 类似倒比例管的MOS管加固结构

图10 存储单元隔离结构

3.2 单粒子昆倾效应(Quenching)的版图加固

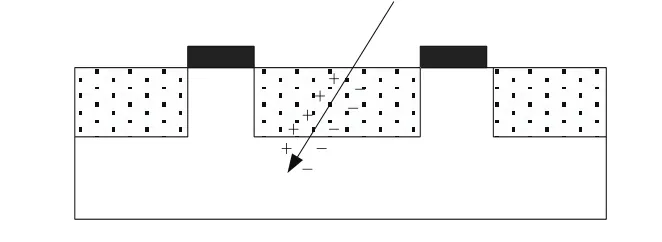

随着工艺尺寸的不断缩小,单粒子效应对器件的影响将不仅仅局限于某一个节点,而是会在临近节点之间出现电荷分享。此单粒子效应电荷分享机制就为昆倾效应(Quenching)。例如,在设计与非门、或非门逻辑时,常常会将两个串联的MOS管版图画成如图11所示的结构。此版图结构制成的电路在受到单粒子效应影响时,会同时影响到两个MOS管的有源区,如图12所示。

图11 普通串联MOS管版图结构

图12 单粒子效应对普通串联MOS管影响

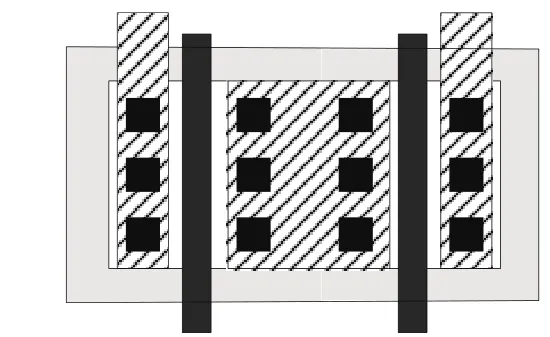

为减小此分享机制的存在,可以将两个串联的MOS版图结构换成如图13的结构。在受到单粒子效应影响时,该版图结构将两个MOS管的共用有源区隔离,从而消除了电荷分享机制的存在,如图14所示,进而提高器件的可靠性。

图13 加固后串联MOS管版图结构

图14 单粒子效应对加固后串联MOS管影响

4 小结

为了满足抗辐射电路设计的需求,本文首先分析了辐射效应对器件产生的影响, 并从版图抗辐射设计加固的角度出发,介绍了抗总剂量的环形栅、倒比例器件,以及抗单粒子昆倾效应(Quenching)抗辐射版图的设计方法。在电路设计时,通过上述几种版图设计方法的应用,可以提高电路的抗辐射性能,进而提高了电路的可靠性。

[1] C Claeys, E Simoen. 先进半导体材料及器件的辐射效应[M]. 北京:国防工业出版社, 2008.

[2] Walters M, Reisman A. Radiation-induced neutral electron trap generation in electrically biased insulated gate field effect transistor gate insulators [J]. Electrochem Soc,1991, 138∶ 2756-2762.