ALD氧化铝薄膜介电性能及其在硅电容器的应用

陈 杰,李 俊,赵金茹,李幸和,许生根

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

电容器广泛应用在电子技术领域,随着电子产品的微型化,对电容器性能提出了更高的要求。譬如应用在医疗领域的电子产品要求电容器体积小、功耗低、可靠性好;而应用在石油勘探领域的电子产品要求电容器能够耐250 ℃的高温;应用在能源存储领域要求电容器存储能量密度高;手机等通信产品要求电容器体积小、温度特性和电压特性好。这些需求促进了用半导体技术在硅片上制造电容器的发展,国内外研究机构也在积极进行相关方面内容的研发[1]。总体来说,对电容器的要求有能量密度更高、耐温高、功耗低等。硅电容器增加能量密度研究的方向一方面是在硅片上形成高深宽比的硅槽来增加电容器的表面积,另一方面是使用高K材料作为电容器的绝缘介质来提高容量,同时减小了电容器的漏电流。

Al2O3材料有较高的相对介电常数,并且高带隙(8.7 eV)、高势垒导致其隧穿电流小。在室温下Al2O3的介电子被激发到导带中去的几率小,表现为绝缘体。理想的Al2O3薄膜相对介电常数是9,击穿强度可达1 V/nm以上。但是用ALD设备沉积的Al2O3薄膜以非晶态形式存在[2],沉积的薄膜中含有-CH3和-OH基团[3]而使介电常数和击穿强度达不到理论值。本文通过提高沉积温度以及在O3气氛下低温退火的方法来减少Al2O3薄膜沉积过程中薄膜内-CH3和-OH基团含量,提高ALD沉积的Al2O3薄膜的介电性能。

2 深硅槽的制备

本文采用Precision 5000等离子刻蚀机刻蚀深硅槽。深硅槽是在硅片衬底上形成的3D结构,是制造高密度硅电容器的关键技术之一,制备方法如图1所示。本文采用三叉柱结构来增加表面积,三叉柱深度6 μm。

图1 深硅槽制备方法

3 Al2O3绝缘薄膜在硅电容器的作用

根据单位面积电容量公式:

式中ε0为真空绝对介电常数,εr是介质材料的相对介电常数,d是介质的厚度。可以看出,能通过减薄介质的厚度来增加电容值。但是半导体制造常用的介质SiO2或Si3N4介质,它们的隧穿电流随着介质厚度的减薄而呈指数性增加[4]。使用高K的材料,可使介质的隧穿电流降低2个数量级以上[5]。Al2O3是高K材料,相对介电常数是9,几乎是二氧化硅/氮化硅/二氧化硅(ONO)介质的2倍。而且Al2O3材料的功函数高,所以Al2O3可以用作高密度电容的介质材料。

4 Al2O3绝缘薄膜的生长原理和制备方法

ALD(原子层沉积)是一种薄膜技术[6~8],它可以由一层原子再一层原子来生长薄膜。沉积Al2O3薄膜的前驱体是三甲基铝(TMA)和水,沉积的化学原理是配位替代化学反应。配位替代化学反应式为:

Al2O3绝缘薄膜的制备采用Cambridge公司的ALD设备。由于ALD方法采用逐层生长,可使薄膜在深硅槽中均匀地生长。Al2O3薄膜在硅槽中用作硅电容的介质,其介电性能是非常重要的。衡量它的介电性能好坏的主要因素是材料的介电常数和击穿强度。本文通过提高沉积温度和O3退火的方法提高介电性能。

5 沉积步骤

(1)硅片放入ALD腔体,由于硅片表面是亲水性的,所以硅片表面存在Si-OH键;(2)脉冲TMA前驱体进入腔体, TMA与硅片表面-OH基团发生配位替代反应,创建Si-O-Al-CH3键;(3)通入N2,排出未反应的TMA和反应产物CH4;(4)脉冲H2O到腔体,H2O配位替代Si-O-Al-CH3键中的CH3基团, 创建O-Al-OH键,一层Al原子已经沉积在硅片表面;(5)再次通入N2排出未反应的H2O和反应产物CH4。

步骤(1)~(5)形成一个周期,循环往复。每个周期产生0.11 nm厚的Al2O3薄膜。沉积结束后,硅片保留在腔体内在O3气氛下退火5 min。

6 Al2O3薄膜的生长和介电性能研究

6.1 实验流程

在硅上生成金属/绝缘体/金属(MIM)结构,来研究Al2O3薄膜的介电性能。在沉积Al2O3薄膜之前,在硅片衬底上生长一层二氧化硅(SiO2)氧化层隔离硅衬底。在SiO2氧化层上溅射一层氮化钛(TiN),然后光刻和刻蚀TiN,清洗工序非常关键,因为硅片表面的洁净度会影响Al2O3薄膜击穿性能。然后通过ALD沉积Al2O3薄膜和退火处理,再溅射一层TiN,然后光刻和刻蚀,清洗后就可以测试。本文采用P型<100>晶向、电阻率为14 Ω.cm的硅片作为衬底,上下电极采用TiN是为避免Al2O3与电极接触的界面发生反应。流程如图2所示。

6.2 ALD 沉积工艺的优化

ALD沉积Al2O3的化学原理是配位替代化学反应,本实验是通过改变ALD腔体的温度来加强配位替代化学反应。各实验的沉积参数如表1所示。

图2 ALD 沉积Al2O3薄膜流程

表1 各实验的沉积参数

6.3 各实验的测试结果与讨论

本文采用TH2689A漏电漏/绝缘电阻测试仪测试Al2O3薄膜的J-E特性,通过TH2818自动元件分析仪测试电容的容量然后计算得到介电常数,J-E特性测得的结果如图3。

图3 实验1~4的J-E曲线图

从结果中可以看出,在0.2 V/nm电场强度下,实验2、实验3和实验4电流密度比实验1的小得多。原因是实验2、实验3和实验4在ALD沉积Al2O3薄膜后都做了退火处理,而实验1没有做退火处理。因为ALD沉积Al2O3采用TMA和H2O作为反应物,Al2O3薄膜中存在没有被配位替代掉的少量-OH键, 这样薄膜内含有氢氧键,经退火后,减小了薄膜中的水分子,同时所含的氢也减少,漏电流随之减小。

从图3中,还可以观察到Al2O3的击穿强度依次是实验4>实验3>实验2>实验1。实验2比实验1的击穿强度略大,说明ALD 沉积的Al2O3薄膜中还有其他因素影响着。实验4中击穿强度得到大幅度的提高,显然随着沉积温度的提高击穿强度随之增加。理论上Al2O3化合物中的O和Al元素按化学计量比1.5结合,ALD沉积的Al2O3薄膜的原理是Al(CH3)3作为反应物配位替代羟基,再有H2O作为反应物配位替代-CH3基团,由于配位替代不充分,薄膜内含有少量的-OH和-CH3基团,由于C和H的存在,沉积的Al2O3薄膜的O与Al元素比就偏离化学计量比。随着腔体温度的提高,反应物Al(CH3)3变得更加活泼,配位替代充分,降低了薄膜内-OH和-CH3基团,Al2O3化合物的O与Al元素比接近于化学计量比。这样的薄膜致密度大大提高,击穿强度随之增加。

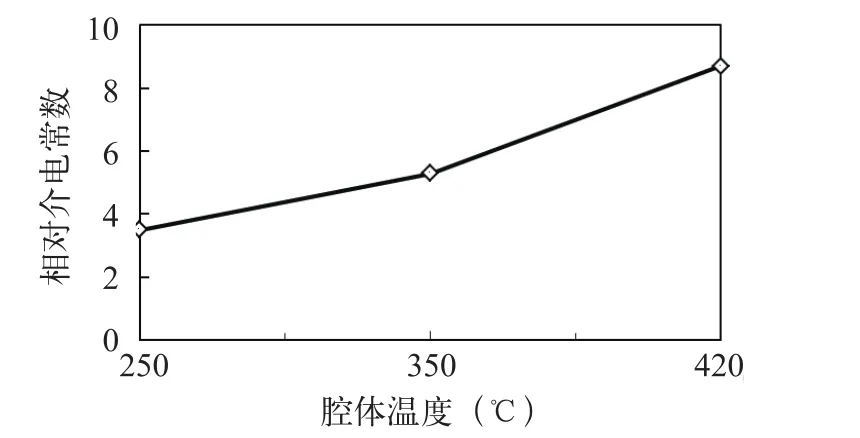

由于ALD沉积的Al2O3薄膜方式是一层又一层原子,其沉积速率非常稳定,用来研究介电常数的样品都是100个生长周期后沉积的Al2O3薄膜,所以样品间薄膜厚度的偏差可以忽略不计。通过测得电容的容量再由单位面积电容计算公式(1)计算得到相对介电常数。实验表明在420 ℃温度下生长的Al2O3相对介电常数可达8.7,接近于理论值。这显然也证明了随着沉积温度的上升,Al2O3薄膜内的含水量(-OH基团)和含碳量(-CH3基团)减少。由于薄膜内杂质的减少,沉积的Al2O3薄膜的O与Al元素比接近于化学计量比,相对介电常数就高。图4是不同腔体沉积温度下得到的Al2O3薄膜材料的相对介电常数。

图4 不同腔体沉积温度下Al2O3薄膜材料的相对介电常数

7 Al2O3薄膜在硅电容器上的应用

7.1 硅电容制作流程

采用半导体CMOS制作相兼容的工艺制成实用型的硅电容器,工艺简单。本文采用双层MIM结构电容(TiN/Al2O3/TiN/Al2O3/TiN)并联组成一个大电容,目的是增加电容密度。TiN和Al2O3采用Cl2基等离子刻蚀,TiN与Al2O3刻蚀的选择比为8∶1, 控制TiN与Al2O3刻蚀时间是关键。硅电容器采用芯片级封装,在电极上化镀5 μm厚度的镍。最终划片形成硅电容器。流程如图5所示。

7.2 硅电容器的容量和击穿电压的测试结果和讨论

用上述流程制作的电容器用KEITHLEY 4200 SCS仪器进行耐压和容量测试,采用连续升压法,图6是测试得到的I-V曲线和C-V曲线。在电容器击穿前,漏电流相当平滑,漏电流小过5 nA,在击穿点,漏电流快速上升,显示了良好的击穿特性。电容器在-5~+5 V电平扫描下,容量变化相当稳定,变化率只有0.03 nF/V。

图5 硅电容器制作流程

图6 测试得到的I-V曲线和C-V曲线

8 结论

本文主要研究了ALD制备氧化铝绝缘薄膜的介电性能,通过优化ALD沉积工艺和退火处理,减少沉积过程中形成含碳和含氢缺陷。随着沉积温度的上升,反应物Al(CH3)3和H2O配位替代反应更彻底,沉积的Al2O3薄膜含碳量降低。通过退火处理的方法进一步使薄膜中含氢量降低,Al2O3薄膜变得致密,Al2O3薄膜击穿强度提高到0.7 V/nm以上。采用这样的薄膜做硅电容器的绝缘介质,提升了硅电容器的性能,6 μm深的硅槽电容器的电容密度可达50 nF/mm²,漏电流小于5 nA。

本文研究ALD沉积Al2O3作为硅电容器的绝缘介质,由于Al2O3介电常数只有9,电容密度提高有限。今后可以研究更高的介质材料如TiO2(K值80)和HfO2(K值25)应用于硅电容器中。另外本文研究的硅电容器硅槽不够深,今后可以采用深硅槽刻蚀机刻蚀60 μm以上的深硅槽。研究更高K值的材料和更深的硅槽,硅电容器的电容密度还有极大的上升空间。

[1] ROOZEBOOM F, DEKKERS W, LAMY Y P R, et al.System-in-package integration of passives using 3D throughsilicon vias [J]. Solid State Technology, 2008, 51∶ 38-41.

[2] MEYER D C, LEVIN A A, PAUFLER P. Crystalline coatings of aluminosilicate Al2SiO5polymorphs formed by solid state reaction of alumina layers with silicon/silica substrates [J]. Thin Solid Films, 2005, 489∶ 5-16.

[3] 卢红亮, 徐敏, 丁士进,等. 原子层淀积Al2O3薄膜的热稳定性研究 [J]. 无机材料学报, 2006, 21∶ 1217-1222.

[4] 施敏,主编. 现代半导体物理[M]. 北京:科学出版社,2001.

[5] 甘学温, 黄如, 刘晓彦. 纳米CMOS器件[M]. 北京:科学出版社,2004.

[6] SUNTOLA T. Atomic Layer Epitaxy [J]. Mat Sci Rep,1989, 4∶ 261-312.

[7] LESKEL M, RITALA M. Atomic layer deposition(ALD)∶from precursors to thin film structures [J]. Thin Solid Films, 2002, 409∶ 138-146.

[8] KIM H. Atomic layer deposition of metal and nitride thin films∶ Current research efforts and applications for semiconductor device processing [J]. J Vac Sci Technol B,2003, 21∶ 2231-2261.