可重构RISC微处理器的FPGA实验方案的研究

杨 斐 ,汪 鹏

(1.湖北理工学院 计算机学院,湖北 黄石 435003; 2.中南大学 软件学院,长沙 410083)

可重构RISC微处理器的FPGA实验方案的研究

杨 斐1*,汪 鹏2

(1.湖北理工学院 计算机学院,湖北 黄石 435003; 2.中南大学 软件学院,长沙 410083)

利用FPGA的可重构特性,设计了一个基于精简指令系统的微处理器。该处理器采用微程序控制器思想,可完成指令的译码、执行以及数据的加工处理,通过Altera公司的QuartusⅡ9.0软件并结合EDA技术完成了核心电路的设计,硬件平台是型号为EP2C8Q240C8的FPGA芯片。该实验方案优势在于开发成本低、功耗低、可重构性,对设计成果进一步改进可适用于大多数嵌入式系统,其硬件可重构的特点对于提高信息安全性也有一定的作用。

可重构;电子设计自动化技术;现场可编程门阵列;高速硬件描述语言

随着电子技术的飞速发展,现代电子产品渗透到了社会的各个领域,并有力地推动着社会生产力的发展和社会信息化程度的提高。这些产品在性能提高、功能更加强大的同时,成本却一直呈现逐步下降的趋势,其主要原因是生产技术和电子设计技术的发展。生产技术以微细加工为代表,目前已经发展到到深亚微米阶段;而电子设计技术的核心是电子设计自动化技术(即EDA技术)[1]。

利用以硬件描述语言为基础的EDA设计方法,用户可以在可编程芯片(CPLD或FPGA)上自行设计面向应用的专用CPU核,以构建适用的嵌入式系统。考虑到设计产品的许多性能指标变化太快,为已经完成设计并投入应用的产品保留多次可自由更改的功能是十分必要的,这就是可重构的概念。通过CPU加入可以动态重构的可编程逻辑,为每一个不同应用加载不同的可编程配置,以优化计算速度,是一种新的模糊软硬件界限的技术[2]。这种可重构技术对于提高产品开发效率、降低成本以及获得更长的市场生命期、拥有独立知识产权有重大意义。

FPGA(现场可编程门阵列)是目前应用最广泛的通用可重构器件,从一定程度上讲,可重构计算起源于FPGA的发明[3]。因此本文研究的是RISC微处理器的FPGA实现方案,使用VHDL(超高速硬件描述语言)和原理图方法进行设计,通过Altera 公司的QuartusⅡ9.0软件平台完成设计的输入、综合,并进行仿真及调试。硬件平台采用EDA开发板,该开发板以Altera公司的CYCLONE II系列的FPGA芯片作为硬件核心,芯片型号为:EP2C8Q240C8,同时开发板包括多种实用接口,便于开发者进行硬件测试。

1 总体设计思路

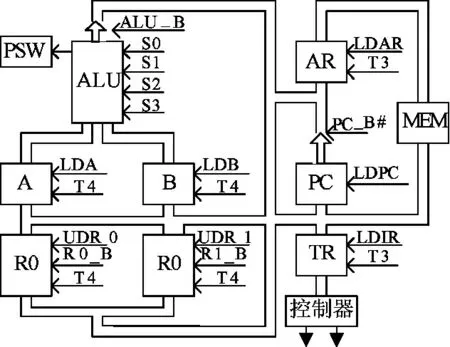

图1 数据通路图

微处理器对整个计算机系统的运行是极其重要的,虽然各种微处理器在性能指标和结构细节上有所不同,但所要完成的功能基本相同,整体可分为:运算器、控制器、指令译码器、通用寄存器、指令寄存器、程序计数器、地址寄存器、状态寄存器、时序产生器等[4],各部件利用总线传递信息。因此,需要设计合理的总线系统,以控制各部件的数据传送工作。设计好的数据通路图如图1所示,其中ALU为算术逻辑单元,其运算功能由S0S1S2S3信号来控制;R0、R1为通用寄存器;LDR0、LDR1是寄存器装载控制信号;R0_B、R1_B是寄存器输出三态门的控制信号;A、B为ALU的2个暂存器,分别由LDA、LDB信号来控制数据的输入;AR、PC、IR分别为地址寄存器、程序计数器、指令寄存器,这些专用寄存器的工作都受到指定信号的控制。所有的控制信号均由控制器根据指令功能来产生。

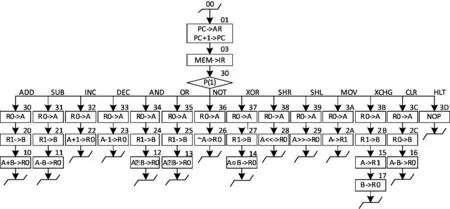

图2 指令周期流程图

2 指令系统的设计

2.1微处理器的机器指令集

指令系统是表征系统性能的重要因素之一,它的格式与功能不仅直接影响到机器的硬件构成,而且直接影响到系统软件的效率和机器的适用范围。因此,指令系统的设计是很重要的。RISC(精简指令系统计算机)具有简单指令集、配备大量通用寄存器、指令执行周期短等特点[5]。因此,笔者设计了14条典型的机器指令,如加法、减法、自增、逻辑与、逻辑或、左移、右移、停机等,指令长度为16位定长,分别用8位二进制位存放指令的操作码和地址码。

例如加法指令:助记符为ADD R0,R1, 指令代码为00000010-00000001;减法指令:助记符为SUB R0,R1,指令代码为00000011-00000001。以此类推,可列出所有机器指令的二进制代码。

2.2 微程序代码的设计

采用微程序控制器的思想,使微处理器具有规整性、灵活性、可维护性等一系列优势。其思想是将每条机器指令由若干条微指令组成的序列来实现的。因此,一条机器指令对应着一个微程序,微程序的总和便构成了整机的指令系统[6]。

根据设计好的数据通路图,将每一条机器指令按功能细分成若干个微操作,从而画出指令周期流程图,如图2所示。图中,将每一条微指令用一个矩形方框表示。以加法指令ADD R0,R1为例,介绍其运行过程:设置初始微地址为0001H,该地址存放的微指令功能是将程序计数器PC的当前值送入地址寄存器AR中,同时将PC加1;然后执行第二条“取指”的微指令,微地址设置为0003H,用来从内存中取出一条机器指令,并存放到IR中,测试位P(1)对机器指令的操作码(即ADD:00000010)进行测试,从而得到下一条微指令的地址。所有微指令都存放在控制存储器中,取出正确的微指令代码后,控制器就会产生相应的控制信号,从而控制执行部件做相应工作。当微程序进行到公操作(即0001地址中的微指令)时,在没有外围设备请求时,就进行下一条机器指令的取指操作。

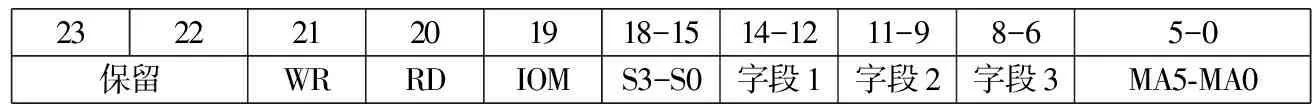

232221201918-1514-1211-98-65-0保留WRRDIOMS3-S0字段1字段2字段3MA5⁃MA0

图3微指令格式

为节省控存容量,本文采用的是直接和译码相混合的水平型微指令格式,共占24位,如图3所示。其中,高5位用来产生存储器或I/O设备的读写控制信号,第18~15位产生运算器的运算控制信号,字段1、字段2、字段3采用的都是字段译码方案,以缩短微指令字的长度。字段1用来产生各寄存器的装载控制信号,字段2产生总线输出控制信号,字段3包括测试位及保留位。5~0位为M字段,即下地址字段,用来产生下一条微指令的微地址。

按照设计好的微指令格式,可以将图2中每一个方框对应的微指令代码编写出来。例如10H微地址中,存放的微指令完成的操作是A+B→R0,其对应的24位二进制代码是:000000010011001000000001。

3 主要模块的设计

3.1 控制器模块的设计

控制器是CPU的核心部件,所有执行部件都在控制器的控制下有条不紊地完成规定的操作。控制器包括指令寄存器、地址转移逻辑、控制存储器、微指令寄存器等部件[7],其基本功能是对指令寄存器中的指令进行翻译,从而产生对应的微程序入口,再从控存中取出一条微指令代码,以微指令代码中的控制字段向各执行部件发号命令。其中,地址转移逻辑承担自动修改微地址的任务,从而控制微程序的正确运行,是纯组合逻辑电路,因此,可以利用VHDL中的CASE语句进行功能描述。

按照前面设计好的指令格式,将机器指令代码和微指令代码分别存入一定容量的RAM和ROM中。这2个模块都是通过QUARTUS II中的参数可设置模块LPM来实现的。要将代码有效存入,还必须事先编写MIF格式的初始化文件。例如,控存ROM对应的MIF文件部分代码为:

WIDTH= 24 ; --字长

DEPTH= 64; --字数

ADDRESS_RADIX=HEX;

DATA_RADIX=HEX;

CONTENT BEGIN

00:000001;

01:006D43;

03:107070;

10:013201;

…….

3.2 运算器模块的设计

运算器由算术逻辑单元(ALU)、累加器、状态寄存器、通用寄存器组等组成。算术逻辑运算单元(ALU)的基本功能是完成操作数的加工处理。将操作数存于暂存器A和暂存器B中,控制信号S3…S0来决定ALU对操作数进行何种运算。运算结果送给输出寄存器Q,结果将影响到状态寄存器中相关位。

图4 顶层设计框图

利用VHDL语言将ALU的主要功能描述出来,主要代码如下:

PROCESS (A,B,S)

BEGIN

CASE S IS

WHEN "0000"=gt;Qlt;=A;

WHEN "0001"=gt;Qlt;=B;

WHEN "0010"=gt;Qlt;=A + B;

WHEN "0011"=gt;Qlt;=A - B;

WHEN "0100"=gt;Qlt;=A + 1;

WHEN "0101"=gt;Qlt;=A - 1;

WHEN "0110"=gt;Qlt;=A AND B;

WHEN "0111"=gt;Qlt;=A OR B;

WHEN "1000"=gt;Qlt;= NOT A ;

……

本文安排的运算功能虽然简单,但具有典型性,优势在于其设计方法简单,扩展性较强,n位控制端可产生2n种运算,较传统电子设计方法而言,可大大降低设计成本、缩短设计周期。

3.3 寄存器模块的设计

寄存器是一个典型的时序逻辑电路,在特定时钟信号的控制下可以装载一组二进制数据并稳定存储[8]。本文的微处理器中用到了多个16位寄存器如PC、IR、AR以及24位寄存器UIR。充分利用VHDL中不完整的IF语句能产生时序电路的特点,实现了数据的稳定存储,不涉及到内部触发器,设计周期更短,效率更高。实际应用中,可根据设计需求随时更改寄存器的位宽以及触发方式,体现出其可重构的特点。

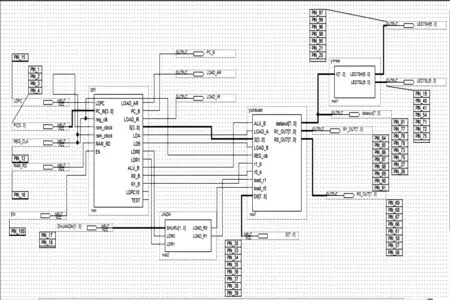

3.4 各模块连接框图

按照系统总体设计思路,并结合EDA技术的开发特性,在QuartusII 9.0中创建新的工程,并利用原理图方法画出该系统的顶层设计框图,如图4所示。

4 仿真与下载

图5 仿真波形图

4.1时序仿真

在编程下载之前,必须利用EDA工具对设计结果仿真。本文采用仿真精度较高的时序仿真,总体波形仿真图如图5所示,其波形描述了CPU取出加法指令(PC=0000)并执行该指令的过程,先后输入了05H、12H到R0、R1中,DATAOUT显示运行结果为17H,输出波形完全正确。同理,运行其他机器指令,观察输出波形,从而验证了该系统达到了预期的功能需求。

4.2 硬件下载

根据开发板中FPGA芯片的引脚特性,在QuartusⅡ9.0中,将本系统中最终的CPU模块进行引脚分配后,对目标器件进行编程操作,成功下载本系统的sof文件后,在开发板上进行硬件调试,并利用嵌入式逻辑分析仪 SignalTap II 观察指令的运行情况。最终在FPGA上实现了基于RISC的微处理器。

5 结语

本文实现了一种具有基本功能的可重构微处理器。打破了传统逻辑电路的设计方法,采用了目前主流的EDA技术,可编程器件FPGA为设计带来了极大的灵活性,通过软件编程对硬件的结构和工作方式进行重构,使得硬件的设计可以像软件设计那样快捷方便。由于高速发展的FPGA具有串、并行工作方式和高性能、低功耗、可重构性的特点,由它实现的微处理器势必在当代电子市场中具有较强的竞争能力。

实验证明,本设计方案可行、可靠,并可以进一步改进以适用于大多数嵌入式系统,尤其是信息安全方面的应用,其硬件可重构的特点对于提高信息安全性有积极作用。

[1] 常瑞丽,崔国玮,韩军.EDA技术的发展与电子技术实验教学的改革[J].中国现代教育装备,2009(11):18-20.

[2] 潘松,黄继业.EDA技术实用教程:VHDL版[M].北京:科学出版社,2010.

[3] BUELL D,EI-GHAZAWI T,GAJ K,et al.High-performance reconfigurable computing[J].IEEE Computer,2007,40(3):23-27.

[4] 许金纲,王维维.微处理器体系结构[M].北京:科学出版社,2008.

[5] 白中英.计算机组成原理[M].北京:科学出版社,2008.

[6] 王培麟.FPGA架构的8位CISC CPU设计[J].煤炭技术,2010,29(10):212-214.

[7] 姜咏江.基于Quartus II的计算机核心设计[M].北京:清华大学出版社,2007.

[8] 卢毅,赖杰.VHDL与数字电路设计[M].北京:科学出版社,2002.

[9] 孙康.可重构计算相关技术研究[D].杭州:浙江大学,2007.

[10] 侯慧,曹伟,王健,等.动态可重构技术浅述[J].半导体技术,2008,33(7):553-557.

[11] BISHOP P,SULLIVAN C.A reconfigurable future[J].Proceedings of IEEE International Conference on Field-Programmable Technology,2003:2-7.

[12] 马梦雅.嵌入式软核CPU的FPGA实现和比较研究[D].北京:北京工业大学,2012.

StudyonFPGAExperimentalSchemeofReconfigurableRISCMicroprocessor

YANGFei1*,WANGPeng2

(1.School of Computer Science, Hubei Polytechnic University, Huangshi 435003,China;2.School of Software, Central South University, Changsha 410083,China)

The paper designs a RISC-based microprocessor using the reconfigurability of FPGA. By using MCU concept, the microprocessor is capable of instruction decoding amp; execution and data processing. Its core circuit is designed by using Altera Company's software QuartusⅡ9.0 and combining EDA technology, and its hardware platform is the FPGA chip of model EP2C8Q240C8. The experimental scheme has the advantages of low cost of development, low power consumption and reconfigurability. After further improvement, the design result is applicable to most embedded systems, and the reconfigurability of hardware contributes to information security to some extent.

Reconfiguration; EDA technology; FPGA; VHDL

2013-08-15

湖北省教育厅科学技术研究项目“基于FPGA的可重构加密系统的研究”(B2013064);湖北理工学院实验室开放基金项目“模型机实验系统的EDA设计方案”(201301)

杨斐(1981- ),女(汉族),湖北大冶人,讲师,硕士,研究方向:EDA技术和嵌入式系统,通信作者邮箱:33965991@qq.com。

汪鹏(1989- ),男(汉族),湖北黄冈人,在读硕士研究生,研究方向:无人车智能控制。

N33

A

2095-5383(2013)04-0037-04