MAP200E音频编码器X.21接口设计

沈向辉,尹航

(中国传媒大学,广播电视数字化教育部工程研究中心,北京 100024)

MAP200E音频编码器X.21接口设计

沈向辉,尹航

(中国传媒大学,广播电视数字化教育部工程研究中心,北京 100024)

本文利用现有E1转PCI接口板上提供的LTC1543多协议转换芯片,将MAP200E 音频编码器输出的数据流(STI-PI帧)通过X.21接口接入FPGA芯片,实现STI-PI帧同步。

MAP200E;E1;PCI;LTC1543;X.21接口;STI-PI帧

1 引 言

在现有E1转PCI接口板的基础上,利用其上提供的LTC1543多协议转换芯片,将MAP200E编码后的数据流(STI-PI帧)通过X.21接口(非标准)接入FPGA芯片(EP1C6Q240C8)进行后续处理。

在FPGA内将由MAP200E编码后的数据流打包封装成PCI接口所需的信号格式,由PCI接口向外(复用器)输出PCI信号流。

2 硬件设计方案

2.1 MAP200E的X.21接口标准

阅读MAP200E的datasheet可知其提供的X.21接口为非完整标准的接口,相关接口特性如下:

图1 X.21接口板信号流向示意图

2.1.1 机械特性

MAP200E上的X.21接口的机械特性采用ISO4903规定的15插针。公头一般为DTE设备端,MAP200E即为公头。

2.1.2 电气特性

MAP200E上的X.21接口的电气特性符合公版X.21标准的定义。接口数据传输速率小于等于9600kbit/s时,接口电路的电气特性在DCE一侧应符合X.27建议,在DTE一侧应符合X.26或X.27(V.11,RS-442-A)的有关规定。接口数据传输速率大于9600kbit/s时,接口电路的电气特性符合X.27建议的有关规定。

2.1.3 功能特性

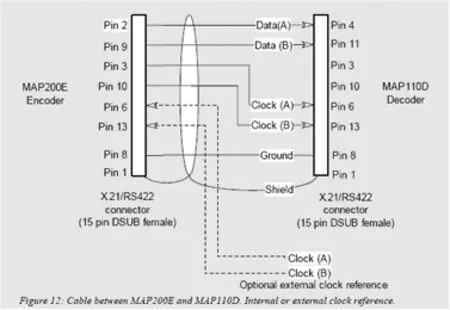

MAP200E上的X.21接口的功能特性不同于公版,其相关定义如下:

图2 MAP200E的X.21接口功能特性

这里需要注意的是Clock ref input信号,其只有在外部时钟工作模式下需要,DAB音频编码采用此格式,所以需要由FPGA产生输入参考时钟。

2.1.4 规程特性

图3 MAP200E的X.21接口信号流向示意图

2.2 基于现有LTC1543的实现方案

2.2.1 LTC1543芯片实现方案分析

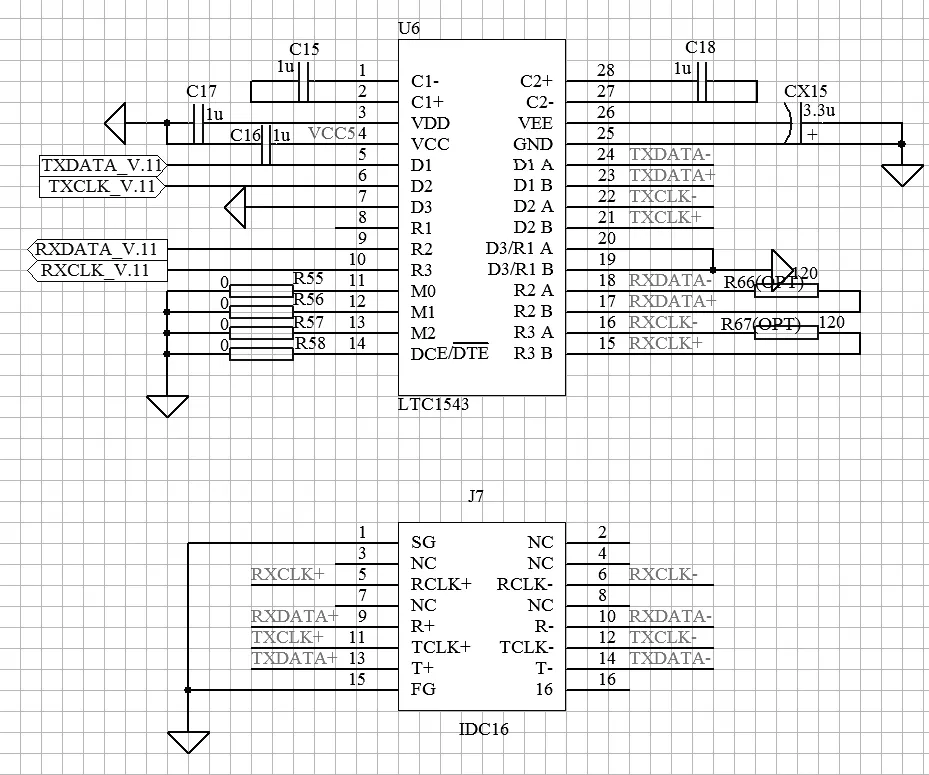

LTC1543工作于+5V 单电源、具有3路发送器/3路接收器的多协议收发器,支持X.21。LTC1543收发器可以传输高速时钟和数据信号,内部电荷泵和专有的低压差发送器输出级在+5V 供电时能够提供与V.11兼容的逻辑电平。所有模式选择引脚(M0、M1和M2) 被拉高或浮空时,器件进入无电缆连接模式。在无电缆连接模式下,电源电流降至0.5μA,所有发送器和接收器输出都被禁止(高阻)。短路限流和热关断电路可避免发送器功耗过大。

图4 LTC1543内部结构示意图

数字接口部分采用单5V 供电的多协议接口芯片LTC1543。这部分电路的主要作用是完成系统中TTL 电平与线路中用户所要求电气性能的相互转换,线路码型为NRZ 码。LTC1543多协议软件可编程数据传输接口芯片与LTC1344多协议软件可编程终端电阻网络配合使用,可使数据处理单元方便快捷地满足用户不同数据格式的传输要求,灵活地选用V.10,V.11,V.28,V.35多种协议。

图5 现有E1接口板上V.11相关电路图

2.2.2 现有E1接口板分析

MAP200E的X.21接口与信号流相关的管脚如下,均为差分信号,有正负端:

输出管脚(DataTx、BitClock) 4pin

输入管脚(Clock ref input) 2pin

对于LTC1534输入输出反向,即在LTC1534上需要两组接收器和一组驱动器(发送器),由现有相关电路设计可以看出,PCB上提供了两组接收器和两组驱动器,可以满足需要,但是由于配置模式管脚被硬配置,现在将其更改为X.21协议模式将PCB上相关的配置管脚的下拉电阻空焊。

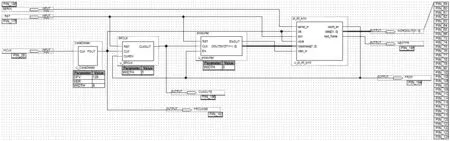

3 STI-PI帧同步模块设计

MAP200E音频编码器的数据流通过LTC1543进行X.21电平转换将串行的STI-PI数据流送入FPGA内部,在这里完成STI-PI帧同步,将同步后的STI-PI数据流送入PCI总线,进行下一步处理。由于暂不考虑后续PCI总线接口的设计,这里FPGA主要完成功能为STI-PI帧同步。

3.1 STI-PI帧同步模块接口定义

图6 STI-PI帧同步模块接口

INCLK:系统工作时钟,32.768MHz

RST:系统复位信号

SERIN:串行数据输入信号

WORDOUT:帧同步后32位数据输出

NEXTFR:读入数据的下一帧号

FRDY:同步完成数据输出标志信号

CLKOUT8:8KHz参考时钟输出

FRCLK256:256KHz参考时钟输出

3.2 STI-PI帧同步内部结构

其主要由以下几个模块构成:

(1)时钟分频模块

由于板上提供的时钟为32.768MHz,这里选取的码流数据率为256Kbit/s,所以对外部时钟进行分频,分频系数为128,产生频率为256KHz的主时钟,同时作为参考时钟送入MAP200E中。

(2)同相时钟产生模块

产生和主时钟相位一致的RAM读地址发生时钟,由于RAM位宽为32,所以读地址发生时钟为256/32=8KHz。

(3)读地址发生器

本质上为一个计数范围为0~255的8位计数器,以产生RAM的读地址。时钟由同相时钟产生模块提供,使能信号由帧同步模块产生。

(4)帧同步模块

利用同步状态机及RAM的乒乓操作实现STI-PI帧的同步,并输出同步后32位宽的STI-PI数据流。

3.3 STI-PI帧同步实现过程

用状态机来控制相应的工作状态,状态机分为四个状态:

图7 STI-PI帧同步系统结构顶层原理图

define SEARCHING_SYNC 0

define GET_FRAME0 1

define VERIFY_FRAME 3

define GET_FRAME1 2

(1)首先进入SEARCHING_SYNC,寻找候选的STI-PI的同步头

Frame0 :24’h1F90CA

Frame1 :24’hE06F35

(2)找到同步头后进入相应的GET_FRAME状态,CNT_SYNC标志+1,同时next_frame输出与当前帧相异的帧号,并将此帧完整读入,存入相应的frameram中(32*192),结束后进入VERIFY_FRAME状态

(3)在VERIFY_FRAME状态中,通过判断CNT_SYNC标志,确定上一帧同步的状况,并验证下一帧的同步字是否与上一帧相异,如结果为真,则CNT_SYNC标志高位置1,进入相应GET_FRAME状态,否则归0,进入状态SEARCHING_SYNC

(4)当CNT_SYNC标志高位为1时进入GET_FRAME状态,则由next_frame生成frame_no,并产生ram读使能信号,将存在frameram中的数据输出

(5) 由frameram0和frameram0实现乒乓操作,用frame_no来判断

4 结束语

MAP200E是一个通用的MPEG-1和MPEG - 2Ⅱ层音频编码器,它提供X.21输出接口,用于DAB系统时需将MAP200E音频编码后输出的STI-PI帧通过X.21接口接入FPGA芯片进行后续处理,在FPGA内将数据流打包封装成PCI接口所需的信号格式,由PCI接口向外输出PCI信号流。本文完成了STI-PI帧同步,将同步后的STI-PI数据流送入PCI总线,进行下一步处理。

[1]ETSI EN 300 401(2006-1),Radio Broadcasting Systems;Digital Audio Broadcasting (DAB) to mobile,portable and fixed receivers[S].

[2]李栋.数字声音广播[M].北京广播学院出版社,2001.

[3]ETSI EN 300 797(2005-5),Digital Audio Broadcasting (DAB),Distribution interfaces,Service Transport Interface (STI)[S].

[4]刘岚.FPGA应用技术基础教程[M].电子工业出版社,2009.

DesignofMAP200EAudioEncoderX.21Interface

SHEN Xiang-hui,YIN Hang

(ECDAV,Communication University of China,Beijing 100024,China)

This paper uses the available multi-protocol conversion chip (LTC1543) on E1 to PCI interface board to access MAP200E audio encoder output data stream (STI-PI frame) to FPGA chip through X.21 interface,achieving STI-PI frame synchronization.

MAP200E;E1;PCI;LTC1543;X.21 interface;STI-PI frame

2010-04-08

沈向辉(1982-),女(汉族),天津人,中国传媒大学广播电视数字化教育部工程研究中心助理研究员.

E-mail:shen_xiang_hui10@sina.com。

TN911.7

A

1673-4793(2013)01-0031-04

(责任编辑:龙学锋)

——编码器