高速核心板的SI仿真与改进*

苏瑞祥 陈少昌 李 超

(1.青岛航保修理厂 青岛 266071)(2.海军工程大学电子工程学院 武汉 430033)

1 引言

SI全称Signal Integrity信号完整性,指的是电路系统中信号的质量及信号在传输后仍保持正确的功能特性。主要包括以下几个问题:

1)延迟[1]:在以往的低速板中,信号在传输线上的传输时间可以忽略,但是对于高速电路板,不能忽略。信号在线上的传输时间产生延迟,会导致数字电路的逻辑产生错误,引起时序问题。延迟主要取决于线长和介质的介电常数。

2)反射[2]:信号在PCB板上传输时遇到阻抗不连续就会发生反射、如过孔、拐角、走线宽度的突变、源端/负载端阻抗不匹配等。有一部分信号被反射回源端,会造成工作效率降低,向外辐射电磁波,影响信号传输从而导致失真。

3)信号振荡[3]:由阻抗不连续产生反射。从负载端返回源端的信号由于源端的阻抗也不匹配在源端又产生反射,从而导致信号在传输线上来回传播。振荡会产生EMI问题。

4)串扰[4]:随着PCB向高密度发展,一块板上集成了越来越多的器件,线路也趋向复杂。信号线由于互感互容引起信号能量耦合到另一条信号线上的现象称为串扰。它会造成信号的失真,数字电路的误触发,甚至会引起器件管脚的损坏。串扰的分析与抑制是一项复杂的工作。

由于振荡究其原因还是由信号的反射引起的,并且延迟是信号的时域问题,本文都不做讨论。本文从串扰和反射入手,提出对S3C2410型核心板的信号完整性分析和改进并给出具体流程与方法。

整板的信号完整性分析应该包括以下几个部分:确定关键网络(关键信号),进行反射和串扰仿真,提出改进办法,验证改进结果。

2 确定关键网络

目前的高速PCB板元器件众多,连线网络复杂。若要每个器件每根连线都进行仿真则工作量太大。选择出易受干扰的和易产生干扰会影响系统工作的关键网络来进行分析[5],这样不仅能够降低工作量,还能有效地找出线路的信号完整性问题。找出关键网络的方法有两种:

1)根据理论知识。一般在高速PCB上容易产生干扰的网络有高频网络,高速网络,数字网络与信号阈值特别低的网络,根据这些元器件的特点,可以在原理图上找出这些网络。在S3C2410核心板上找出的核心网络为[6]:SDRAM的时钟信号,SDRAM的片选信号,CPU与SDRAM之间的数据信号,地址信号等。因为SDRAM的工作频率达到了133MHz,而CPU的工作频率为266MHz。

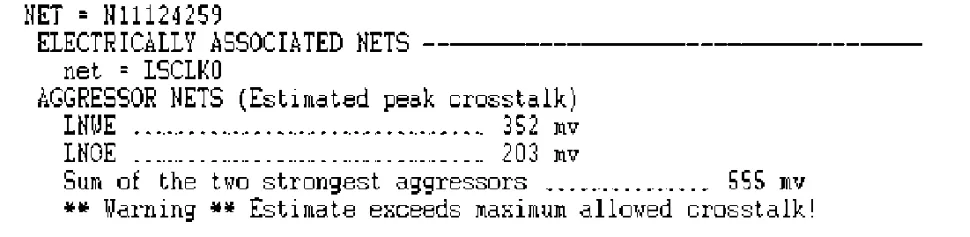

2)利用HyperLynx的快速整板仿真功能[7]。Hyper-Lynx提供了快速的整板仿真,并且不需要器件的IC模型。通过软件仿真,设置串扰阈值为150mV得到所有串扰超过阈 值 的 网 络:LSCLK0,LNWE,LADDR0-24,LDQM0-3,LNOE,NGCS0-5,N11070248,N11070262,LDATA0,1,8,9,LSCKE, LNSCS0,LSCLK1,LNSCAS,LNSRAS,NFRE,NXBREQ,NTRST,L3CLOCK,CLE,TDO,NWAIT,NFCE,NFWE,ALE,L3MODE,NRESET,VD2,TMS仿真结果部分如图1。

图1 快速仿真结果

图1可见对于LSCLK0串扰过强的总共有两个网络,分别为LNWE、LNOE。

设置阈值串扰电压为150mV并不是电路不能承受150mV,只是为了设置一个阈值电压,找出那些串扰比较大的网络。因为快速仿真的精确度并不高,找出关键网络后必须根据PCB各器件所能承受的干扰阈值再进行准确的分析。

一般采用两种方法结合的办法来寻找关键网络。第一种是通过经验寻找,第二种是通过串扰强度分析寻找,两种方法结合后可以优势互补,找出高速PCB板上的关键网络,保证了分析的全面性与准确性。经过验证本组合方法可以有效准确地查找出关键网络。

3 反射串扰的分析改进与验证

在前面一部分内容中已经找出了关键网络,下面以关键网络中的LSCLK0为例进行反射与串扰仿真并改进。

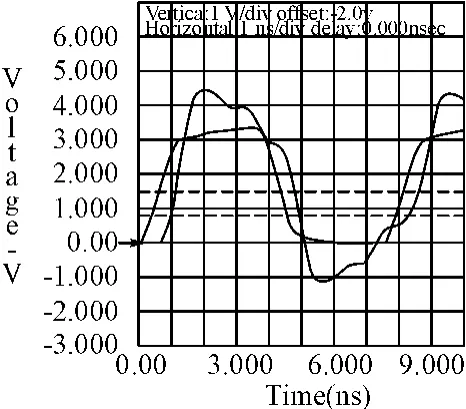

反射:设置LSCLK0网络源端为133MHz,峰值为3.3V的方波驱动,得到负载端波形如图2所示。

图2 改进前反射仿真结果

从图2中得出末端SDRAM接收到的信号正峰值逼近4.6V,负峰值超过-1.0V。由HY57V561620B参考手册知其所有管脚的限制电压为-1V~4.6V,显然网络由反射引起的过冲太大。反射主要是由于网络上的阻抗不连续产生的,包括过孔、拐角、源端/负载端阻抗不匹配等[8]。其中尤以源端/负载端阻抗不匹配影响最大。采用端接技术[9]抑制反射。端接技术分为:串联端接,简单并联端接、戴维南并联端接、主动并联端接、RC并联端接。不同的方法有不同的优势和缺点,采用哪种方法看具体情况而定,这里不再赘述。软件的terminator wizard提示只需在源端串接一个阻值为55Ω的电阻即可改善性能。串接后仿真图形如图3。

图3所示负载端信号波形得到明显改善,并且串联端接方法简单,实行起来也比较方便。所以这里已经不再需要其他的改进办法,包括其他端接方法和对于过孔,拐角的改善。

图3 改进后反射仿真结果

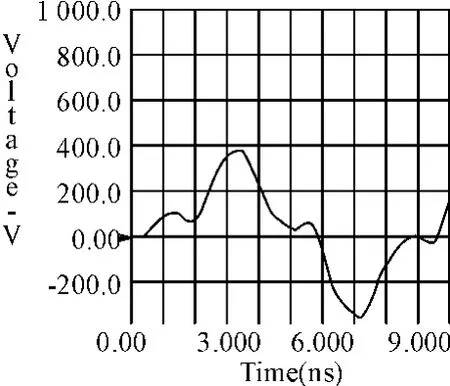

串扰:LSCLK0负载端的接收电平要求为(高2V~3.9V)(低-0.3V~0.8V),并且器件的管脚限制电平为-1V~4.6V,从而得出最大的耦合电压不能超过700mV。从快速整板仿真结果可以看出,LNWE对LSCLK0的串扰强度最大,达到了352mV,其次是LNOE也达到了203mV。虽然两个网络的干扰值之和为555mV并没有超过阈值,但电磁干扰错综复杂,必须为其他未知的干扰留下充足的余量。所以要对网络进行改进。并且快速分析并不够准确,在确定关键网络后可以利用交互式串扰仿真来进行分析。仿真得到波形如图4。

图4 改进前串扰仿真结果

仿真时软件自动给出超过设定耦合阈值150mV的网络有三条,分别是LNWE、LNOE、11070276。源端串扰较小可以不用考虑。负载端串扰强度总和过冲接近于400mV与-400mV,距离700mV的阈值太近,必须加以抑制。一般抑制串扰的方法有增加两线间距和在耦合线间加上一条隔离地线。由于加地线的方法操作复杂,并且耦合网络不仅仅是一条,所以要加的地线也不只一条,这里不建议采用。采用改变走线位置的方法,加大受害线与攻击线的距离,遵循3W原则(即走线间距为走线宽度的三倍)。改进后串扰仿真波形如图5所示。

图5 改进后串扰仿真结果

通过仿真结果可知与LSCLK0产生耦合的网络为LNWE,11070276,与改进前相比少了一个网络LNOE,因为改变走线位置后LNOE对LSCLK的耦合已经低于设定的阈值,所以不再是攻击网络。负载端总耦合强度明显减弱,上下都只达到200mV左右,为700mV阈值留下了足够的余量,符合设计要求。

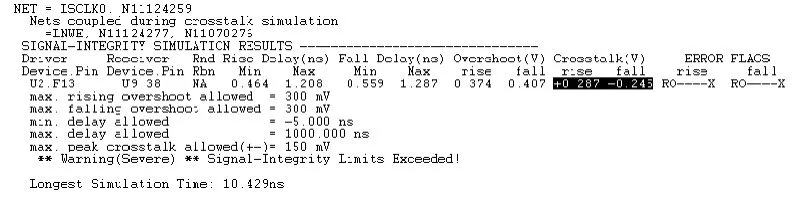

若对于网络LSCLK0的攻击网络过多,在交互式仿真时会耗费大量的时间,所以这时可以采用详细整板仿真的方法[12]。图6所示为改进前的详细仿真结果,其中串扰强度为432mV和-395mV。改进后仿真结果如图7所示,串扰强度下降为287mV,-245mV。

图6 详细整板仿真结果

图7 改进后详细整板仿真结果

综上所述,对某型高速PCB板进行信号完整性分析时,首先要先确定关键网络(采用经验,快速仿真结合组合的办法)。然后利用交互式办法对反射进行仿真与改进。对于串扰可以先采用交互式办法,若网络复杂可以再采用详细整板仿真,分析并改进。

4 结语

本文基于HyperLynx软件对S3C2410核心板进行了信号完整性的分析,从反射与串扰入手说明了分析方法与改进方法,并对改进前后的仿真结果做了比较。总结了对于任何高速PCB板进行信号完整性分析的一般性方法和步骤。提出了查找关键网络的组合方法。但是由于S3C2410核心板的IBIS模型不易获得,所以采用了Hyper-Lynx软件提供的通用模型,对仿真结果有一定的影响。

[1]卓沛,严国萍.高速数字系统中的时序分析与设计[J].计算机技术与发展,2007,17(7):23-24.

[2]杨华.高速PCB电磁兼容性分析与研究[D].武汉:海军工程大学,2011:77-90.

[3]贾凯宾.高速数字PCB互连设计信号完整性研究[D].南京:南京理工大学,2008:48-53.

[4]曹海舟.减小PCB微带线间串扰方法分析[J].电子质量,2008(1):19-24.

[5]刘波.高速数字电路信号完整性和电源完整性的研究[D].西安:西安电子科技大学,2011:27-31.

[6]吴昊.高速数字电路板级信号完整性分析及其应用[D].武汉:海军工程大学,2008:55-57.

[7]张海风.HyperLynx[M].北京:机器工业出版社,2006:4-70.

[8]王宗跃.高速PCB信号完整性分析与研究[D].武汉:海军工程大学,2009:30-35.

[9]郝丽翠.高速互连设计中的信号完整性分析[D].南京:南京理工大学,2009:52-60.

[10]许建平.军用计算机信号完整性分析与设计[J].计算机与数字工程,2012,40(1).

[11]谭力,苏钢,朱光喜,等.多天线系统中的高速串行互联总线的信号完整性[J].计算机与数字工程,2008,36(9).

[12]赵光.PADS2007高速电路板设计[M].北京:人民邮电出版社,2009:26-33.