基于VxWorks的PCI-CAN总线交换及驱动开发

郑 炜

(广州海格通信集团股份有限公司,广州510663)

1 引 言

某通信控制平台系统方案中对数据传输总线的设计是通信控制平台单机内的主板数据传输总线采用工业控制领域成熟的PCI总线,其数据传输速率高,可靠性高,可即插即用;平台的外部远程遥控总线采用国际标准的现场总线CAN,具有传输字节短、速度快、容错性好、数据传输可靠等特性[1],有效支持分布式控制和实时控制,支持多主方式,总线上分布的任意节点均可主动向其他的节点发送信息。

为实现外部遥控命令直接送到平台控制板的嵌入式处理器中,需要设计高速、低成本的PCI-CAN总线交换电路。文献[1-3]主要介绍了CAN总线的特点、总线标准及应用,以及芯片 PCI9052和SJA1000的应用方案和设计要求,文献[4]主要介绍了VxWorks操作系统下开发PCI总线驱动程序的基本方法。本文结合设计需求和文献相关内容设计开发了PCI-CAN总线交换的硬件电路和驱动程序,并给出了设计中的关键点和处理建议。

2 硬件设计

2.1 总体方案设计

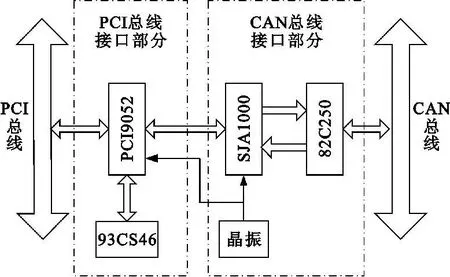

PCI-CAN总线交换硬件电路设计主要由PCI桥芯片PCI9052、CAN总线控制器SJA1000和CAN总线驱动器PCA82C251组成。

PCI9052兼容PCI V2.1规范,支持目标设备的直接数据传输,具有4个片选空间,可通过I/O空间映射或Memory空间映射将PCI总线访问直接映射到局部总线访问,局部总线支持8位、16位或32位总线模式[2]。设计中PCI总线和局部总线端均采用Little Endian模式。

SJA1000是独立的CAN总线控制器,位速率可达1 Mb/s,兼容CAN2.0B协议[3]。PCA82C251是用于CAN总线与总线控制器SJA1000之间的物理接口驱动芯片,最高传输速率为1 Mb/s,抗干扰能力强,具有芯片热保护能力。

传统设计方案会在PCI9052与SJA1000之间加一级控制芯片和双口RAM,以方便进行协议解析和数据缓存,但同时会增加总线数据协议转换的处理延时。本方案考虑到降低成本和转换延时的要求,以及考虑到实际使用中遥控终端与通信控制平台间的控制命令、数据交互并不频繁,协议中的单帧数据指令不长,不会因频繁的中断和数据读写影响嵌入式处理器的实时性能,因此设计中直接使用PCI9052的局部总线以数据地址复用方式访问SJA1000,原理框图如图1所示。

图1 硬件原理框图Fig.1 Schematic diagram of hardware

2.2 CAN总线接口电路设计

如图2所示,CAN接口电路由PCA82C251总线驱动器实现总线控制器SJA1000与CAN总线间的物理接口,R37为斜率电阻,需根据实际的总线传输速率进行调整,取值范围一般在10 Ψ~100 kΨ之间。

图2 CAN接口电路原理图Fig.2 The CAN interface circuit

SJA1000与PCI9052之间采用局部总线的地址数据复用方式连接,PCI9052需通过MODE管脚的上拉配置为复用方式。在软件的驱动配置过程中需对PCI9052的相关寄存器进行配置,将其局部总线位宽设置为8 b,同时配置CS0片选空间的基地址和范围,本例为24000h和4000h,其余寄存器保持上电默认值的状态下即可通过PCI9042的Memory空间将PCI总线地址的访问直接映射到局部总线CS0片选空间的地址访问。

LINT为中断信号,设计中配置为边沿触发,当SJA1000接收到CAN总线上的有效数据后拉低该信号线,由PCI9052转换成PCI中断通知嵌入式处理器来读数据,缩短处理器的响应时间。LCLK为局部总线的时钟输入信号,为保证PCI9052与SJA1000之间读写数据的有效性,保持地址数据建立和保持时间的一致性,设计上将LCLK与SJA1000的时钟输入接到同源时钟上。

SJA1000的复位输入信号由PCI9052的LRESET#输出管脚产生,满足复位时间要求,同时可以保证两者上电后初始化配置顺序的合理性。SJA1000可通过MODE管脚选择工作于Intel或Motorola模式,本例设计为上拉,即采用Intel模式。

调试过程中,应重点关注CS0片选信号有效时,对应的地址/数据是否正确,其与读写信号、时钟信号间的时序关系是否正确以及ALE锁存是否工作正常。在对SJA1000进行初始化配置时建议将时钟分频配置为1/4以区别于默认的1/2时钟分频设置,这样可以通过CLKOUT管脚的时钟输出频率值判断是否初始化配置成功。

2.3 PCI总线接口电路设计

如图3所示,PCI接口部分的电路主要由PCI9052和NM93CS46组成,NM93CS46为支持连续数据读写的EEPROM,存储空间为1 kb,EEPROM用于存储PCI配置寄存器的初始化配置数据,在上电后PCI端口自动读取EEPROM中的数据执行初始化操作。需要注意的是PCI9052仅支持1 kb的可连续数据读写的EEPROM,常用型号如93C46、93C56的芯片不能支持。

PCI9052的EEDO管脚用于选择是否从EEPROM读取值来进行自动初始化,当该管脚配置为下拉时,可选择使用PCI9052的默认值来进行自动初始化。TEST管脚在芯片正常工作时一定要下拉或直接接地。建议设计中将PCI总线侧的控制和地址/数据信号线串接33 Ψ的吸收匹配电阻,降低信号线阻抗失配引起的信号反射,提高信号完整性。硬件PCB设计过程中需要注意PCI总线侧信号线的长度差要控制在一定的范围,通常不超过100 mil。

图3 PCI接口电路原理图Fig.3 The PCI interface circuit

3 软件设计

3.1 驱动程序设计

通信控制平台的嵌入式处理器运行的操作系统是VxWorks,需要开发基于VxWorks的驱动程序对PCI桥芯片PCI9052和CAN总线控制器SJA1000进行初始化配置。

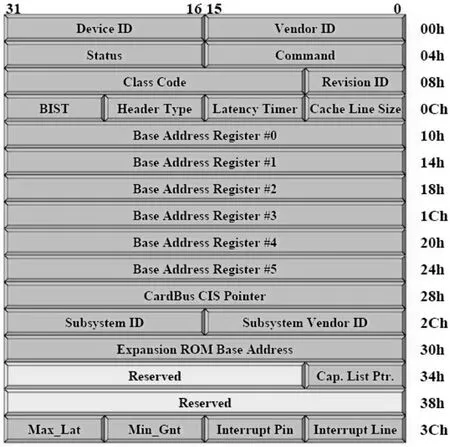

标准PCI设备要求具有3种地址空间:配置空间、Memory空间和I/O空间[4]。上电后,驱动程序扫描PCI总线,并通过设备的配置空间确定PCI总线上的PCI设备和配置要求,以进行系统初始化配置。配置空间可分为头标区和设备有关区两部分,头标区的长度为64 B,结构内容如图4所示。

图4 PCI总线配置空间头标区寄存器Fig.4 Registers in PCI bus configuration space

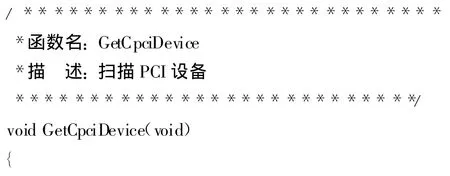

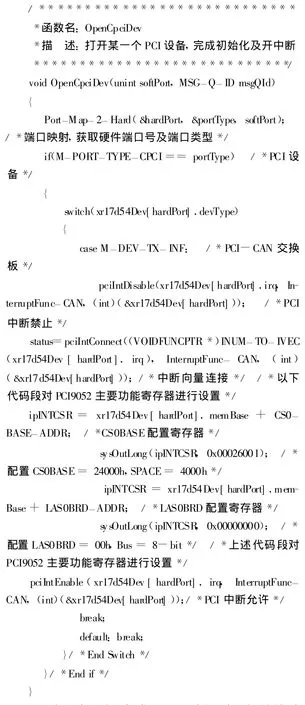

PCI设备驱动程序的基本流程是查找PCI设备、确定厂商ID、设备ID、基地址等配置信息,初始化PCI设备、设置中断服务函数的入口地址及启动功能模块。具体程序流程图如图5所示。

图5 PCI设备驱动程序流程图Fig.5 The PCI device driver program process

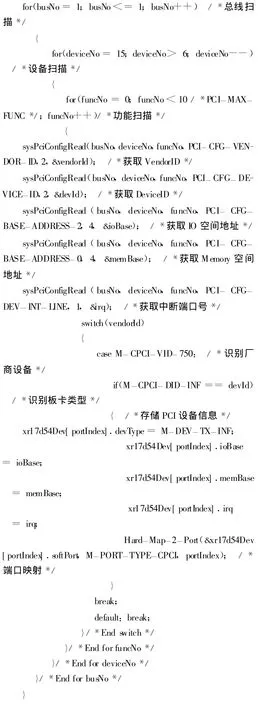

驱动程序启动后首先启动GetCpciDevice查找PCI设备、确定厂商ID、设备ID、基地址等配置信息,然后进行软硬件端口号的映射。

通过上述操作后,可以通过对Memory空间地址的访问实现对PCI9052配置寄存器的访问。程序中的sysPciConfigRead函数为VxWorks提供的标准PCI驱动库函数。程序找到PCI设备后,执行OpenCpciDev函数对PCI设备进行初始化以及中断配置、开中断等。

通过上述程序,完成了PCI地址到局部总线地址的映射,随后可以通过对起始地址为90124000h(其中90100000h为I/O空间基地址),大小为4000h的地址范围的访问实现对SJA1000的内存访问。

程序中的中断挂接函数主要完成挂接中断,将中断向量和中断服务程序相关联。VxWorks为用户提供了PCI中断挂接函数pciIntConnect,该挂接函数将PCI中断服务程序InterruptFunc-CAN加入到中断服务链表中。同时,程序调用了标准PCI驱动库函数中的pciIntDisable和pciIntEnable来开关PCI中断,调用sysOutLong执行PCI空间的数据读写操作。

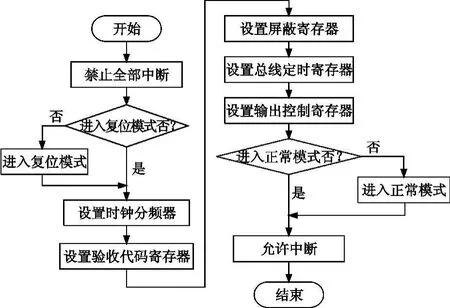

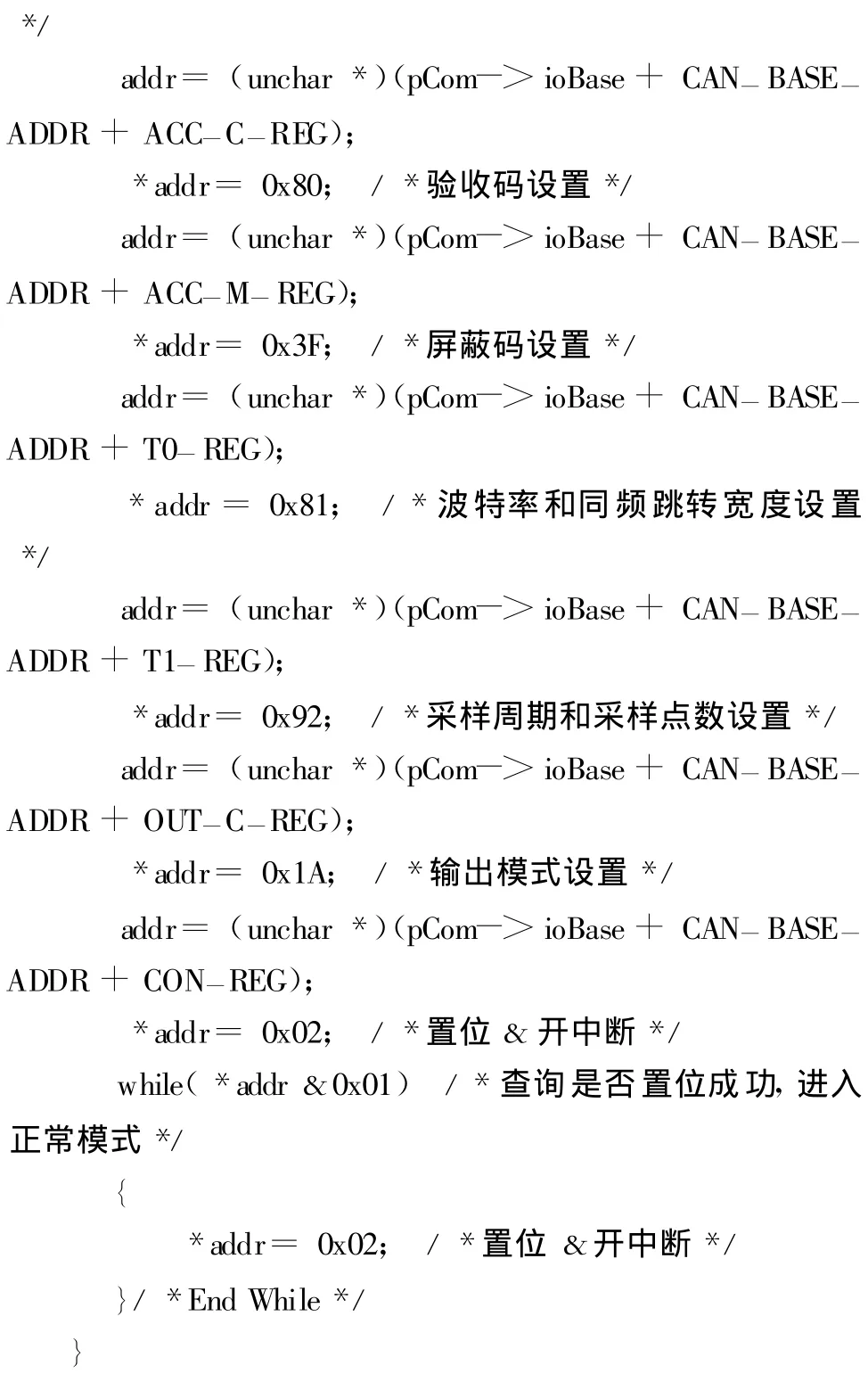

3.2 SJA1000初始化程序设计

CAN总线控制器SJA1000的初始化是CAN接口电路驱动程序设计的重要部分,成功的初始化配置是保证CAN总线数据正确接收和发送的基础。程序初始化过程中要设置的芯片工作参数主要有:选择SJA1000的工作模式,设定总线通信波特率,设置验收码寄存器和验收屏蔽寄存器等。程序初始化流程图如图6所示。

图6 SJA1000初始化流程图Fig.6 SJA1000 initial program process

设计中CAN总线控制器SJA1000的输入时钟为12 MHz,CLKOUT管脚上电后默认输出为输入时钟的1/2,即6 MHz,当执行上述代码完成对芯片初始化配置后,CLKOUT输入变为3 MHz,表明初始化成功。其后即可通过读写SJA1000的接收和发送寄存器完成CAN总线数据的收发操作。

4 应用情况

研究成果已成功应用于某短波通信产品的通信控制平台中,并随系统产品通过了常温功能和性能测试、环境试验、用户试用以及定型评审。各项测试结果表明,本方案的设计成果可实现PCI和CAN总线间的数据交换,功能正常。性能测试方面,从CAN总线接收到遥控数据命令开始,到完成数据协议转换并以中断方式通知嵌入式处理器读取为止,所计平均延时时间为0.3 μ s,最大延时不超过0.5 μ s,优于传统方案,且生产成本降低了30%。本方案设计简单、成本低、延时小,满足高速、实时处理的要求,且具有很好的兼容性和通用性,可移植应用于各种有类似功能需求的产品中。

5 结束语

本文针对低成本、低时延和实时处理的设计需求,设计了低成本的PCI-CAN总线交换硬件实现方案和驱动程序,对比传统实现方案,在数据时延和实时处理的性能方面有较大的提升,且实现简单、成本更低,更有利于实际产品的批量生产。同时,结合实际调试经验,指出了软硬件设计和调试过程中的关键点,给出了相应的建议和指导,并对软件源代码进行了详细的解读,对工程应用中此类功能需求的设计开发具有一定的参考价值。

[1]邬宽民.CAN总线原理与应用系统设计[M].北京:北京航空航天大学出版社,2004:32-158.WU Kuan-min.Principle andApplication of CAN BusSystem Design[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2004:32-158.(in Chinese)

[2]PLX Technology Inc.PCI9052 Data Book v1.02[EB/OL].2000[2012-06-25].http://www.plxtech.com/products/io/pci9052.

[3]岑雪松.SJA1000在CAN总线系统节点的应用[J].单片机与嵌入式系统应用,2002(3):50-54.CEN Xue-song.Application of SJA1000 inthe SystemNode of CAN Bus[J].Microcontrollers&Embedded Systems,2002(3):50-54.(in Chinese)

[4]王宇磊,周东.VxWorks下PCI总线驱动程序设计与实现[J].自动化与仪表,2008(7):45-48.WANG Yu-lei,ZHOU Dong.Driver Design and Realize of PCI Bus Under VxWorks[J].Automatization and Instrument,2008(7):45-48.(in Chinese)