可编程FM锁相发射机的实现

宋小勇,王晓远,宋里瑾

(中国空空导弹研究院 河南 洛阳 471009)

调频技术是遥测通信中的关键技术,广泛应用于各种遥测系统中。文中设计一种基于Atmega8的FM锁相发射机,可实现发射频率和调制频偏的可编程。

1 FM锁相发射机原理

调制信号首先经过调制电路进行电平转换与幅度调整,然后与环路产生的误差电压相加,控制压控振荡器。由于环路带宽低于调制频谱的下限,因此调制信号不参与环路的反馈,使压控振荡器仍锁定于中心频率,实现调制信号对载波的频率调制[1]。其原理如图1所示。

图1 锁相调频发射机原理图Fig.1 FM transmitter based on PLL schematic diagram

2 FM锁相发射机电路实现

锁相调频发射机的核心是锁相环路及调制电路的设计。发射机输出频率的可编程,可以通过单片机对锁相环芯片的编程来实现。在本设计中,锁相环芯片采用ADF4107,可通过LE、DATA、CLOCK 3个端口实现输出频率的可编程。

调制频偏通过分压电路来实现,在设计中可以利用数字电位器来进行分压,通过对数字电位器的编程来实现调制频偏的可编程,数字电位器选用AD5259。

控制单片机采用Atmega8,支持多种串口通信模式,包括TWI、SPI及USART,可实现与外部主机的串口通信及芯片控制功能。本设计中,Atmega8与上位机的通信采用USART协议端口实现,与数字电位器的通信采用TWI协议端口实现。

2.1 锁相环电路设计

锁相环电路包括参考晶振、锁相环芯片、压控振荡器和环路滤波器。参考晶振选用40 MHz,压控振荡器选用S波段双路电压控制、双输出的振荡器,锁相环芯片使用ADF4107,其内部集成鉴相鉴频器、分频器、电荷泵等,通过改变内部寄存器的值能够实现频率的可编程。环路滤波器具有低通作用,用来滤除电压中的高频分量和噪声。它对环路参数调整起着决定性的作用,可以改善控制电压的频谱纯度,提高系统稳定度[2-3]。考虑鉴相频率的泄漏问题,本设计采用3阶有源环路来实现,其电路图如图2所示。

图2 有源环路滤波器电路图Fig.2 Active loop filter circuit diagram

利用仿真软件ADIsimPLL对所设计锁相环进行仿真,得到其开环传递函数的增益与相位曲线,如图3所示。

图3 输入信号的开环频率响应关系图Fig.3 Open-loop frequency response of input signal

本设计中,鉴相频率设定为5 kHz,环路带宽100 Hz,由上图可以看出该环路滤波器的相位裕量大于45,可以保证环路较好的稳定性[4]。对鉴相频率的抑制大于60 dB,能够保证发射机具有较小的寄生调频。

2.2 调制电路设计

调制前端的分压电路如图4所示。

图4 调制前端电路Fig.4 Modem front circuit diagram

数字电位器Rab中a为输入端,w为输出端,在w与地之间存在分布电容Cw,典型值为3~80 pF,选用的数字电位器AD5259的Cw为60 pF。该分布电容的存在使电位器呈低通特性,等效电路图如图5所示。

图5 数字电位器的等效电路图Fig.5 Digital potentiometer equivalent circuit diagram

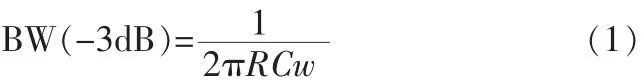

由式(1)可得,AD5259-10 的带宽为 1 061 kHz,该带宽不能满足现有的调制信号需要。在设计中,在可调电位器的aw,wb之间分别接一相同阻值的电阻,扩展其带宽,此时其等效电阻 R=(Raw//R3)//(Rwb//R4)。 因 R3=R4,所以 Raw=Rwb时,等效电阻最大,此时的R值即对应于低通滤波器的截止频率。经计算,当R3=R4=2 kΩ时,带宽可扩展为3.5 MHz,能够满足现阶段需要。同时为了增加发射机的输入阻抗,满足采

该低通电路的-3 dB带宽在数值上等于低通滤波器的上限截止频率fC,即编器的带负载能力,在a端串联电阻R1。为了提高数字电位器的分辨率,在b端与地之间串接电阻R2[5]。

因压控振荡器的输入端存在对地电容,为了提高其频率响应,输入端要求低输入阻抗。采用运算放大器MAX4016设计一电压跟随电路,具有输入阻抗高输出阻抗低的特点,且其有高达350 MHz的增益带宽积,能够响应10 MHz以上的信号。

3 下位机软件实现

发射机的可编程通过上位机与Atmega8的串口通信来实现,在上位机的操作界面上输入设定的输出频率值或调制频偏值,通过串口发送给Atmega8。Atmega8根据接收到的值,对ADF4107或AD5259进行配置,从而实现可编程功能。约定一次有效设置发送的数据帧格式如下:

表1 配置数据帧格式Tab.1 Figuration data frame format

帧头为0x0F时判定为对输出频率进行编程,帧头为0xF0时判定为对调制频偏进行编程,帧头为其他数据时判定为无效数据,需重新配置。程序流程图如图6所示。

图6 下位机软件流程图Fig.6 Hypogenous machine software flow chart

3.1 串口通信实现

ATmega8单片机带有一个全双工通用同步/异步串行收发模块USART,有独立的高精度波特率发生器,支持5、6、7、8和9位数据位、1位或2位停止位的串行数据帧结构[6]。设计中采用中断的方式来实现接收功能,波特率设定为9 600 bps,采用8位数据位、无校验、1位停止位的数据帧结构。中断响应函数如下:

Atmega8完成一次中断响应后,数据保存在数组rx_data[]中,主程序根据接收到的数据调用频率或调制频偏配置函数。

3.2 配置函数设计

输出频率配置通过改变ADF4107控制字来实现。ADF4107共有4个控制寄存器需配置,输出频率改变时仅N寄存器改变即可,Atmega8与 ADF4107之间遵循 SPI通信协议。对ADF4107配置时,接收到的数据以unsigned char形式保存在三字节的数组中,需要转换成24位的寄存器控制字。

调制频偏配置通过改变AD5259的RDAC寄存器值来实现。Atmega8与AD5259之间遵循TWI通信协议。该通信协议需两根双向信号线,一根是数据线SDA,另一根是时钟线SCL,通过上拉电阻接正电源。每个接到I2C总线上的器件都有唯一的地址。主机发送地址时,总线上的每个从机都将这7位地址码与自己的地址进行比较,如果相同,则认为自己正被主机寻址,根据R/T位将自己确定为发送器或接收器。

配置函数设计时,首先对各个寄存器进行初始化,再按照配置时序向各个寄存器写入预定的值。需要注意的是,TWI协议中每一个传送字节后面都必须跟随一位应答位,且SCL位为高电平时,SDA不能有上升或下降沿出现,否则就重新开始一个字节的数据传输或中断本字节传输。

4 结束语

该可编程发射机在不进行硬件改变的情况下,实现了输出频率和调制频偏的可编程,提高了发射机的通用性。该发射机频率覆盖 2 200~2 300 MHz,调制响应 100 Hz~3.5 MHz,能够满足大部分FM体制下的遥测任务需求。

[1]张厥盛,郑继禹.锁相技术[M].西安:西安电子科技大学出版社,2003.

[2]DEAN BANERJEE.PLL Performance, Simulation, and Design[M].Handbook 4th Edition,2006.

[3]石春燕.射频锁相环频率合成器的分析与设计 [D].南京:河海大学,2006.

[4]Thompson I V,Brennan P V.Fourth-order PLL loop filters design technique with invariant frequency and phase margin[J].IEE proc.-Circuits Devices Syst.,2005(152):2.

[5]沙占友.数字电位器应用指南[M].北京:化学工业出版社,2008.

[6]马潮.Atmega8原理及应用手册[M].北京:清华大学出版社,2002.