双MicroBlaze软核处理器的SOPC系统设计※

李金凤,施慧彬,杨定定

(南京航空航天大学 计算机科学与技术学院,南京 210016)

引 言

随着时代的发展,单核片上可编程系统SOPC(System On a Programmable Chip)解决复杂问题的能力与处理速度已很难满足用户的需求,面向多处理器SOPC系统的设计成为片上系统发展的必然趋势[1]。具有高密度、大容量逻辑的FPGA(Field Programmable Gate Array)的出现使得高性能片上多处理器的设计成为现实。目前,片上多核系统的设计已有一定发展,但在处理器间通信和中断方面仍需进一步的研究。本文在处理器间通信和中断控制方面进行了深入的研究。

MicroBlaze是一个被优化过的可以在Xilinx公司FPGA中运行的软核处理器,可以和其他外设IP核一起完成可编程系统芯片的设计。它具有运行速度快、占用资源少、可配置性强等优点,广泛应用于通信、高端消费市场等领域[2]。MicroBlaze处理器采用 RISC(Reduced Instruction Set Computer)指令集结构和哈佛存储结构,指令、数据总线位宽均为32位。本文MicroBlaze处理器采用面积优化,流水线分为3级,即取指、译码和执行,减少了硬件开销[3]。

1 系统设计

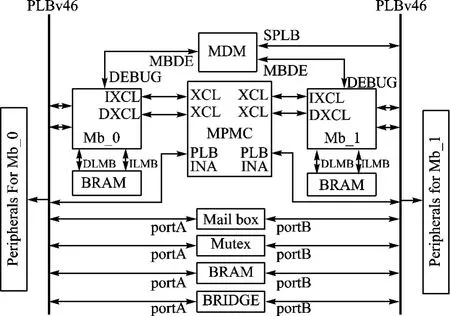

1.1 双MicroBlaze SOPC系统结构

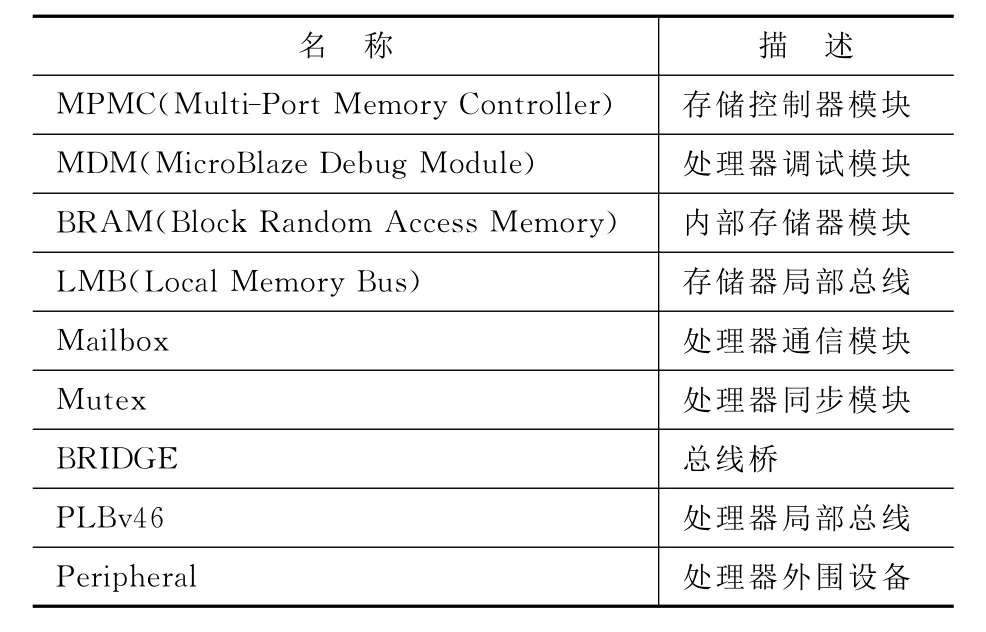

双MicroBlaze SOPC系统结构图如图1所示。从图1中可知,整个SOPC系统可以分为两个处理器子系统。系统采用两个PLB(Processor Local Bus)v46总线作为系统的通信结构,所有的模块都是直接或间接地连接到这两个总线上[4]。两个总线上均挂有用于处理器间通信和同步的核,即 Mailbox和Mutex,因此两个处理器并不是完全独立的。表1列出了SOPC系统包含的主要模块。

表1中的BRAM有两种用途:一是作为单个处理器的私有存储器用来存储指令和数据,它通过存储器局部总线LMB与处理器相连;二是作为两个处理器之间的共享存储器(Shared Memory)用作通信模块进行数据传输。它所传输的数据量比Mailbox大很多,特别是在传输信息量大于千字节时,共享存储器是最常用的通信模块[5]。

图1 双MicroBlaze SOPC系统结构图

表1 SOPC系统的主要模块

1.2 硬件设计

1.2.1 硬件结构

图1所示的SOPC系统的整体结构不仅和处理器的数目有关,还和系统中模块的配置及功能有关,外部存储器和外围设备的不同配置都会影响系统的结构和功能[1]。具体如下:

①SOPC系统通过各自独立的PLBv46总线隔离两处理器子系统,可以确保两个处理器系统在执行各自的处理器事务时不会相互干扰。

② 共享模块(例如MPMC),采用多端口结构,这些多端口模块使多个处理器在访问共享模块时可以并行进行。

③ 两个独立的 MicroBlaze处理器Mb_0和 Mb_1,通过共享部件连接在一起,这些共享部件使得两个 Micro-Blaze处理器之间以各种方式通信。

④此SOPC系统中有两个MicroBlaze处理器软核,其中任何一个MicroBlaze都可以灵活地被其他类型的处理器所代替,比如PowerPC,因此处理器的选择是非常灵活的。

⑤两个处理器可以共享互斥访问设备,比如串口UART、串行外设接口 SPI(Serial Periphieral Interface)等,这种情况需要在没有直接连接此外设的总线和直接连接此外设的总线之间提供一个系统总线桥[6]。

⑥ 关键的外围设备是外部存储控制器MPMC,它最多提供8个端口,可以通过XCL(Xilinx Cache Link)连接处理器局部存储器(BRAM),通过PLBv46总线连接到系统中,因此,可以将1~4个处理器同时连接到MPMC控制器上。

⑦ 两个处理器之间的Mailbox和Mutex有简单通信的功能,主要体现在处理器之间的通信和同步上。

1.2.2 存储器映像

当程序没有被加载或者运行的时候,它以文件的形式存放在硬盘上。当它被下载到MPMC内存中的时候,系统会自动从MPMC内存中划分出一段区域,用来将这个磁盘上的文件映射到内存相应的位置上。此时这块内存中的数据就是磁盘文件的一个拷贝。存储器映像就是指和被加载的磁盘文件相对应的一块内存区域。由于MPMC存储器和外围设备是统一编址的,两者的地址范围不可能重叠,因此直接或者间接连接到处理器上的外围设备地址的分配决定了外部存储器的地址空间[7]。

一般而言,当多个处理器共用一条总线时,存储器、外围设备和共享元素是密不可分的,在本文设计的处理器系统中,每一个处理器都有自己独立的系统总线,因此,所有的存储器和外围设备与共享元素都是分开的。也就是说,不同总线上的相同外围设备可以有相同的地址范围。在每一个处理器子系统中,为了能够运行可执行文件,对存储器映像有一些要求。每个处理器都必须将自己的可执行文件加载到各自私有的MPMC地址空间中,可执行文件加载地址不能重叠。在私有存储器里必须有各自的复位和中断存储器映像,这种私有存储器可以通过本地存储器接口(XCL)或者PLBv46总线接口连接起来。一旦私有存储器与其他总线连接完毕,XPS的地址发生器会为每一个MicroBlaze处理器子系统(包括外围设备和存储器)生成适当地址范围的存储器映像。

1.2.3 处理器之间的通信与同步

在Xilinx SOPC系统设计中,常用的处理器之间的通信模块是Shared Memory和 Mailbox,同步控制模块是Mutex,调试模块是 MDM[7]。

Shared Memory共有两个通信端口,它通过存储器控制端口分别连接到系统的两条PLBv46总线上。系统通过处理器对Shared Memory模块进行读写操作完成通信。Shared Memory可以由片上本地存储器或者外部存储器构成。当信息传输量比较大时,Shared Memory的异步传输效率比较高,它支持零拷贝或者原状信息队列拷贝。

利用Mailbox也可以进行处理器之间的通信[8]。关于Mailbox,有如下一些特征描述:

① Mailbox可以认为是处理器之间的类似于TCP/IP的一个简单的通信协议。

② 处理器之间通过Mailbox通信有同步和异步之分:同步主要体现在处理器之间的通信上,接收者实时地读取Mailbox中的数据;异步主要体现在处理器之间的中断上,发送者通过Mailbox发送中断信息给接收者,接收者收到中断后反馈给发送者。

③ 每一个Mailbox核都有一个FIFO和一个双端队列,分别用来发送和接收信息,用户可以根据自己的需要对它们的深度进行配置,主要通过分布式的RAM或者BRAM来实现。

④ Mailbox共有两个端口分别连接到系统的两个总线上来实现处理器之间的通信。

⑤ Mailbox软核比较适合传输信息量小于100字节的信息,发送者需要从本地或者外部存储器拷贝整个信息到FIFO,然后,接收者同步地拷贝整个信息到自己的存储器中,因此,Mailbox不适合传输信息量较大的信息,这些将会耗费掉处理器的一些时钟周期。

⑥ 处理器间的中断是指一个处理器去中断另一个处理器的行为,通过Mailbox的异步通信来实现,处理器发送中断就是往Mailbox里写入一个信息,然后Mailbox通过中断控制器对接收者产生一个中断,接收者收到中断以后会反馈给发送者,当Mailbox中没有新的信息时,中断为无效状态。

本文在SOPC系统设计中,用到的同步控制模块是Mutex[7]。此模块主要有以下特点:

① 存储器映像以后,Mutex寄存器的数量可配置这些寄存器中有分别存储数据和处理器ID的区域,Mutex寄存器中的数据和ID分别通过Mutex进行测试和设置。

② 复位时,Mutex的值变为0,它表示Mutex处于开锁状态(UNLOCK),并且其中的处理器ID号没有赋值,当Mutex处于锁定状态(LOCK)时,其中的值保持不变。

③ 处理器通过软件赋值的方式将各自的处理器ID号写入到相应的Mutex寄存器中,从而获得Mutex的使用权,当两个处理器同步访问Mutex寄存器时,每个处理器都会读取Mutex寄存器中的值,然后和自己的ID号进行比较,比较匹配的处理器才可访问Mutex寄存器,修改其中的数据。

MicroBlaze核通过处理器调试口与MDM(Microprocessor Debug Module)调试模块相连[4]。调试模块 MDM可以调试系统中的每一个处理器。MDM的特点如下:

① MDM的调试端口数目是可配置的,最多可以达到8个。

② MDM提供一个JTAG UART接口通向系统中的某个处理器,这个UART接口是通过PLBv46总线接口连接到处理器上的。

③ MDM不会自动地调试每个处理器,用户必须通过输入调试命令来进行选择性的调试。

1.3 软件设计

1.3.1 存储器映像

为了保证每个处理器在执行软件部分时不发生冲突,必须对其存储器进行存储器映像[8]。图2是存储器映像图。

图2 处理器的存储器映像图

从图2中可以看出,用户可以灵活地为两个ELF文件分配适当大小的存储器空间作为ELF文件的映射地址范围。由于boot(引导)存储器不可以共享,所以ELF文件的boot部分(.vectors*)被映射到私有存储器中,它可以实现MicroBlaze处理器随时调用,也可以引导ELF文件加载到DDR中。Heap和stack的范围表示ELF文件在DDR中映像的存储器大小。boot存储器的大小表示boot部分所能引导的DDR的范围。ELF文件的位置和输出链接脚本的位置可以根据用户的需求选择。每个可执行文件的存储器映像地址都是通过编译器来实现的,实现以后被传到链接器,生成链接脚本[9]。

1.3.2 通信与同步

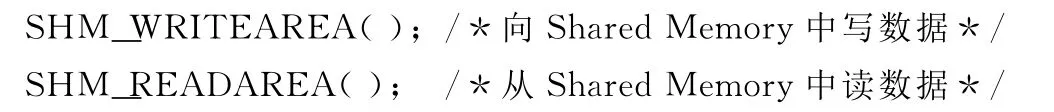

利用Shared Memory模块通信是处理器之间最常用的通信方式。其通信接口函数如下:

利用Mailbox模块可以实现处理器之间的信息传递和中断。这在软件设计中主要体现在以下代码行中:

在软件应用设计中,两个处理器之间的同步是通过Mutex Locks实现的,它的状态有LOCK和 UNLOCK之分。Mutex状态的操作主要体现在以下命令行中:

软件的调试(debug)需要手工地选择处理器,两个处理器不可以同时调试[10]。在XMD Console中的调试命令主要有:

2 实验结果

本设计采用调试模块分别对两个处理器进行调试,通过超级终端输出测试结果。

2.1 Mailbox的测试结果

通过Mailbox可以实现处理器之间的中断和通信。两处理器首先通过交换字符串“helo BOY”的形式汇合(rendezvous),以此来证明两个处理器的连接情况。在这里,每次发送的数据包为2 044字节,共发送了3个数据包,都能成功地发送。经验证,每次发送的信息量最大为4 096字节,可以重复发送。

2.2 Mutex的测试结果

通过Mutex可以实现两处理器的同步。当两个MicroBlaze处理器访问共享资源时,可以用Mutex核修改临界区域里共享资源的值。临界区域里的值是随着处理器的访问而更新的。在没有输出时处理器会锁定 Mutex核,有输出时解锁 Mutex核。同步使得控制台的输出结果正确可用,不会出现混乱的状态。

2.3 Shared Memory的测试结果

通过Shared Memory实现处理器之间的通信。处理器0首先向共享存储器中写入一个32位的数据并设置一个共享flag表明数据可用,等待处理器1读取这个数据。然后,处理器1从共享存储器中读取处理器0写入的数据并设置一个共享flag表明它已经读取了这个数据。双处理器会重复这样的过程,直到达到所设置的最大数目12[8]。

编者注:实验测试结果图略。

结 语

本文以MicroBlaze软核为基础,利用XPS作平台来设计双MicroBlaze处理器片上系统,此片上系统可以很好地实现两软核处理器间的通信和中断功能,该系统在Xilinx公司的XUPV5-LX110T开发板上得到实现,在超级终端中得到验证。本设计的优点是把处理器核之间的通信、中断、同步放在了同一系统中进行研究,深入研究了处理器之间的中断控制。下一步要做的工作是更多核的片上系统设计和操作系统移植。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1] Wayne Wolf.FPGA-Based System Design[M].北京:中国机械出版社,2004:5-13.

[2] Takeshi Kodaka,Keiji Kimura,Hironori Kasahara.Multigrain Parallel Processing for JPEG Encoding on a Single Chip Multiprocessor[C]//International workshop on Innovative Architecture for Future Generation High-Performance,2002:57-63.

[3] Hristo Nikolov,Todor Stefanov,Ed deprettere.Efficient External Memory interface for Multiprocessor Platforms Realized on FPGA Chips[C]//Field Programmable Logic and Applications International Conference,Amsterdam,2007:580-584.

[4] Jerraya A,A Franza,O Levy.Envisioning the Future for Multiprocessor SoC[J].Design &Test of Computers,2007,24(2):174-183.

[5] Ravindran N,Satish Y.Jin K.An FPGA-based Soft Multiprocessor System for IPv4Packet Forwarding[C]//International Conference on Field Programmable Logic and Applications(FPL),2005.8:487-492.

[6] Chris Rowen,Tensilica Inc.Fundamental Change in MPSoCs:A fifteen year outlook.MPSOC'03Workshop Proceedings[C]//International Seminar on Application-Specific Multi-Processor SoC,2003:45-46.

[7] Paulin PG,Pilkington C,Langevin M.Parallel programming models for a multiprocessor SoC platform applied to networking and multimedia[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2006,14(7):667-680.

[8] Ravindran K,Satish N,Yujia Jin.An FPGA-based soft multiprocessor system for IPv4packet forwarding[C]//Field Programmable Logic and Applications,New York,2005.487-492.

[9] 赵锋,马迪铭,孙炜,等.FPGA上的嵌入式系统设计实例[M].西安:西安电子科技大学出版社,2008.

[10] 陈渝,韩超,康烁,等.嵌入式系统实践教程[M].北京:机械工业出版社,2008:49-71.