一种基于0.5μm CMOS工艺圆片级可靠性评估方法*

涂启志,马敏辉,赵文清

(1.无锡市广播电视大学,江苏 无锡,214000;2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 概述

半导体器件从分立走向集成,从SSI发展到ULSI。现在已可以将近1亿个器件集成在一个芯片上,失效率将降低至10FIT数量级[1]。在这种低失效率的情况下,已无法通过传统的可靠性试验方法确定失效率的具体数值,当然更不可能定量确定失效率与有关工艺参数的相互关系。这时考虑工艺可靠性就不应从失效率出发,而应根据失效机理,确定影响可靠性的关键工序和关键工艺参数。

快速圆片级工艺可靠性(WLR)评估正是基于这样的基本思路[2~4],其核心包括两方面的工作。一方面是将表示IC可靠性的失效率要求转化为对工艺参数和工艺条件的控制要求,并通过调整设备、工艺优化设计,使这些要求得到满足。另一方面是在平时常规生产中,通过工艺参数监测和实施统计过程控制技术,使工艺过程始终处于统计受控状态,保证生产的电路一直满足可靠性要求。在0.5 μm工艺开发过程中,我们在PCM中设计了多种用于考核工艺和器件可靠性的测试结构,用来测试金属、孔、W-Plug通孔的电迁移、器件热载流子以及工艺等离子损伤引起电荷等可靠性方面的参数,同时分别给出了相应的工艺和物理机理、测试结构和方法以及测试结果。

快速WLR测试为半导体厂产出的大批量样品能够方便进行测试提供了巨大的便利。这些测试结构设计在划片槽中,这样的安排使快速测试能够反映整个圆片的可靠性变化以及片间和批间的变化。使用日常的WLR测试技术可以量化和检查这些变化的来源。

2 电迁移测试

2.1 电迁移产生原因

电迁移是Al的自扩散,主要原因是Al条中电子运动的动力迁移。虽然电子电势不足以使Al原子离开其晶格位置,但增加了原子获得足够的热能移动到相邻空位的几率。轻微电子电流的动力传输增加了原子朝相同方向跳越的可能性,持续的电流同样降低了原子朝相反方向跳越的可能,这样持续同方向的电流导致了绝对物质的流动[5]。

铝金属通常是以一系列紧密排列的单晶晶粒存在。虽然电迁移沿晶粒边界快速发生,但同时也穿通晶粒内部。试验表明,在到达材料的1/2~2/3绝对熔点温度前,体内或格点扩散率都很低,并且依赖于条宽和晶粒的比率。

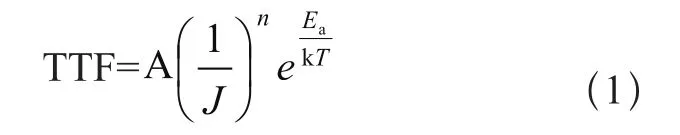

对给定的任何材料,电迁移率和电流密度以及膜层温度成正比。依赖关系通过Black方程[6]表示:

其中:TTF是失效时间,A是材料依赖常数,J是电流密度A/cm2,通常为106A/cm2;n是电流密度因子,通常为2;Ea是热激活能,为0.473 eV;k是Boltzmann常数,为8.62×10-5eV/K;T是绝对温度,为(85+273)K。

公式反映固定电流密度应力条件下金属条金属电迁移率相关情况,但金属条失效时间也受应力梯度的影响,热梯度和机械应力都能优先引起铝中自扩散。我们知道没有电应力下这些应力梯度也能引起金属条失效,梯度的存在以及梯度扩散方向和驱动电迁移的电流方向是否一致,能使早期金属电迁移率加速或降低。

2.2 测试结构设计

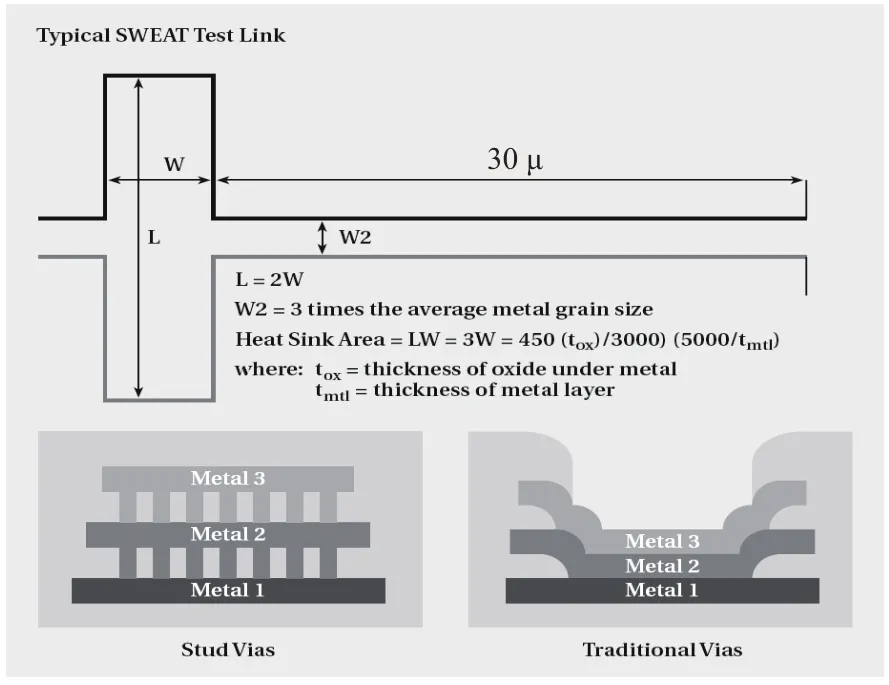

图1显示电迁移标准圆片级电加速测试(SWEAT)结构[7]。结构是一系列宽和窄的线条段,这些线条可以允许大电流密度测试,同时保持温度低于发生体内和边界迁移的临界跃迁温度,宽条作为热收集器为窄条降温。图中也显示这些结构的设计规则,通常测试链中大于7个这样的结构,显示值都为经验值。图1显示对三层金属工艺中选择两种不同热收集器的纵向剖面图,对任何一层金属,热收集器和M1相连,这非常重要,因为金属热导大约是二氧化硅的50倍,这样设计给了热收集器一个热阻,使每层金属基本相同。

图1 SWEAT 结构细节描述

使用热收集器比单一的直条可以允许金属条通过大的电流密度而不发生异常的失效,这样测试时间可以降低,对多层金属工艺而言非常重要。如果M3下的氧化层是M1下氧化层厚度的3倍,那么M3的热阻将是M1的3倍,结果是若要M1、M3金属条的温度相同,流过M3的电流密度将是M1电流密度的1/3。如果这个工艺电流密度指数是2,那么M3的测试时间将延长9倍。

采用相似的测试结构同样可以测试孔和W-Plug通孔的失效时间和寿命估计。

2.3 测试结果分析

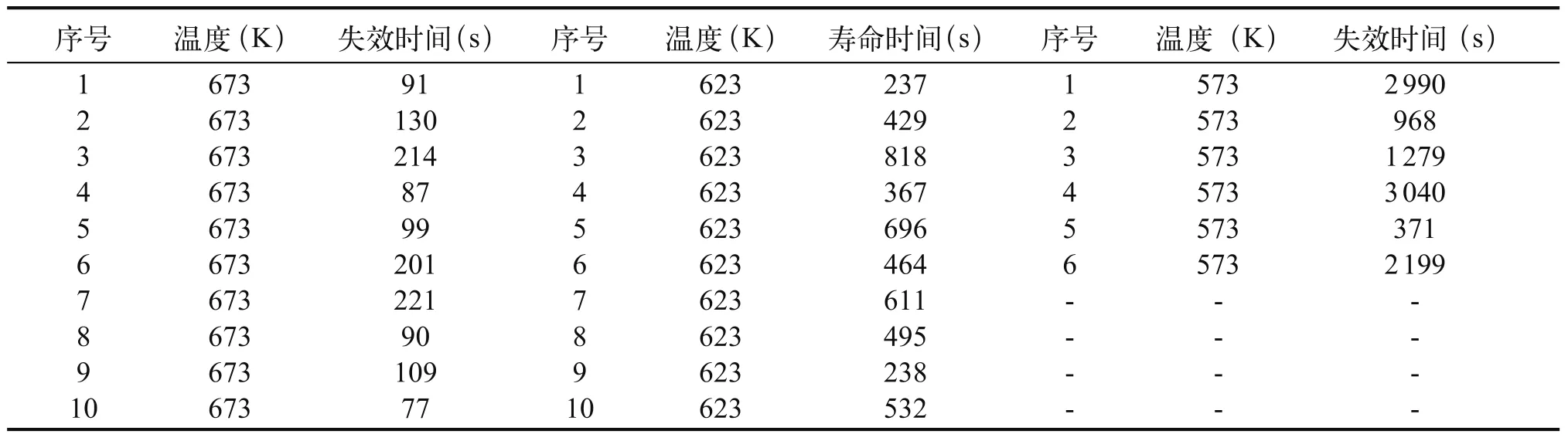

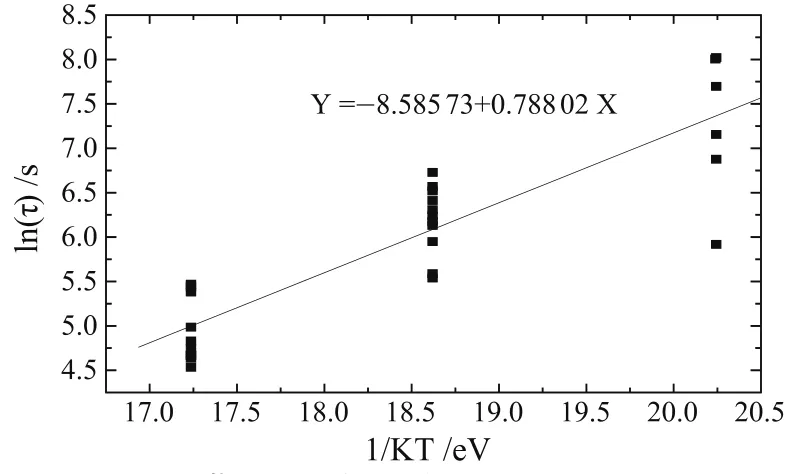

根据式(1),测试过程中同时考虑温度加速度和电流加速度,得到在不同温度下的电迁移失效时间(如表1)及其相应的金属电迁移寿命和温度对应曲线(如图2)。

由图2的寿命拟合曲线,很容易就能够估算出金属在一定电流密度下不同温度的电迁移寿命时间。

表2列出了在673 K时,测试的温度加速度、电流加速度、总加速度和失效时间,以及推算出的电迁移寿命值。可以看出,在单一电迁移失效机理下,金属寿命可以达到近三十年以上。

表1 CMOS工艺金属1在不同温度下的电迁移失效值

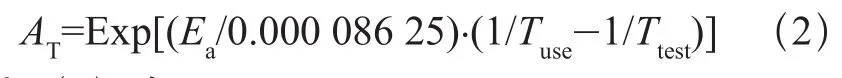

温度加速度:

式(2)中:

AT—温度加速度;

Tuse—使用条件下的温度值,K;

Ttest—实验条件下的温度值,K。

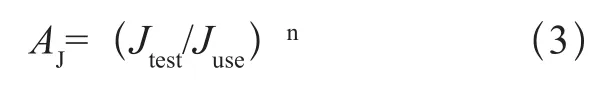

电流加速度:

式(3)中:

AJ—电流加速度;

Juse—使用条件下的电流密度,A/cm2;

Ttest—加速应力条件下的电流密度,A/cm2。

图2 CMOS工艺金属1电迁移失效与温度的关系曲线

表2 673 K时CMOS工艺金属1电迁移寿命时间

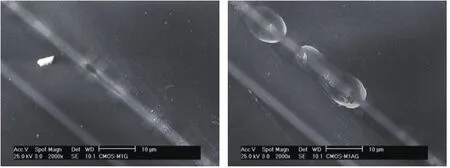

图3给出了测试金属电迁移失效后的照片,图中发亮部分表现为金属条中出现空洞。

图3 亚微米CMOS工艺金属1的电迁移失效图形

3 热载流子测试

3.1 热载流子产生机理

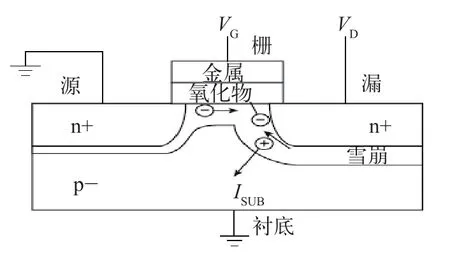

0.5 μm CMOS工艺中,器件在水平和垂直方向上的参数(例如:沟道长度L、宽度W、栅氧厚度Tox、源漏结深Xj等)都按一定规律等比例缩小,薄栅氧以及较短的沟道长度都会使沟道区纵向电场和横向电场增大,使得沟道区载流子在从源向漏移动的过程中获得足够的动能,这些高能(热)载流子能克服Si-SiO2界面势垒进入氧化层,造成Si-SiO2界面损伤或产生氧化物陷阱(如图4所示),使MOSFET的阈值电压Vth、线性区跨导gm等参数发生漂移或退化,影响器件的可靠性,并最终引起电路失效,此即为热载流子效应[8~9]。

热载流子效应造成的器件性能退化主要由器件寿命τ来表征,器件的寿命值是以阈值电压Vth、跨导gm等的变化量达到某一标准(例如:ΔVth=10 mV,Δgm/gm=10%)为失效判据。由于要达到这一失效标准仍然需要较长时间,所以通常是在器件上作用一段时间的应力,测出若干个应力时间的参数漂移点,再用外推的方法算出器件在应力作用下的寿命值,以此为根据进行参数提取,得到正常工作条件下的寿命值[10]。

图4 NMOS器件中热载流子效应示意图

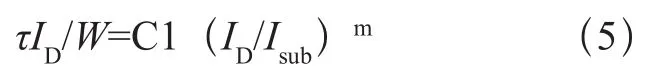

对NMOSFET器件而言,推算寿命的加速模型有三种:衬底/漏极电流比率模型、基极电流模型和漏极电压加速模型[11~12],本章采用衬底/漏极电流比率模型,模型方程如下:

式中,τ是热载流子退化寿命,H是比例常数,m、n是模型参数,ID是漏极电流,Isub是衬底电流,ΔD指的是参数退化量,W是沟道宽度。

按照模型要求,我们设计了不同尺寸的NMOS管(图4),并使用阈值电压Vth漂移10 mV作为失效判据,对工艺线的热载流子注入效应进行评价。

对衬底/漏极电流比率模型公式整理可得:

C1=ΔDnH,采用跨导gm漂移量作为失效判据,ΔD为规定的跨导gm的变化量,H取决于工艺的系数,模型参数m=φit/φt[11]。

φit为电子在产生界面陷阱中所必须具备的临界能量,φt为碰撞离化能,m可以通过τID与ID/Isub的对数曲线中得出。

模型参数n由阈值电压随时间变化的对数坐标中得出。得到模型参数m、n之后,只需测量器件的寿命τ、衬底电流Isub以及漏极电流ID,利用式(5)可以定出针对该种器件的介质工艺的系数H;所以,对于工艺线上产品,只要监测到Isub和ID,就能估计相关器件的寿命,并对该器件的热载流子衰退效应进行评价。

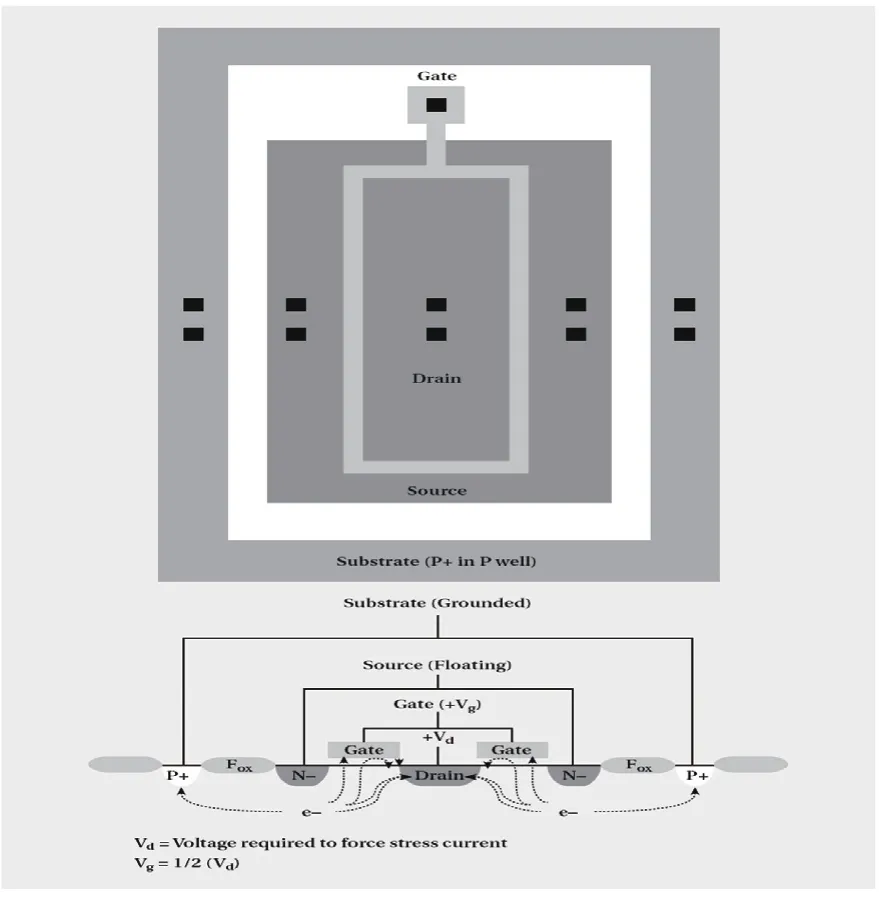

3.2 热载流子测试结构

图5显示了热载流子器件测试结构,漏被栅包围的N管。这是没有场氧边界的测试器件,结构四周被衬底接触包围,漏接触在漏的中心,漏设计较宽是减小在漏边角处的注入电流。采用栅包围结构是因为测试需要在漏端加雪崩击穿电压,产生大量热电子来进行,雪崩击穿电压必须作用在漏靠近栅边界,如果用常用器件结构进行测试,由于电场注入效应,雪崩击穿电压通常发生在有源区和场氧的边界,场注会在场边界点产生一个陡峭的结,降低了此点的击穿电压。

图5 热载流子测试

3.3 热载流子测试结果

由于应力试验通常是以阈值电压Vth、跨导gm等的变化量达到某一标准(例如:ΔVth=10 mV,Δgm/gm=10%)为失效判据,所以在应力实验之前首先要得到器件的Vth、gm、BVdss(击穿电压)等参数的原始值。然后通过测试得到使Isub达到最大值的栅压和漏压。

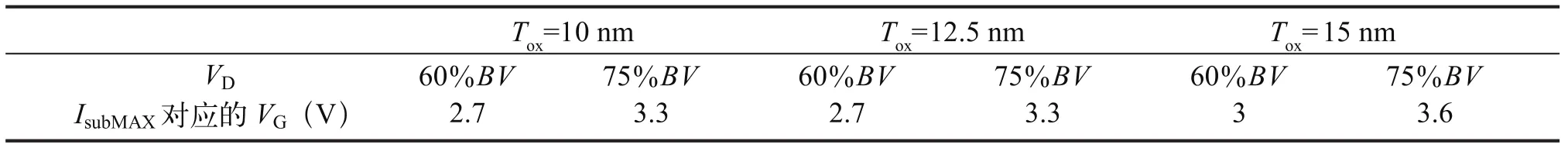

众所周知,Isub和Ig(栅电流)是监控热载流子注入效应的重要电学参数。其中主要由Isub反映NMOS管的热载流子注入效应,而反映PMOS管的热载流子注入效应的是Ig。而在加速应力实验中器件栅端以及漏端所施加的应力通常是IsubMAX(最大衬底电流)或IgMAX(最大栅电流)所对应的VG(栅压)和VD(漏压);而VD的选取与该器件的击穿电压BVdss有关,通常选取击穿电压的60%~90%作为漏端的电应力值。

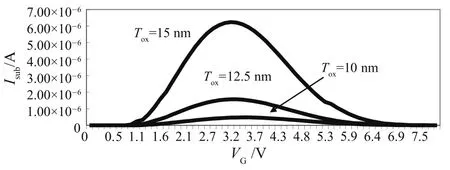

对于宽长比W/L=20/0.55,栅氧厚度为15 nm、10 nm、12.5 nm的一组NMOS管,Isub与VG、VD的关系曲线如图6所示,对应VD=75%BVdss。

从图6可知,在NMOS管的宽长比相同的情况下,栅氧越薄,IsubMAX越大;但是当VD一定时,这些NMOS管的IsubMAX对应的VG几乎是相同的,如表3所示。

表3 不同栅氧厚度NMOS管之IsubMAX所对应的VG和VD

图6 VD=75%BVdss时不同栅氧厚度N管的Isub-VG曲线

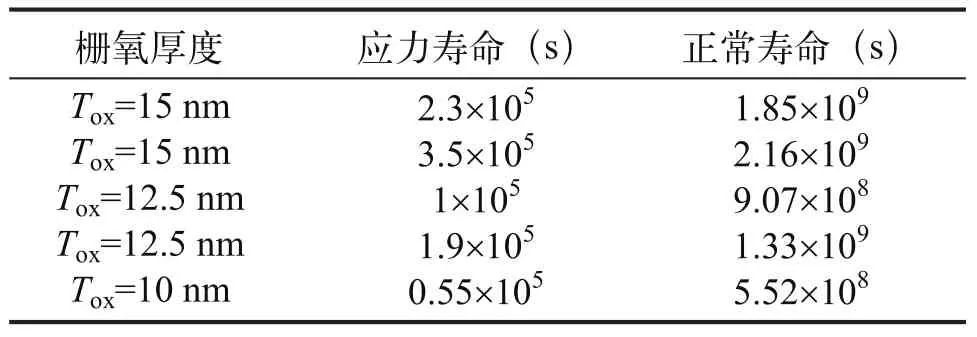

表4中列出的是部分器件的应力寿命值和正常工作条件下器件的正常寿命值,W/L=20/0.55、Tox=15 nm、12.5 nm、10 nm。就热载流子衰退效应这单一失效机理而言,大部分器件的使用寿命可以长达数十年,这说明热载流子效应对该类型器件影响甚微,利用与之相关的工艺生产的产品抗热载流子的能力比较强。

表4 NMOS应力寿命和正常寿命

4 结论

为了考核0.5 μm工艺开发完成后的可靠性情况,本文提出了对0.5 μm CMOS工艺进行圆片级可靠性(WLR)评估,为提高工艺、电路可靠性和及时在线控制开拓了新思路,给出了相关的失效机理和测试结构,并完成了金属电迁移测试、器件热载流子测试等。测试得出单一电迁移失效、热载流子失效寿命可以达到1×109数量级(几十年),初步实现了工艺可靠性的在线监控。

[1]James D Plummer,Michael D Deal,Peter B Griffin.Silicon VLSI Technology Fundamentals [M].北京:电子工业出版社,2003.

[2]施敏.半导体器件物理与工艺[M].苏州:苏州大学出版社,2004.

[3]陈星弼,张庆中.晶体管原理与设计[M].成都:电子科技大学出版社,2004.256-258.

[4]Campbell S A.微电子制造科学原理与工程技术[M].北京:电子工业出版社,2003.

[5]Marbell M N,Cherepko S V,Madiar A,et al.An improved large signal model for harmonic-balance simulation of Si LDMOSFETs [A].34th Europ Microw Conf [C].Amsterdam,The Netherlands.2004.225-228.

[6]Tang C W,Tong K Y.A compact large signal model of LDMOS [J].Sol Sta Electron,2002,46(12):2111-2115.

[7]Aarts A C T,Kloosterman W J.Compact modeling of high voltage LDMOS devices including quasi-saturation [J].IEEE Trans Elec Dev,2006,53(4): 897-902.

[8]SU J,FANG J,WU J,et al.Characterization and modeling of a 700 V single crystal diffused LDMOS device [J].Microelectronics,2004,34(2): 192-194.

[9]Yang Y,Woo Y Y,Yi J,et al.A new empirical large singnal model of Si-LDMOSFETs for high power amplifier design[J].IEEE Trans Microwave Theory and Techniques,2001,49(9): 1626-1633.

[10]Wu X L,Chen J N,Ke D M,et al.A circuit micro model of high voltage LDMOS based on numerical simulation[A].IEEE Int Workshop VLSI Design & Video Tech [C].Suzhou,China.2005.90-93.

[11]HE j,ZHANG X.Analytical model of surface field distribution and breakdown voltage for RESURF LDMOS transistors [J].Chinese J Semicond,2001,22(9):1102-1106.

[12]Ameen M,Hebb J.Implanter,RTP system issues for ultrashallow junction formation [J].Sol Sta Technol,2001,44(77): 77-84.