基于异构多核处理器的嵌入式数控系统研究

陆小虎 于 东 胡 毅 林立明

1.中国科学院大学,北京,100049 2.中国科学院沈阳计算技术研究所高档数控国家工程研究中心,沈阳,110168

0 引言

嵌入式系统具有成本低、体积小、集成度高、可靠性高等特点,目前已经在数控领域获得一定的应用。目前嵌入式数控系统主要基于ARM(advanced RISC machines)+DSP(digital signal processor)和 ARM+DSP+FPGA(field programmable gate array)两种硬件结构[1-2]。基于分立元件的嵌入式数控系统集成度不高,稳定性不好。不同架构处理器之间的通信方式复杂,ARM处理器和DSP处理器之间的通信带宽小导致了系统的通信延时增加[3]。在软件结构上,传统的嵌入式数控系统没有操作系统,任务之间切换开销大,系统的可扩展性差,不能提供友好的人机接口,不同处理器之间的协同工作比较困难,数控系统效率不高[2]。

异构多核技术最大的特点就是在一个芯片内集成多个异构的处理器核[3-4],不同核心之间使用处理器内部的高速总线相连,核心之间的通信延迟可以忽略。文献[5]在以多核处理器为核心的应用系统中,提出一种基于异构多核处理器系统在高性能并发处理应用中的三层软件架构,为并发处理应用加速。文献[6]提出一种主从单边卸载模型,以及编译框架模型,为异构多核处理器在专门计算领域的应用提供理论基础。

在嵌入式计算领域中,异构多核处理器能够比同构多核处理器发挥出更优的性能。基于异构多核处理器的嵌入式数控系统具有很高的集成度和稳定性,由不同体系结构的处理器核心负责数控系统工作负载中的不同类型任务的运行机制,能有效地提高数控系统的性能[4,7]。

针对传统基于模拟接口的伺服系统中存在的分辨率低、系统柔性弱、通信带宽小、难以分布式控制等问题,近年来数控系统与数字伺服驱动器之间采用现场总线连接。现场总线采用全数字通信,支持数据双向传输,线缆大大简化,从根本上突破了传统点对点式的模拟信号或数/模信号控制的局限性,同时具有传输速率高、传输距离远、抗干扰能力强等优点,具有较强的实时性和可靠性[5-6,8],结合现场总线的嵌入式数控系统,能够满足高速高精数控系统的需求。

数控系统在要求具备较高加工精度和复杂曲线计算能力的同时,还要求给用户提供人性化的操作界面。传统嵌入式数控由于没有操作系统的支持,人机交互功能弱,多任务的处理能力差,不能满足数控系统高精度控制的要求。为满足高性能嵌入式数控系统的要求,本文基于异构嵌入式处理器平台提出一种嵌入式数控系统体系结构。

1 基于异构处理器的数控系统关键技术

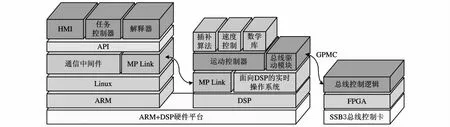

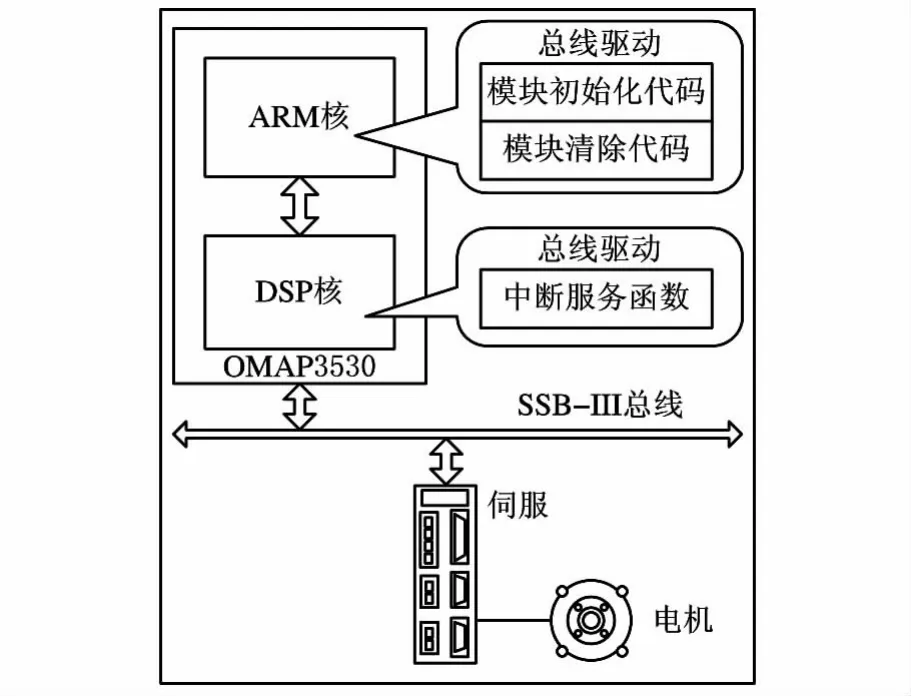

本文提出的嵌入式数控系统体系结构如图1所示。

图1 系统结构

该嵌入式数控系统结构中,在异构双核处理器的不同核心上运行不同操作系统,分别管理不同的处理器核心,充分发挥不同体系结构处理器核心的性能;使用静态划分的方法,将数控任务分配到不同处理器核心上,提高嵌入式数控系统的稳定性和实时性;使用基于共享内存机制实现不同核心上任务的协同工作,避免不同的处理器结构的差异带来的潜在的内存访问冲突;使用现场总线连接嵌入式数控系统与伺服驱动实现一种基于异构多核处理器的嵌入式数控系统。

1.1 异构的多操作系统平台

目前异构处理器都采用主从式架构,即采用一个主核和一个专用处理核作为加速核,其中主核通常采用成熟的标量处理器核心,专用处理核则面向特定类型工作负载进行定制,使用面向特定的负载而设计特殊的指令集[4]。不同的处理器核心具有自己的处理器架构、自身的内存空间和外设,不同处理器核心的运行频率不同,单一的操作系统不能同时发挥所有处理器核心最佳性能[6]。

在数控系统中,实时任务要求系统延迟尽量小,Linux的高度抽象机制难以满足高实时的算法要求。

在异构处理器中,ARM核心在用户接口控制方面具有很高的效率,DSP核心功能强大,能够进行大量数据计算。Linux通过应用软件模块与硬件资源隔离机制为用户提供了高度的资源抽象,系统稳健性强,基于ARM处理器核心的Linux+ARM子系统提供友好的用户界面。DSP/BIOS提供了直接存取硬件中断的机制,可以实现底层硬件所支持的最短延迟响应,对运动控制、位置控制等强实时性的任务,这种精细粒度的硬件中断控制机制可以提供很好的实时性[9],基于DSP核心的DSP+DSP/BIOS子系统提供高精度多轴伺服控制。

1.2 异构系统中任务的分配策略

在基于异构多核处理器的数控系统内部,处理器架构的差异和操作系统的差异导致任务在不同的核心上运行时间不相同,任务在不同的处理器核心之间迁移的开销巨大[10]。异构多核架构中,提高处理系统性能的关键就是合理的任务分配,任务分配的目标就是找出一个任务组合,使得这些任务能够满足实时性要求的同时,整个系统执行效率达到最优[11]。

异构多处理机系统的任务分配被证明是一个NP完全问题,而异构多核处理器能等效为一个片上的多处理机系统,异构多核处理器的任务最优化分配同样是一个NP完全问题。在嵌入式系统中进行任务分配时主要考虑的因素有:任务的执行时间、任务的执行频率、优先级、通信、系统资源等[7,12]。

本文在多机系统中任务的分配方法[11]基础上,提出异构多核嵌入式数控系统中的任务分配策略:①给同一个处理器核心分配相互通信频繁的任务;②给同一个处理器核心分配最适合该处理器的任务;③给同一个处理器核心分配最少的任务;④均衡各个处理器核心的负载;⑤将任务静态分配成多个子集,每一个子集对应到不同的处理器核心上。

1.3 数控系统中任务的划分

数控系统是一个多任务和高实时并存的系统,在数控系统内部,任务主要分为实时任务和非实时任务。数控系统内部任务有用户界面(HMI)、软PLC、G代码解释、粗插补、精插补、任务控制器、手轮控制、速度规划、运动控制等。显示任务与图形环境密切相关,图形环境是Linux系统的一部分,因此将和图形显示相关的任务安排到Linux系统下运行。数控系统通过软PLC实现对IO的控制,IO控制任务对实时性的要求不高,不与运动控制等任务进行交互,软PLC既可以安排在实时系统中运行,也可以安排在非实时系统中运行。在数控加工过程中,由G代码解析、插补算法、速度规划、运动控制等任务构成一个加工过程。其中G代码解释任务既可以运行在实时系统中也可以运行在非实时系统中,G代码解释需要用到大量的分支判断等操作。数控系统的运动控制任务、插补任务、速度规划任务在获得G解释器的数据之后,通过实时性周期地运行实现数控加工过程的精度控制,这些任务中包含大量的数学运算,属于计时密集型任务。数控系统中的手轮任务需要系统能够对手轮的操作进行实时响应。

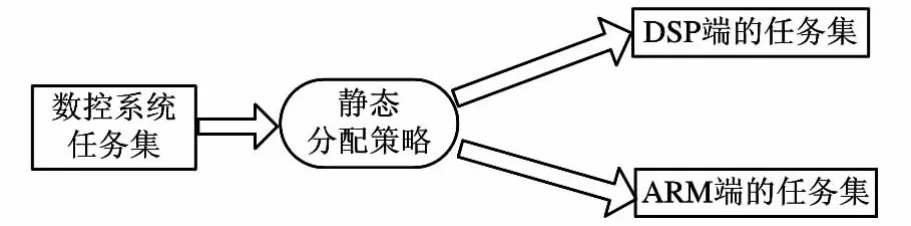

结合不同任务对实时性的要求和本文提出的任务分配策略,对数控系统内部任务进行分解,降低不同处理器核心的耦合度,从而将整个系统划分成两个以处理器核心为单位的并行子系统,如图2所示。在数控系统内部的任务中,G代码解释任务、运动控制任务、插补任务、轨迹规划任务之间需要进行大量的数据交互,但是G代码解释任务与其他任务之间的交互较少。将计算密集而且实时性要求较高,同时数据交互量大的运动控制任务、插补任务、轨迹规划任务作为一组实时的周期任务分配到DSP核心上执行;将具有实时性要求,但不是周期任务的手轮控制任务安排在DSP核心上作为一个高优先级中断任务执行;将与Linux系统关系紧密的图形显示任务分配到ARM核心下运行,用户界面运行在ARM Linux子系统下[13];将软PLC安排在ARM核心上执行;为实现平衡处理器核心的负载,将G代码解释任务安排在ARM端执行,并且通过核心之间的共享内存实现与实时任务的通信(图1)。

图2 静态任务分配图

1.4 处理器核心间的协同方法

嵌入式操作系统的引导过程与系统的硬件结构相关,本文使用主从方法加载操作系统,并提出一种基于共享内存的核心间的协同工作机制。

1.4.1 操作系统加载方式与运行方式

目前的主从架构的嵌入式结构中,通用的处理器负责所有资源的管理和操作,专用的处理器负责计算加速[6]。本文在异构双核处理器的核心上运行不同操作系统,通过串行的启动方式来启动两个核心上的操作系统。首先在ARM处理器端启动Linux系统,然后通过Linux系统向DSP加载操作DSP/BIOS操作系统。通过运行在DSP核心的实时系统,让实时任务常驻DSP核心上,实现数控系统内部任务的并行执行。

1.4.2 核心间的通信方法

基于异构双核处理器的数控系统中同时存在两种不同的操作系统(ARM Linux子系统和DSP+DSP/BIOS子系统)和三种任务间的通信模式(ARM核心内部的任务通信,DSP核心内部的任务通信,ARM与DSP核心间的通信),其中,前两种通信模式属于操作系统内部的通信,由操作系统维护,ARM与DSP核心间的任务通信可以通过处理器间的共享物理内存实现。在数控系统中,实时任务运行在DSP核心上,非实时任务运行在ARM处理器核心上,两种不同的任务之间通过共享物理内存的方式进行通信。在共享内存上,定义了能够被两个处理器核心访问的共享数据结构,用于两个处理器之间信息的通信。

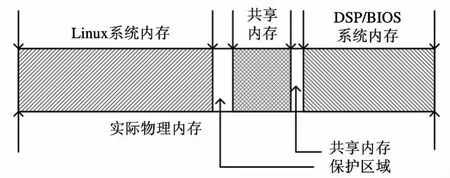

在硬件上,将物理内存划分为五个区域,包括Linux的系统内存、用于两个核心之间通信的共享内存、DSP/BIOS的系统内存和两块保护内存区域(图3)。实时任务与非实时任务进行通信的共享数据结构保存在ARM处理器核心和DSP核心之间专属的共享内存区域。这片内存区域由DSP/BIOS进行初始化,并且创建共享数据结构。共享数据结构创建成功之后,DSP/BIOS将共享内存的实际物理地址通过处理器核心间的消息总线传递到运行在ARM端的Linux系统中,Linux系统在获得共享内存的信息之后,按照地址转换协议,将该共享内存的地址信息转换成Linux可以直接访问的地址,并且将共享内存的地址指向该内存区域。

图3 内存分配图

共享内存中的数据结构采用互斥锁的机制,在不同的操作系统中通过唯一的ID对该内存进行标识。当处理器核心的任务需要对共享数据结构进行读写操作时,首先需要获得互斥锁,然后对共享内存中的数据结构进行读写操作;当任务完成对共享内存数据结构的读写操作之后,释放互斥锁,并通知正在等待访问共享内存的任务。这种互斥共享数据结构实现了不同处理核心上的各个任务之间对共享内存数据互斥的访问,同时可以保证DSP核心和ARM核心间共享数据的同步。

1.5 嵌入式数控系统与运动控制总线的集成

通过将总线技术与嵌入式技术结合,实现高速的控制,通信专用芯片采用现场可编程逻辑门阵列(FPGA),实现SSB-III总线的链路层功能,整个链路层可以划分为三个逻辑部分:物理层接口、链路层逻辑功能和用户层接口[8]。通过将与电机控制相关的伺服单元直接与DSP核心相连,实现DSP对伺服电机的控制。总线的驱动分布在不同的核心之上,可以获得较高的实时性,如图4所示。首先由ARM核心完成总线的初始化工作,然后将运动总线的控制权限交给DSP+DSP/BIOS实时子系统,由于DSP+DSP/BIOS子系统的实时性好,所以可以实现高精度的控制。

图4 总线驱动模型

2 实验验证

2.1 性能分析

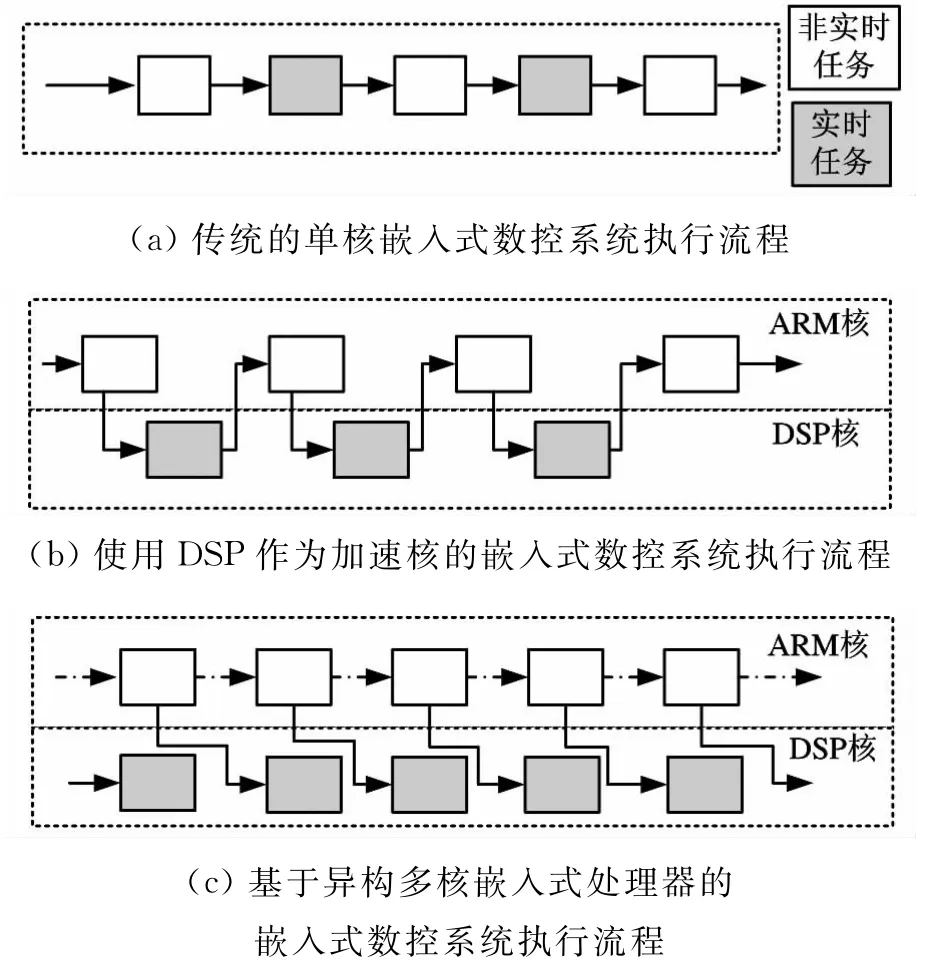

在传统的单核的嵌入式数控系统中,数控系统内部的实时任务和非实时任务是串行的,如图5a所示。使用ARM+DSP结构的嵌入式数控系统中,由于DSP处理器仅仅起到的是加速作用,因此数控系统内部的实时任务和非实时任务之间也是串行执行的,如图5b所示。本文实现的基于异构处理器的嵌入式数控系统中,通过运行在不同的处理器核心上的操作系统对该处理器核心上的任务进行调度,真正实现数控系统内实时与非实时任务的并行执行,如图5c所示。记T为数控系统一个任务周期的执行时间,tn为一个控制周期内的非实时任务的执行时间,tr为一个控制周期内的实时任务的执行时间,则传统单核处理器嵌入式数控系统的一个控制周期的执行时间为

图5 任务的执行流对比图

记tt为不同处理器之间的通信时间,t′r为一个控制周期内实时任务在DSP上的执行时间。则

式(2)表示的是传统的ARM+DSP的一个控制周期的执行时间。则本文实现的嵌入式数控系统的一个控制周期的执行时间为

2.2 实验验证过程

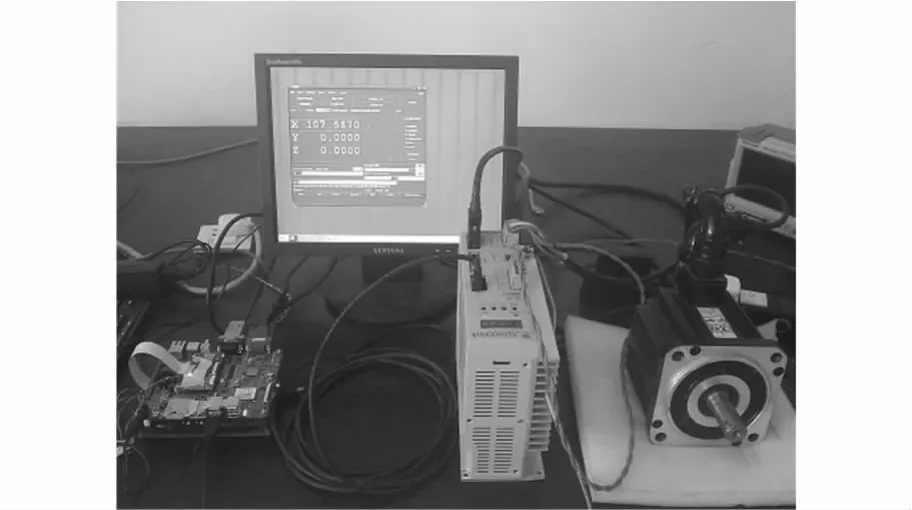

本文开发了一个基于OMAP3530的嵌入式数控系统,OMAP3530是一款异构处理器,同时具备ARM核心和DSP核心,该处理器充分利用控制性能优异的ARM体系结构和计算机功能强大的DSP体系结构。使用FPGA技术实现了嵌入式数控系统与运动控制总线的集成。本文在完成的数控系统和现场总线驱动板卡上一共连接了三套伺服驱动系统,系统的拓扑结构如图6所示。

图6 实验环境

2.3 实时性评估

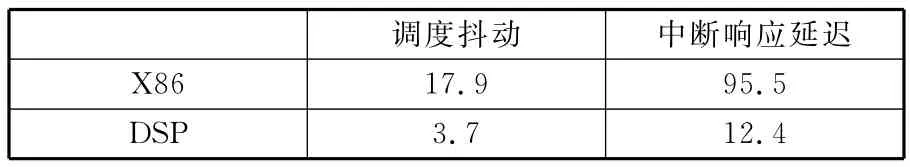

为了验证本文实现的数控系统的实时性,本文选择中断响应延迟和任务的周期抖动作为评价指标,对数控系统进行测试。本文开发的数控系统和基于X86的数控系统对比结果如表1所示,表中记录的是在一个完整的加工过程中的最大调度抖动和最大中断响应延迟。由实验的结果可知,由于DSP的体系结构简单,DSP/BIOS具有精简实时性高、可以直接访问硬件等特点,运行在DSP上的运动控制任务调度抖动比较小,DSP对中断的响应时间要比X86平台短,更适合实时控制。

表1 X86与DSP的实时性对比 μs

2.4 线场总线性能评估

数控系统的高速高精运动控制对总线的要求主要体现在以下几方面[13]:①实时循环周期一般在1~10ms之间;②总线传输的确定性;③执行命令与反馈的同步性;④支持I/O设备信号的传递;⑤支持非周期的数据。针对上述要求,本文在基于OMAP3530处理器和FPGA的嵌入式数控系统上,对影响总线传输实时性的中断响应延迟和影响总线传输确定性的中断抖动两个性能参数开展了相关实验测试工作。

本文采用OMAP3530处理器自身的定时器来测量中断延迟。记gt_rate为定时器的频率,则有

其中,式(4)表示定时器的初始值为start_tick,从start_tick开始经过n秒后定时器将产生一个溢出中断,此时定时器会自动重载start_tick,然后继续计时。系统响应该中断后进入相应中断服务函数,此时调用针对OMAP平台的内核系统函数,用式(6)获得定时器当前的数值end_tick,代入式(5)即可获得中断响应延迟intr_delay。

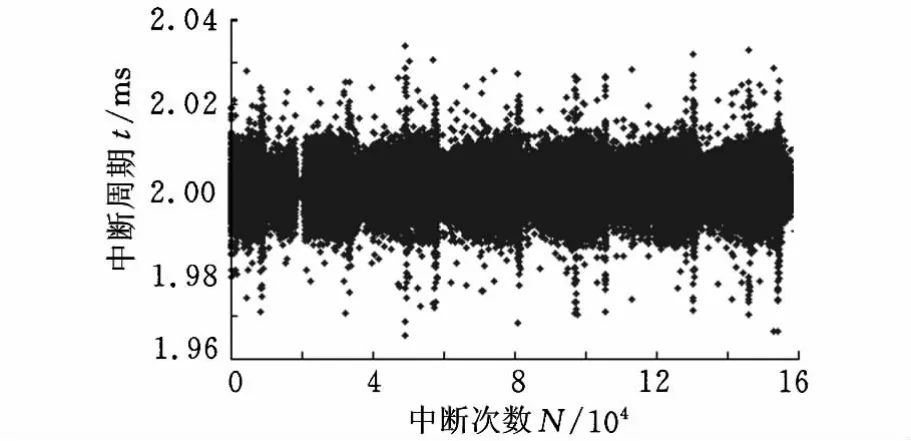

本文选取2ms作为SSB-Ⅲ现场总线通信周期,实验测得的总线中断周期数据如图7所示,最大偏差(实际周期与理论周期2ms的最大偏离值)为34.615μs,可见基于OMAP3530处理器和FPGA的SSB-Ⅲ总线周期具有很好的确定性。

图7 现场总线中断周期

2.5 执行的效率和对比

本文通过对数控加工中电机的控制过程的仿真,对运行在嵌入式实时系统上的数控系统中的插补任务执行时间进行了测试。

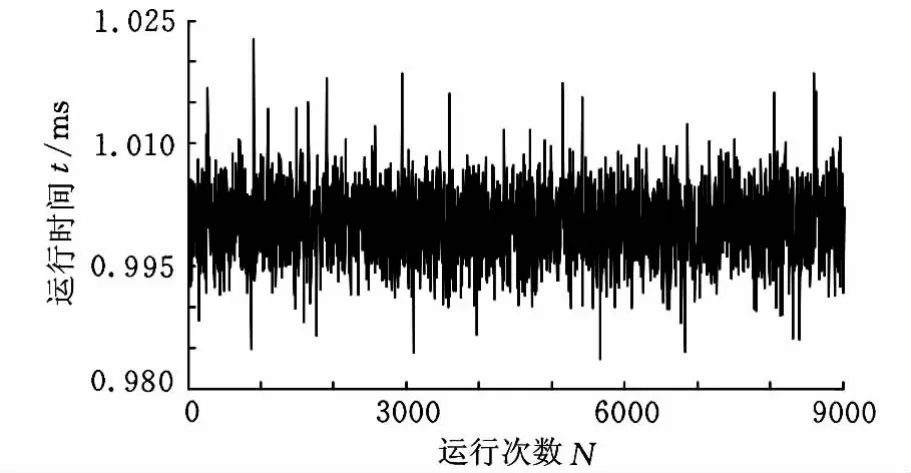

如图8所示,该加工过程中,总共有1356段命令线段,在数控软件的参数里将运行周期设置为1ms,实际任务周期范围介于1.03~0.973ms之间,可以满足实时控制和加工的要求。

图8 数控系统任务周期

3 结语

本文提出了一种基于异构双核处理器和现场总线的嵌入式数控系统的设计与实现方法,该方法通过在异构双核处理器的核心上同时运行两个操作系统,结合静态划分的方法对数控系统任务进行划分,实现嵌入式的数控系统,结合现场总线技术使数控系统具有良好的可扩展性。通过将基于异构多核处理器的嵌入式数控系统的中断响应延迟和中断抖动两个实时性能指标和基于PC的数控系统进行对比,以及对现场总线的性能测试和数控加工过程主要任务执行时间的测试,证明了本文提出的基于异构多核处理器的嵌入式数控系统具有良好的实时性,能够满足数控加工的需求,可以为高性能嵌入式数控系统的体系结构提供参考。

[1]徐跃,王太勇,赵艳菊,等.基于ARM和DSP的可重构数控系统[J].吉林大学学报(工学版),2008,38(4):848-851.Xu Yue,Wang Taiyong,Zhao Yanju,et al.Reconfigurable CNC System Based on ARM and DSP[J].Journal of Jilin University(Engineering and Technology Edition),2008,38(4):848-851.

[2]孙程建.基于Linux的嵌入式数控系统底层软件设计[D].武汉:武汉科技大学,2007.

[3]李爱朝,林桂清,陈小亮.采用ARM和DSP的数控系统硬件设计及驱动开发[J].现代制造工程,2010(5):27-29.Li Aichao,Lin Guiqing,Chen Xiaoliang.Design of NC System Hardware Based on ARM&DSP and Driver Development[J].Modern Manufacturing Engineering,2010(5):27-29.

[4]李春江,杨学军.主从式单边异构多核处理器编程模型和编译架构[J].计算机工程与科学,2009,31(8):66-68.Li Chunjiang,Yang Xuejun.The Programming Model and Compilation Framework for Master-Slave One-sided Heterogeneous Multi-core Processors[J].Computer Engineering & Science,2009,31(8):66-68.

[5]汪少敏,赵猛,朱振博,等.基于多核处理器并发计算软件构架设计与实现[J].计算机科学,2008,35(7):283-285.Wang Shaomin,Zhao Meng,Zhu Zhenbo,et al.Multi core Processor Based Software Framework Design and Implementation for Concurrent Computation[J].Computer Science,2008,35(7):283-285.

[6]胡毅,于东,李培楠,等.基于现场总线的开放式数控系统的设计与实现[J].小型微型计算机系统,2008,29(9):1745-1749.Hu Yi,Yu Dong,Li Peinan.Design and Implementation of Open CNC System Based on Fieldbus[J].Journal of Chinese Computer Systems,2008,29(9):1745-1749.

[7]王志成,于东,张晓辉,等.数控系统现场总线可靠通信机制的研究[J].机械工程学报,2011,47(3):152-158.Wang Zhicheng,Yu Dong,Zhang Xiaohui,et al.Study on Reliable Communication Mechanism of Field-bus for Numerical Control System[J].Chinese Journal of Mechanical Engineering,2011,47(3):152-158.

[8]Preissig S,Beal D,Jacquiot A.采用Linux与DSP/BIOS RTOS实施双OS信号处理技术[J].电子设计技术,2009(3):70-73.Preissig S,Beal D,Jacquiot A.The Implementation of the Dual OS Signal Processing Technology Based on Linux and DSP/BIOS RTOS[J].EDN China,2009(3):70-73.

[9]王超,陈香兰,周学海,等.异构多核平台上基于任务划分和调度的性能评估方法[J].中国科学院研究生院学报,2012,29(2):257-263.Wang Chao,Chen Xianglan,Zhou Xuehai,et al.Performance Evaluation Based on Task Division and Scheduling in Heterogeneous Multi-core Systems[J].Journal of Graduate University of Chinese Academy of Sciences,2012,29(2):257-263.

[10]蒋建春,汪同庆.异构多核处理器的任务调度算法[J].计算机工程与应用,2009,45(33):52-56.Jiang Jianchun,Wang Tongqing.Task Scheduling Algorithm for Heterogeneous Multi-core Processor[J].Computer Engineering and Applications,2009,45(33):52-56.

[11]董珍.异构多核处理器的任务调度分配问题及算法研究[D].哈尔滨:哈尔滨工程大学,2010.

[12]彭蔓蔓,徐立超,王颖.异构多核处理器的任务分配及能耗的研究[J].计算机应用研究,2010,27(5):1729-1731+1736.Peng Manman,Xu Lichao,Wang Ying.Task Allocation and Energy on Heterogeneous Multi-core Processors[J].Application Research of Computers,2010,27(5):1729-1731.

[13]林立明,于东,胡毅,等.一种嵌入式总线运动控制器的实时系统设计[J].中国机械工程,2013,24(4):494-499.Lin Liming,Yu Dong,Hu Yi,et al.Design of Realtime System for a Fieldbus-based Embedded Motion Controller[J].China Mechanical Engineering,2013,24(4):494-499.