多速率滤波器组IP 核的高效高速实现方法研究

贺天良 谭哲文

(1.中国人民解放军92665 部队三大队 张家界市 427200)

(2.湖南澧水流域水利水电开发有限责任公司 长沙市 410004)

近年来,多速率数字信号处理与M 带滤波器组作为现代通信与信息处理领域的一种新的技术,在许多领域(通信、图像编码、语音编码、雷达,电力系统暂态保护等)受到重视并得以应用,其基本原理都是先通过分析端的一组滤波器及其级联的抽取器将输人信号分解为多个子带信号,在子带域根据应用场合不同进行相应的处理,最终在综合端通过一组内插器及其级联的综合滤波器组将子带信号恢复成为原始输入信号或稍有失真的原始信号。

对于那些有海量信息待处理的工程应用来说,应用多速率滤波器组来提高计算效率和速度是一种有效的途径,而分析/综合滤波器组实现是关键部分之一。多速率滤波器组的有效实现形式尤其重要,因此随着精确重构滤波器组的基本理论逐渐趋于成熟。

1 分布式算法(distributedarithmetic,DA)及其并行实现

1.1 DA 算法

DA 算法是一项重要的FPGA 技术,广泛地应用在卷积、相关、DFT 计算和RNS 反演映射等“乘积和”之中。

一个线性时不变网络的输出可以用式(1)表示,

式中 y——某时刻网络的输出;

x[n]——这一时刻的第n个输入变量;

c[n]——第n个输人变量的权值。

在线性时不变系统中,对于所有时刻,c[n]都是常量。 如果该网络表现为滤波器,常量c[n]即为滤波器系数,变量x[n]为信号源的抽样数据(如A/D的输出)。 那么c[n]x[n]就变成了一个常数乘法。 这是实现DA 设计的一个先决条件。 考虑“乘积和”内积如下。

假设系数c[n]是已知常数,x[n]是变量。 有符号DA 系统假设变量x[n]的表达式如下:

其中xB[n],xb[n]∈[0,1],xb[n]表示x[n]的第b 位,xB[n]符号位,而x[n]也就是x 的第n 次采样,而内积y 可以表示为:

函数f(c[n],xb[n])的实现方法就是利用LUT 查询表实现映射f(c[n],xb[n]),即每个括号中进行的是输人变量的某一个数据位和所有常数(c[0]~c[N-1])的每一位进行位与并求和。 而指数部分则说明了求和结果的位权。 这样就可以建立查找表来实现括号中的操作了,其查找表用所有输人变量的同一位进行寻址,如图1 所示。

图1 DA 查询表方式和内容

图1 中所示的DA 查找表,其宽度为对常数c[n]定义的宽度,深度为2N,N 是能够对数据源抽样数据进行处理的数据长度,对于滤波器就表现为滤波器阶数。

1.2 DA 算法的并行实现

若将式(4)每个括号之间的加法并行执行,即将每个DA 查找表的输出采用并行的加法,就得到了全并行结构,如图2 所示。 该实现方法就是利用N个LUT 实现映射f(c[n],xb[n]),n=0...N-1,每个LUT接受一个N 位输入向量xb=[xb[0],xb[1],...xb[n]],输出为f(c[n],xb[n])。 各个映射f(c[n],xb[n]),都有相应的二次幂加权并累加。 在一次同时对N个查询表查询后累加就完成了对内积的计算。

图2 并行分布式算法

2 FIR多相分解高效结构

多相表示在多抽样率信号处理中是一种基本方法。 使用它可以在实现整数倍和分数倍抽取和内插时提高计算效率,在实现滤波器组时也非常有用,多相表示亦称多相分解,它是指将数字滤波器的转移函数H(z)分解成若干个不同相位的组。

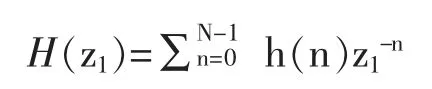

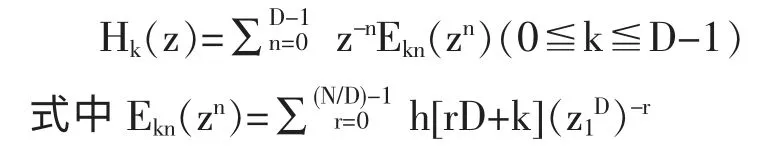

在FIR 滤波器中,转移函数

式中N为滤波器长度。 如果将冲激响应h(n)按下列分成D个组,并设N为整数倍数,即N/D=Q,Q为整数,则

Ek()称为H(z1)的多相分量。式(6)称为H(z1)的多相表示,其网络结构(带抽取器)如图3 所示。

图3 多相分解高效结构

3 多速率分析滤波器组的实现

数字滤波器组是有共同输入或者相加输出的一组数字带通滤波器。 图4 的结构称为多速率分析滤波器组,其子滤波器Hk(z)称为分析滤波器。 它用来将输入信号分解成M个子带信号yk(n),其中每一个子带信号占据原始频带的一部分。 这里主要以余弦调制滤波器组为例研究分析滤波器组的实现。

图4 分析滤波器组

把分析滤波器组中的各通道的分析滤波器采用高效的实现形式,则中D 通道分析滤波器组中的第k 信道分析滤波器Hk(z)可以表示如下:

其中N为D 的整数倍。 进一步可表示为:

上式的矩阵表示为:

上面定义的矩阵E(z)称为I 型多相分解矩阵。

由上可知各相Ek(z2)等价于一低阶的FIR 滤波器,各通道多相卷积部分采用全并行分布式算法实现。对于每一相系数仍较多,则采用分割表法以减小查找表的硬件规模。

4 实验结果与讨论

在QutursII 开发环境下,以APE2000k为目标器件,采用全并行DA 算法,对滤波器组输入以及滤波器系数预先按比例进行缩放化为整数,并采用二进制补码编码,用VHDL 语言设计实现一个10 信道160 阶的余弦调制多速率滤波器组。 对设计结果进行综合、时序仿真,仿真结果见图5。

图5 滤波器组的时序仿真结果

其输入信号取自南网电力系统某超高压线路A相故障短路电流信号。 QutursII 仿真计算结果与MATLAB 运算结果完全一致,证明设计的正确性。对该设计进行时序分析显示,其clock 时钟信号的时序逻辑所需的最小时钟周期为28.957 ns,信号的最大时钟频率为34.53 MHz,能够满足海量数据处理场合的实时性要求。

5 结论

通过采用多项分解技术和分布式算法高效高速实现了分析多速率滤波器组的IP 核设计。由于常系数滤波器乘法可以方便地在一次查表操作,累加中完成,大大减少了滤波的时间,为整套系统中其它电路完成复杂算法节约了宝贵的时间,使整套硬件系统能过满足工业应用实时性的严格要求。 同时由于采用了多速率处理技术使得大部分滤波电路工作在较低频率下,降低了系统的功耗。对具体的设计进行了综合、仿真、时序分析。 本文开发的多速率滤波器组IP 模可应用于要求对海量信息处理实时性要求高的场合。 应用类似的方案还可完成多速率综合滤波器组的IP 的研发。