基于FPGA的灯光智能控制系统

周荣荣,刘亦萍,王 玮,刘 涛

(上海第二工业大学电子与电气工程学院,上海201209)

基于FPGA的灯光智能控制系统

周荣荣,刘亦萍,王 玮,刘 涛

(上海第二工业大学电子与电气工程学院,上海201209)

本系统通过时序逻辑电路设计,采用在Quartus II上用原理图编程的方法,经过仿真验证,最终将程序下载到FPGA开发板上,实现了硬件模拟。实现了以FPGA为核心的灯光智能控制系统。

FPGA;Quartus II;时序逻辑电路

0 引言

随着中国经济的发展,近几年机动车辆的数量急剧增加,道路超负荷承载的现象日趋严重,交通拥挤、堵塞甚至事故频发。特别是在十字路口处,交通灯已成为交通管理必不可少的重要工具。因此,一个智能、稳定、工作效率高的灯光智能控制系统已经成为解决上述交通问题、保障城乡交通有序、安全、畅通的关键。

目前FPGA的应用方兴未艾,因其集成度高、设计便捷、易于修改、可靠性高而成为新的趋势。本系统就基于FPGA芯片,以Quartus II为平台,以时序逻辑电路为基础,实现交通信号灯的智能化控制。尽管实现交通灯的智能控制的方法有很多,如可用PLC实现、可用单片机实现,但用FPGA实现更便于编程修改、仿真验证,运行速度高而故障率低,并且只需较少的硬件电路。

FPGA是英文Field—Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Conf i gurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。FPGA的基本特点有:

1)采用FPGA设计ASIC电路,用户不需要投片生产就能得到合用的芯片;

2)FPGA可做其它全定制或半定制ASIC电路的中试样片;

3)FPGA内部有丰富的触发器和I/O引脚;

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一;

5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

FPGA内部集成锁项环,可以把外部时钟倍频,核心频率可以到几百兆,而单片机的运行速度低得多,在高速场合下,单片机无法代替FPGA。单片机程序是串行执行的,执行完一条才能执行下一条,在处理突发事件时只能调用有限的中断资源;而FPGA不同逻辑可以并行执行,可以同时处理不同任务,因此应用FPGA工作更有效率。

1 功能描述

由一条主干道和一条支干道汇合成十字路口,每个入口处放置红、绿、黄三色信号灯。在主次干道设置传感器检测测量是否到来(本试验用两个开关代替)。主干道处于常通车状态,支干道有车来时才允许通行。主干道和支干道都处于有车状态时,两者交替通行。主干道绿、黄、红灯的显示时间分别为40 s、5 s、25 s。支干道红、绿、黄灯的显示时间分别为45 s、20 s、5 s。需设立40 s、20 s、5 s计数及显示电路。

2 实现方案

2.1 功能逻辑实现

2.1.1 控制系统框图

用自顶向下的方法将试验所需完成的功能设计成如图1所示的控制系统框图。根据控制系统框图可以看出主控电路是整个电路的核心。

图1 控制系统框图Fig.1 Block diagram of control system

2.1.2 逻辑状态转换

分析问题,将信号灯的显示分为4个状态,4个状态对应计时器的4种计时时间。如表1为4种状态转换表,表示各状态对应的信号灯的显示及计时器的计数关系。

表1 状态转换表Tab.1 State transition table

选用JK触发器,其输出为Q2,Q1(见表2)。

表2 状态编码Tab.2 Status code

设车辆检测信号为A、B。

C、D、E分别与40 s、20 s、5 s计数器连接。

A=0,主干道无车;A=1,主干道有车;

B=0,支干道无车;B=1,支干道有车;

C=0,40 s定时未到;C=1,40 s定时已到;

D=0,20 s定时未到;D=1,20 s定时已到;

E=0,5 s定时未到;E=1,5 s定时已到。

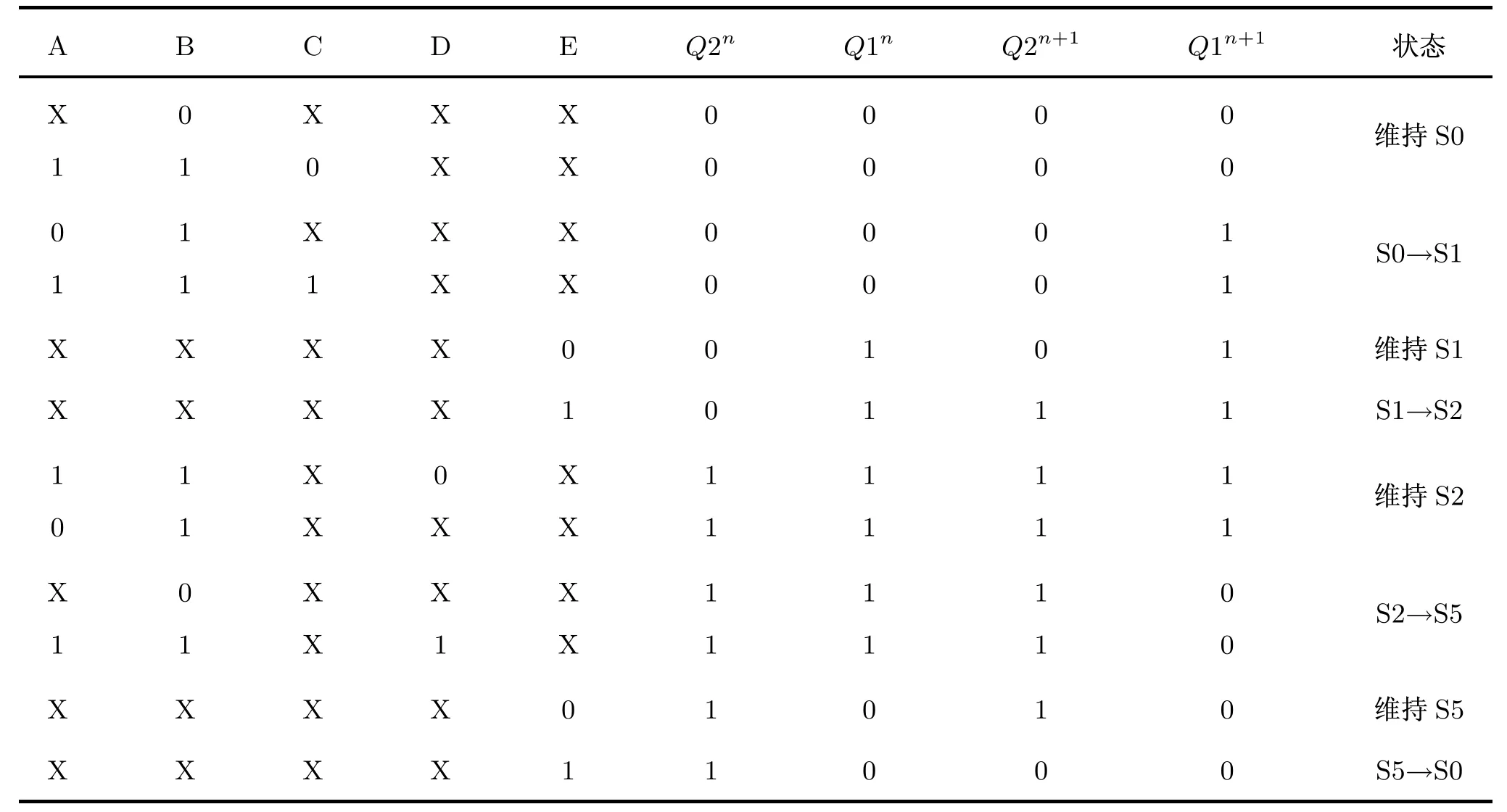

逻辑赋值后的状态表及状态转换如表3所示。

表3 逻辑赋值后状态表Tab.3 Status table after logical assign

2.2 电路设计

本系统以Quartus II为开发设计平台,通过时序逻辑电路设计,以原理图方式编程,经编译下载后在硬件上达到本系统预设逻辑功能要求。

2.2.1 分频

本系统选用Cyclone II FPGA系列的EP2C5Q208C8芯片为主控芯片。查阅有关资料得知此芯片的振荡频率为20 MHz。使用74 290来进行分频,经过7次的十分频和1次的二分频,使输入到主控电路及定时电路的CP频率为1 Hz,即脉冲周期为1 s。

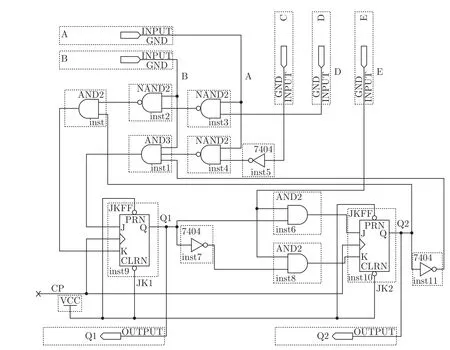

2.2.2 主控电路

根据逻辑状态转换表在Quartus II上设计的主控电路如图2。传感器检测测量用两个拨码开关代替。C、D、E数值状态变化分别用拨码开关控制,CP输入的脉冲为经过分频得到的频率为1 Hz的脉冲。用LED来显示输出,以检查电路输出是否符合要求。将主控电路烧入FPGA开发板中,LED显示符合表2所示的状态转换。将主控电路进行仿真,得到如图3所示的波形图。显然,主控电路的波形图与理论设计相符合。

2.2.3 计数器驱动电路

交通控制灯涉及到红黄绿灯依次点亮的问题和点亮延时的问题,所以需要计数器来解决这两个问题。图4为计数器驱动电路,以解决这两个问题。将计数器驱动电路增加到图2的主控制电路中,进行电路联调。经仿真,观察输出波形,得到的波形符合表1的设计要求。将图4中所标的cp40、cp20、cp5端分别作为40 s、20 s、5 s计数器的输入时钟脉冲。将图2中的C、D、E端分别连接到40 s、20 s、5 s带有数码管显示的计数器电路中。在Quartus II上编译,将系统烧录到FPGA芯片中,在开发板上观察到LED[0]、LED[1]的发光次序及发光时间与表1所表示的状态一致。

图2 主控电路图Fig.2 The main control circuit diagram

图3 主控电路仿真波形图Fig.3 The main control circuit simulation waveform

2.2.4 译码驱动电路

图5为译码驱动电路,将两个JK触发器的输出状态译成在不同信号灯上表现亮灯的信号,用来控制信号灯的显示次序。将此电路增加到上一节得到的电路中(去掉图2中的两个JK触发器引出的两个输出到LED的脚),进行仿真,观察输出波形,输出的LED[5:0]的波形及cp40、cp20、cp5的波形实现了表3所示的状态转换。

3 结论

如图6所示,得到4种状态,分别对应表1的4种状态。4种状态的维持时间分别为40 s、5 s、20 s、5 s。即主干道绿、黄、红灯的显示时间分别为40 s、5 s、25 s,支干道红、绿、黄灯的显示时间分别为45 s、20 s、5 s。将2.2.4节中所得到的电路,编译程序,烧录到FPGA开发板中,观察LED灯的显示转换、LED灯的显示延时及计数器电路中所带的数码管显示,符合表3中列出的状态转换要求。所以,得到的主控制电路达到了预设逻辑要求,达到了以FPGA为核心的灯光智能控制系统在硬件上实现的设计要求。用二—五—十进制计数器74 290进行分频以及整个系统的原理图法编程设计、仿真验证及硬件实现是本系统的特色。

图4 计数器控制电路Fig.4 Counter control circuit

图5 译码驱动电路Fig.5 Decoding and driving circuit

本系统弥补了现行交通灯的不足。道路设有道路车辆检测传感器,实现了车辆和交通信号灯的信息交互,在保证交通安全的前提下,使交通信号灵活智能化,实现了交通效率最大化,在一定程度上到达了减轻交通拥堵的现象。传统交通信号灯控制系统的设计方法基于中、小规模集成电路进行,电路复杂、故障率高、可靠性低。利用EDA技术采用超大规模可编程器件FPGA实现,可降低设计成本,缩短设计周期,保证设计过程的正确性,为数字系统的设计带来了极大的灵活性。

图6 最终各信号灯显示结果Fig.6 The f i nal display results of LEDs

[1]康华光.电子技术基础-数电部分[M].第五版.北京:高等教育出版社,2006.

[2]武俊鹏,孟昭林,付小晶.数字电路与可编程技术实验教程[M].黑龙江:哈尔滨工业大学出版社,2007.

[3]张顺兴.数字电路与系统设计[M].南京:东南大学出版社,2004.

[4]黄智伟.FPGA.系统设计与实践[M].北京:电子工业出版社,2005.

[5]李大社.基于Quartus II的FPGA/CPLD设计实例精解[M].北京:电子工业出版社,2010.

[6]罗朝霞,高书莉.CPLD/FPGA设计及应用[M].北京:人民邮电出版社,2007.

[7]李国丽,朱维勇,何剑春.EDA与数字系统设计[M].机械工业出版社,2009.

[8]袁小平.电子技术综合设计教程[M].北京:机械工业出版社,2008.

[9]江国强.EDA技术习题与实验[M].北京:电子工业出版社,2005.

[10]赵曼,徐和根.基于FPGA的椭圆曲线密码(ECC)算法硬件设计[J].机电一体化,2013,19(1):85-88.

[11]李军,张波,刘品宽,等.基于FPGA的增量式编码器接口电路的设计[J].机电一体化,2012,19(2):58-61.

[12]KUON L,TESSIER R,ROSE J.FPGA Architecture:Survey and Chanllenges[M].USA:Now Publishers Inc.,2008.

The Controlled Intelligent Lighting System Based on FPGA

ZHOU Rong-rong,LIU Yi-ping,WANG Wei,LIU Tao

(School of Electronic and Electric Engineering,Shanghai Second Polytechnic University, Shanghai 201209,P.R.China)

The system is designed through the use of sequential logic circuit.After making the schematic program f i le on Quartus II,the simulating wave can prove whether or not it is right according to the logic relations.Also,the hardware simulating is realized in the FPGA development board by underdown the program.The controlled intelligent lighting system has come true with the core of FPGA.

FPGA;Quartuse II;sequential logic circuit

TP271

A

1001-4543(2013)02-0111-06

2013-04-10;

2013-05-13

周荣荣(1991–),女,浙江人,在读大学生,专业方向为电子信息工程,电子邮箱zhourr37@163.com。

2013年度校级大学生科技资助项目(No.2013-xjkj-015);上海第二工业大学科研基金(编号:EGD13XQD20)