基于TWI接口实现AVR单片机主从机通信

周永刚

(中国电子科技集团公司第四十一研究所,山东青岛266555)

0 引言

AVR ATmega 系列单片机片内集成两线串行接口TWI 模块。采用TWI 协议,设计者可通过两根双向总线,即一根时钟线SCL 和一根数据线SDA,最多连接128 个从设备[1]。实现总线连接时唯一需要增加的外部设备是两条总线上的上拉电阻。所有与总线相连的设备都需要定义各自的设备地址。 实际上,TWI 接口时序与常见的I2C 总线是兼容的,因此,只需要控制相关寄存器,就能够实现通过TWI 传输数据,TWI 通信工作于主从模式,把系统任务进行了合理的分工,节省了硬件资源,减少了工作量,从而使编程简单,开发更容易。

1 TWI 接口简介

TWI 总线是简单同时强大而灵活的通信接口, 具有最高达400kHz 的数据传输率。 TWI 总线协议可仅用两根线将不同的设备互连到一起。 支持主机和从机操作、多主机仲裁。 AVR 单片机的TWI 模块由以下几个子模块构成[2]:

1.1 SCL 和SDA 引脚

当CPU 对应的端口设置为SCL 和SDA 引脚时,可以设定相应I/O 口内部上拉电阻有效,这样可以省略外部的上拉电阻。

1.2 波特率发生器

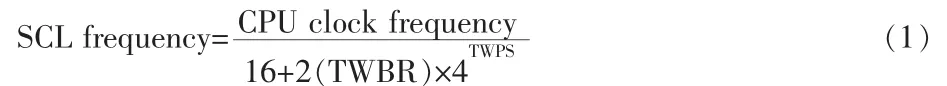

TWI 工作于主机模式时, 时钟信号SCL 的周期由比特率发生器控制。 具体由TWI 状态寄存器TWSR 的预分频系数以及比特率寄存器TWBR 设定,SCL 的频率计算公式如公式(1):

其中,TWBR 为TWI 波特率寄存器的值;TWPS 为TWI 状态寄存器预分频位的值。 在主机模式下,TWBR 的值应大于10,否则可能会产生不正确的输出。

1.3 总线接口单元

该单元包括数据与地址移位寄存器TWDR, 起始/终止信号(START/STOP)控制器和总线仲裁判定硬件电路。

1.4 地址匹配单元

地址匹配单元将检测从总线上接收到的地址是否与TWAR 寄存器中的7 位地址相匹配。 一旦地址匹配成功,控制单元将按照得到的通知作出相应的响应。

1.5 控制单元

控制单元监听总线TWI 总线,并根据TWI 控制寄存器TWCR 的设置作出相应的响应。 当TWI 总线上产生需要应用程序干预处理的事件时,TWI 中断标志位TWINT 置位,时钟线SCL 被拉低,暂停TWI总线上的数据传输。

1.6 TWI 寄存器

TWBR:TWI 比特率寄存器。

TWCR:TWI 控制寄存器。

TWSR:TWI 状态寄存器。

TWDR:TWI 数据寄存器。

TWAR:TWI(从机)地址寄存器。

2 TWI 总线的使用

AVR 的TWI 接口是面向字节和基于中断的。所有的总线事件,如接收到一个字节或发送一个START 信号等, 都会产生一个TWI 中断。由于TWI 接口是基于中断的,因此TWI 接口在字节发送和接受过程中,不需要应用程序的干预[3]。TWI 状态寄存器TWSR 包含了表面当前TWI 总线状态的值。 应用程序可以读取TWSR 的状态码,判别此时的状态是否正确,并通过设置控制寄存器,决定在下一个TWI 总线周期TWI 接口的工作[4]。

TWI 可以工作于4 种不同的模式,即主机发送模式(MT)、主机接收模式(MR)、从机发送模式(ST)、从机接收模式(SR)。当TWI 上出现多个主机时,就会发生多主机仲裁。除了依靠自身硬件的检测外,还可以通过软件读取TWSR 状态寄存器判断自己在总线中的精确状态,以便为下一步动作提供更精确的诊断依据。

主机模式下,主机可向从机发送或接收数据。为了进入主机模式,必须先发送START 信号; 紧接着的地址包格式决定是进入主机发送模式或者主机接收模式。 如果发送SLA+W,则进入主机发送模式;如果发送SLA+R,则进入主机接收模式。

从机模式下,从机只需要监听TWI 总线,如果接收到SLA+R 并回复ACK 后,则进入从机发送模式;如果接收到SLA+W 并回复ACK后,则进入从机接收模式。

3 系统硬件设计

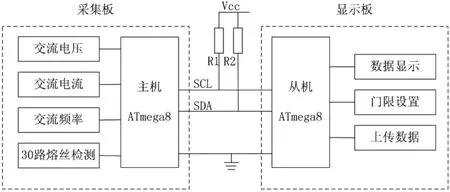

图1 系统硬件结构

在交流电源分配柜中,采集板负责采集交流电压、交流电流、交流频率和30 熔丝告警信息,采集数据后发送到显示板;显示板具备告警门限设置、数据显示以及数据上传服务器等功能。 采集板和显示板的CPU 均采用ATmega8 芯片。基于TWI 接口的硬件电路实现非常方便,只需要将两片ATmega8 芯片的SCL 和SDA 引脚通过上拉电阻与+5V电源相连接即可。 硬件电路如图1 所示。

4 系统软件设计

采集板CPU 采集数据后, 通过TWI 总线发送数据到显示板CPU,显示板CPU 接收数据后,给采集板CPU 回复相应的数据。 显示板CPU 在用户重新设定告警门限后, 需要设定值发送给采集板进行设定。 因此在该系统中采集板CPU 工作于主机发送和主机接收模式,显示板CPU 工作于从机接收和从机发送模式。

4.1 主机模式

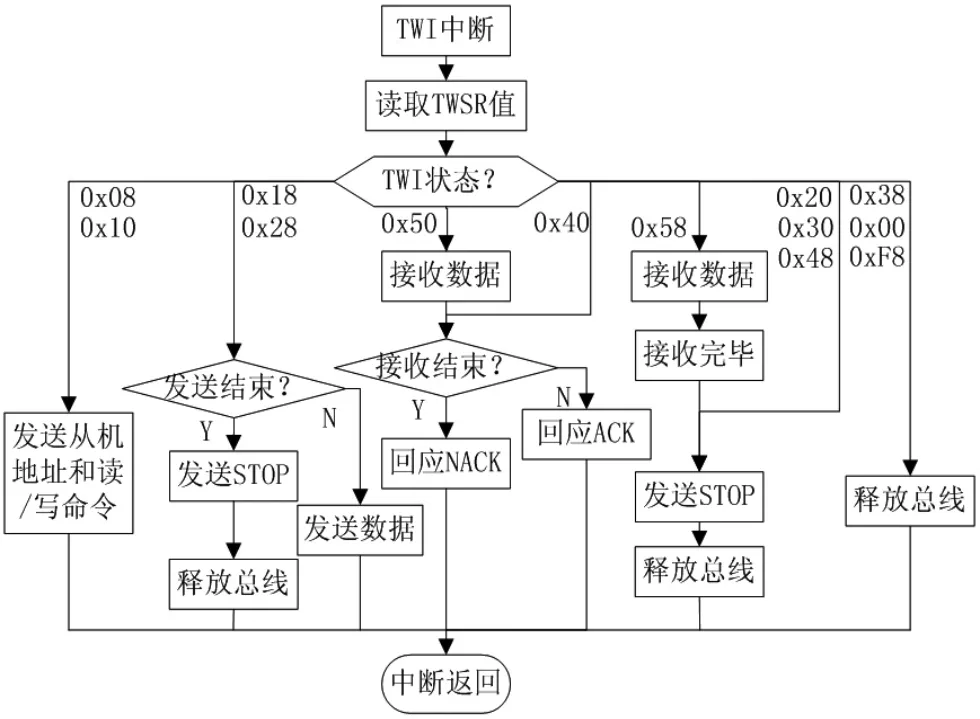

在主机模式[5]下,主机通过发送START 信号启动总线,确认START信号发送后,发送从机地址和写标志位等待从机响应,得到从机的响应后,发送数据到从机。同时在总线空闲时,主机每隔一段时间发送从机地址和读标志位进入主机接收模式,接收从机的告警门限值,接收完后设定主机的门限值。主机在初始化后,需要执行包括主机读、主机写程序,并把读取到数据从缓冲区中转存。 为了保证TWI 总线的稳定运行,只有主机发送模式(MT)和主机接收模式(MR)程序是不够的,还必须有一定的系统总线状态错误处理程序[6],以防止TWI 总线在受到外界干扰时出现故障。考虑本文所设计的系统是主机与从机不会实时发生变化的总线网络系统, 所以对于主机而言还要有容错处理程序。中断流程图如图2 所示。

图2 主机模式中断流程图

4.2 从机模式

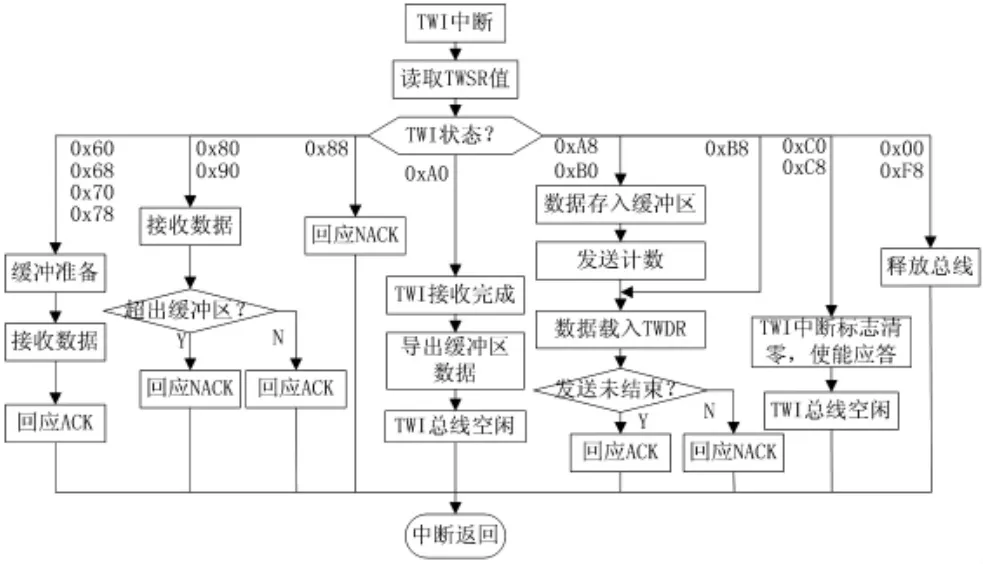

在从机模式[7]下,由于从机也需要处理不通的事件,需要采用中断的方式处理接收和发送数据, 这样可以有效的提高程序的运行程序。通过检测TWSR 状态码,进行不同的处理。 从机在被寻址后,回复主机,判断是否进入从机接收模式或从机发送模式。 进入从机接收模式时,在RAM 中开辟一块数据缓冲区,用于接收数据;进入从机发送模式时,将需要发送的数据装入发送缓冲区,中断程序在自动响应主机进行数据发送。 中断流程图如图3 所示。

图3 从机模式中断流程图

5 结束语

利用TWI 接口实现AVR 单片机主从机通信,简化了硬件和软件设计, 缩短了系统开发周期。 在TWI 通信程序中增加了容错处理程序,使总线运行稳定可靠,提高了系统的抗干扰能力。在通信中采用了TWI 中断,合理安排事件处理时间,有效提高了程序的运行效率。

[1]ATmega8 Datasheet[Z]. ATMEL Corporation.

[2]马潮,詹卫前,耿德根,等.ATmega8 原理及应用手册[M].北京:清华大学出版社,2002.

[3]郭祥军.AVR 单片机的TWI 总线的原理及应用[J].单片机与嵌入式系统应用,2006(8):37-39.

[4]楚天鹏,郑华耀.TWI 接口多机通信的实现[J].装备制造技术,2008(6):96-98.

[5]AVR315: Using the TWI module as I2C master[OL]. www.atmel.com.

[6]汪海波,王卓然,耿德根,等.深入浅出AVR 单片机[M].北京:中国电力出版社,2008.

[7]AVR311: Using the TWI module as I2C slave[OL]. www.atmel.com.