CMOS轨到轨电压跟随器的设计及优化

赵树军

(黑龙江工程学院电气与信息工程学院,黑龙江 哈尔滨150050)

1 跟随器概述

CMOS技术刚刚问世时,人们还不清楚它会对模拟集成电路设计产生多么重要的影响。然而,现在CMOS技术已成为混合信号环境中模拟电路设计的一种选择。这种技术的普及并不是由于设计者的极力推广,而恰恰是工业设计的必然选择[1]。

80年代末,液晶显示技术飞速发展。虽然超扭曲线列在显像效果上不如有源矩阵的液晶显示技术,但对液晶显示技术的显示效果要求并不高,且超扭曲线列结构简单、成本低廉、功率损耗低等方面比有源矩阵的液晶显示技术有着明显的提高,故其在手机、MP3、MP4、计算器等便携式消费电子产品中占有相当大的市场。

跟随器是STN驱动芯片的研究难点,其性能与改善串扰、提高显示质量有很大关联。消费类的STN驱动芯片对跟随器设计和实现提出要求:功率损耗低、输出信号失真较低、电压输出范围较大。这几个要求也是跟随器未来的研究和发展方向[2-3]。

电压跟随器,顾名思义,就是输出电压与输入电压相同,电压跟随器的电压放大倍数恒小于且接近1。电压跟随器的显著特点就是输入阻抗高,而输出阻抗低,一般来说,输入阻抗要达到很高是容易做到的。输出阻抗低,通常可以到几欧姆,甚至更低[4]。

在电路中,电压跟随器一般做缓冲级(buffer)及隔离级[5]。因为电压放大器的输出阻抗一般比较高,通常在几千欧姆到几十千欧姆,如果后级的输入阻抗比较小,那么信号就会有部分损耗在前级的输出电阻中。这个时候,就需要电压跟随器从中进行缓冲,起到承上启下的作用。应用电压跟随器的另外一个好处是提高了输入阻抗,这样,输入电容的容量可以大幅度减小,为应用高品质的电容提供了前提保证[6]。

电压跟随器的另外一个作用就是隔离,在HIFI电路中,关于负反馈的争议已经很久了,其实,如果真的没有负反馈的作用,相信绝大多数的放大电路是不能很好工作的。但是由于引入了大环路负反馈电路,扬声器的反电动势就会通过反馈电路与输入信号叠加,造成音质模糊,清晰度下降,所以有一部分功放的末级采用了无大环路负反馈的电路,试图通过断开负反馈回路来消除大环路负反馈带来的弊端。但是,由于放大器末级的工作电流变化很大,其失真度很难保证[7]。

在这里,电压跟随器的作用正好达到应用,把电路置于前级和功放之间,切断扬声器的反电动势对前级的干扰作用,使音质的清晰度得到大幅度提高。

目前,电压跟随器除了在电乐器方面有较大的应用,其还被广泛应用于ANN(人工神经网络)、LED显示屏、音频功放等诸多领域,发展前景十分乐观。

2 轨到轨电压跟随器的设计及优化

2.1 传统对称式电压跟随器电路描述

传统对称式电压跟随器如图1所示,电路中4个晶体管(M1-M4)连接成两级共漏缓冲器。

图1 传统对称式电压跟随器

这种结构有3个缺点[8]:①由于 NMOS和PMOS之间的栅源电压不匹配,导致它需要很大的补偿电压;②由于MOS晶体管相对于三极管(BJT)的跨导较小,而导致输出阻抗增高;③线性输出摆幅较小。为了尽量避免上述缺点,对电路进行了改进。

2.2 改进后的电路描述

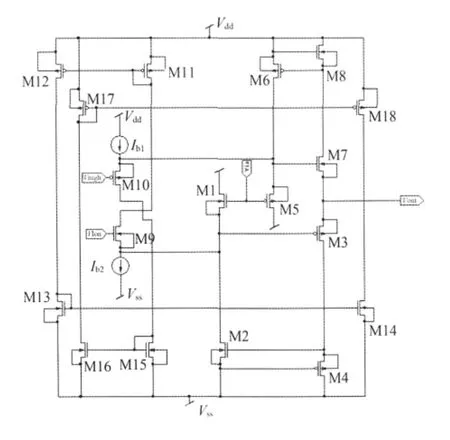

图2的电路原理图是以图1中传统对称式电压跟随器为基础改进获得的。

图2 改进后的轨到轨电压跟随器

M1、M3、M5和M7形成两级共漏,转移电流比率为α的 NMOS和PMOS管(M2-M4、M6-M8)形成电流镜装置,而 M1、M3、M5、M7这4个晶体管被电流镜装置所偏置。M1和M2有相同的漏电流,M3和M4有相同的漏电流,所有的NMOS和PMOS都具有相同的尺寸,M1的栅源电压和M3的栅源电压接近相等。这种栅源电压匹配方法也可以应用于跟随器M5-M8。最终,改进后的电压跟随器的补偿电压将会降到最小[9]。通过运用两个复合管(M1-M4、M5-M8),可以增加 MOS管输出的跨导。跟随器M1-M4和M5-M8的跨导可以分别用式(1)、式(2)表示。

从式(1)、式(2)看出,通过控制转移电流比率α就可以调节输出晶体管的跨导。仿真显示,α取恰当的值时,能够获得很高的跨导。

输入电压的幅度在Vlow和Vhigh之间,此时电路将会作为一种传统电压跟随器,而这种传统电压跟随器会有很高的跨导和很低的栅源电压不匹配现象。通过式(1)、式(2),可以算出输出阻抗,如式(3)所示。

晶体管M1和M9被连接作为差分放大器,假如输入电压比Vlow低,此时M1和M9的偏置电流Ib2的大部分变成 M9的漏电流,Ib2被 M11-M12、M13-M14两个电流镜镜像复制。M14的宽是M13的N倍。输出值能够在负极的过驱动(VDSAT14)范围内摆动,此时输出阻抗 R0(low)由式 1/gM7-α/gM5给出。相似的,晶体管M5和M10被连接作为差分放大器,假如输入电压比Vhigh高,此时M5和M10的偏置电流Ib1的大部分变成M10的漏电流,Ib1被 M15-M16、M17-M18两个电流镜镜像复制。M18的宽是M17的N倍。输出值能够在正极的过驱动(VDSAT18)范围内摆动,此时输出阻抗R0(high)由式1/gM3-α/gM1给出[10]。

2.3 对改进后的电路图完成仿真并记录数据

直流(2.5V)传输特性,如图3所示。

图3 直流(2.5V)传输特性

给定Vdd=2.5V,负载R=600Ω,对电路电源电压进行直流(DC)扫描分析,其扫描范围为0~2.5V,从图4可以看出,0.7~1.4V电压跟随效果线性度很高。直流(3.3V)传输特性如图4所示。

图4 直流(3.3V)传输特性

给定Vdd=3.3V,负载R=600Ω,对电路电源电压进行直流(DC)扫描分析,其扫描范围为0~3.3V。由图4可以看出,0.7~1.7V电压跟随效果线性度很高,基本达到设计要求。经过与图3对比得出,提高Vdd值可以增大输入电压跟随范围。改进后电压跟随器的频率响应如图5所示。

本文设计的CMOS轨到轨电压跟随器在驱动负载R=600Ω的情况下,此电路在频率1k~1G的范围内,得出图5所示的电压增益输出曲线。由图5可知,改进后的电压跟随器增益为-0.4dB,截止频率(-3dB)大约为500MHz。改进后的电路基本能满足所要求的设计指标。M1、M3、M5、M7跨导如图6所示。

图5 改进后电压跟随器的频率响应

图6 M1、M3、M5、M7跨导

通过T-Spice网表的编辑,仿真出图3~4波形,导出 M1、M3、M5、M7的(.out)输出文件,然后粘贴至Excel表格中,编辑公式(2)~(3),最终得出输出阻抗图形如图7所示。

图7 输出阻抗

由图7可知,CMOS轨到轨电压跟随器在驱动负载R=600Ω情况下,输入电压在0.8~1.7V跟随范围内,输出阻抗小于20Ω,基本达到设计要求。

结果表明改进后的电压跟随器具有较低的输出阻抗、较大的线性输出电压摆幅、较大的截止频率。改进后的电压跟随器在负载R=600Ω的情况下,提高Vdd值可以增大输入电压跟随范围(Vdd从2.5V提高到3.3V)。改进后的电路在频率1kHz~1GHz的范围内工作时,可以得到增益约为-0.4dB,截止频率(-3dB)约为500MHz。当输入电压在0.7~1.7V范围内变化时,输出与输入表现出较好的跟随效果,最大输出阻抗低于20Ω,以上设计指标已经满足了最初的设计要求。写出各MOS管宽长比的简单计算过程,最后列出改进后电路的各个MOS管宽长比数值。

3 结束语

本文设计一种AB类高性能CMOS轨到轨电压跟随器。设计过程中,针对设计需求首先应用理论计算得到所有MOS管的宽长比值。通过研究传统对称式电压跟随器与改进后的电压跟随器,比较性能优缺点,对电压跟随器有了更深刻的认识。介绍了电压跟随器的基础知识,列举了两种电压跟随器的电路,并将传统对称式电压跟随器与改进后的电压跟随器进行了比较,分别分析了它们的具体结构,并简单介绍了各MOS管组成的模块功能,使改进后的电压跟随器的电路可以在电源电压为2.5V或者3.3V条件下工作,电压跟随范围拟定1~1.5V,能驱动600Ω的负载,截止频率(-3dB)在200MHz以上,并且保证输出阻抗小于30Ω。通过本文的理论研究和分析将为进一步的仿真及版图设计打下理论基础,深化对STN驱动芯片的研究和挖掘。AB类高性能CMOS轨到轨电压跟随器具有功率损耗低、输出信号失真较低、电压输出范围较大的特点,能够使液晶显示技术有明显的提高,从而应用于手机、MP3、MP4、计算器等便携式消费电子产品市场。

[1]ALLEN P.E.Douglas R.Holberg.CMOS模拟集成电路设计[M].北京:电子工业出版社,2005:8-9.

[2]蒋研飞.应用于缓冲放大器的设计与研究[D].北京:北京大学,2006.

[3]华成英,童诗白.模拟电子技术基础[M].北京:高等教育出版社,2006:327-329.

[4]ALLEN P.E.Douglas R.Holberg.CMOS模拟集成电路设计[M].北京:电子工业出版社,2005:8-9.

[5]蒋研飞.应用于缓冲放大器的设计与研究[D].北京:北京大学,2006.

[6]华成英,童诗白.模拟电子技术基础[M].北京:高等教育出版社,2006:327-329.

[7]马场清太郎.运算放大器应用电路设计[M].北京:科学出版社,2011:5-25.

[8]David A.Jones,and Ken Martin.模拟集成电路设计[M].北京:机械工业出版社,2005:105-106.

[9]Manetakis,K,and Toumazou,C,“A new high-frequency very low output-impedance CMOS buffer”[J].IEEE International Symposium on Circuits and Systems.2006,21(1):485-488.

[10]毕查德.拉扎维.模拟CMOS集成电路设计[M].陈绍贵,程军,张瑞智,等译.西安:西安交通大学出版社,2002:243-254.