基于FPGA的参数可调高斯白噪声发生器的设计

王鹏宇,翟丽丽,石巨峰

(解放军91550部队,大连116023)

0 引 言

高斯白噪声是普遍存在的一种噪声源,对电子对抗、遥测系统、通信系统的性能检测起着关键作用。将系统各模块通过高斯白噪声信道测试,不仅可以检验其抗噪性能,还可以通过理论仿真对比实测结果验证系统设计的正确性。因此,设计一个能够在特定条件下模拟高斯白噪声的发生器对一个系统从理论层走向实际应用层有着重要意义[1-4]。

通过硬件模拟高斯白噪声可以采用物理噪声发生器,虽然其精度较高,但其实现电路复杂,成本较高且噪声功率不易控制。本文提出的基于现场可编程门阵列(FPGA)的高斯白噪声发生器采用线性同余法产生随机控制Box-Muller变换器的地址,使用上位机控制末端放大器参数改变噪声功率,充分考虑硬件资源的优化,具有结构简单、模拟速度快、噪声周期长、相关性好的特点。设计方案先通过Matlab仿真,再用VerilogHDL硬件描述语言在FPGA上移植,能够较好地满足实际测试的需求。

1 总体设计方案

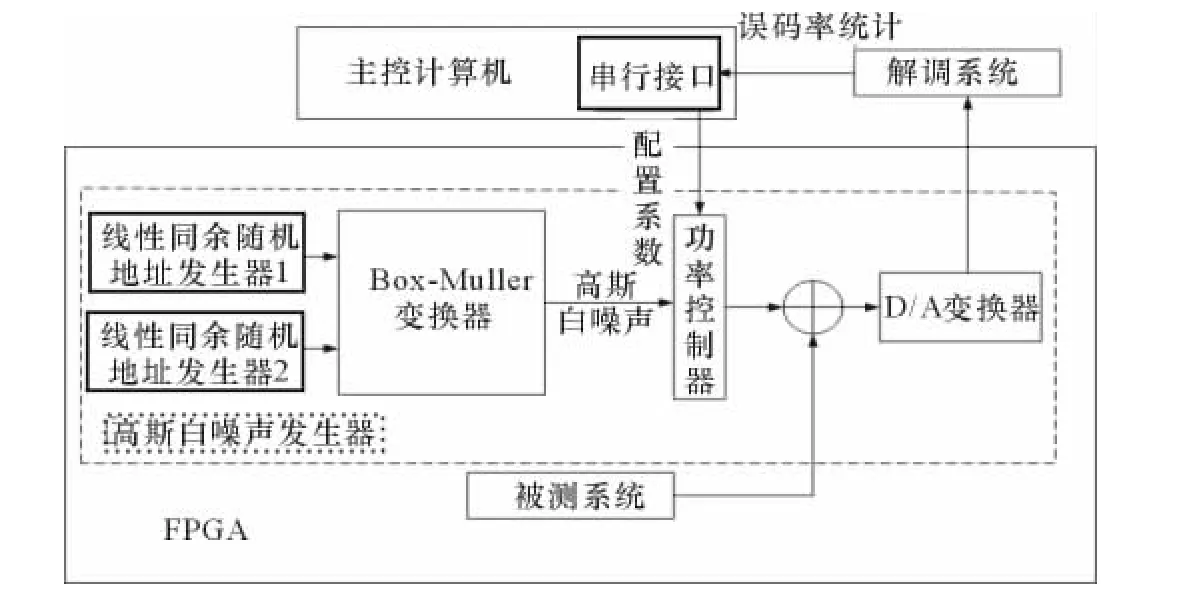

本文提出的噪声发生器总体设计方案如图1所示。其主要包括计算机控制模块,线性同余随机地址发生器模块,Box-Muller变换器模块,噪声功率控制模块,加法器模块,数字/模拟(D/A)变换器输出模块和串行接口模块。

通过一种改进的线性同余发生器产生2组随机数,每次时钟上升沿到来时使用随机数作为Box-Muller变换器内2个数据存储单元的地址进而输出相应数据。主控计算机根据用户选择的相应信噪比通过串行接口配置功率控制模块的系数a产生相应功率的噪声,将其与被测试系统信号进行叠加,经加法器通过D/A转换器输出模拟信号。

图1 高斯白噪声发生器总体设计方案

2 各模块设计与仿真

2.1 改进的线性同余随机地址发生器

产生均匀随机数的方法有多种,比如说线性同余法、移位寄存器法、进位加等方法。本文采用改进的线性同余法生成随机数,具有速度快、节约资源和生成序列随机性好的特点[5]。

通过数字模拟产生的随机数与真正的随机数不同,它是经过一定的递推具有固定周期的伪随机序列。但只要根据实际需求,产生的序列周期足够长,满足均匀性和独立性,就能够在特定条件下具有与真正随机数相似的性质。

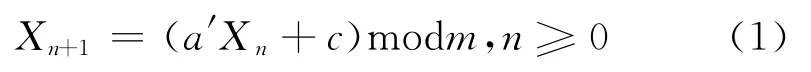

线性同余法的递推公式为:

式中:m为 模数,m>0;a为乘数,1<a<m;c为增量,0≤c<m;X0为开始值,一般0≤X0<m。

一般序列周期小于m。例如要产生周期为32 768的随机地址,那么设置m为215=32 768显然不合适,为了能够遍历1~32 768之间所有数,充分体现其随机性,可以设置m为220=1 048 576,然后将输出的数据除以25=32后取整处理。这里的a取2即可,通过仿真得到的效果符合条件。c取0可以提高生成速度,节约硬件资源。

为了进一步增加周期性,每次算法产生的数据到达周期m后改变初始值X0,这样就会产生另外一组周期为m但数据不完全相同的序列。理想情况下可以做到周期为m×m。其算法流程如图2所示。

2.2 Box-Muller变换器模块

图2 线性同余算法流程

Box-Muller变换法是将在(0,1)之间均匀分布的随机数经过一定变化,生成符合高斯分布的随机数。设x1,x2符合(0,1)之间的均匀分布,那么对x1,x2做一定变化:

n即为最终生成的高斯分布随机数,该方法叫做Box-Muller变换法。

为了减少FPGA硬件的计算量,由Matlab仿真产生x1,x2,然后建立f(x1)和g(x2)的数据表,对其量化处理后存入FPGA的内部只读存储器(ROM)中。这里由于g(x2)是周期函数,只需存储1/4周期即可以节约FPGA的存储单元。

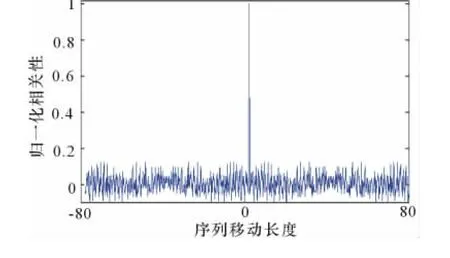

将线性同余法产生的随机数作为f(x1)和g(x2)的地址读取数据。高斯随机序列的归一化相关性仿真如图3所示,可见其随机序列具有良好的独立性。

图3 高斯随机序列自相关性仿真

其功率谱仿真如图4所示,该序列的功率谱是一条均匀的白谱。

图4 高斯随机序列功率谱仿真

2.3 噪声功率模块

在信号功率固定情况下,为了产生不同信噪比,可以通过改变噪声功率来实现。设信号平均功率为Ps,噪声平均功率为Pn,噪声输出乘系数为a,由于随机信号的平均功率等于其交流功率和直流功率之和,而高斯白噪声直流分量为0,则Pn的值等于其方差的大小。当设乘系数a=1时,噪声方差为D,则:。

通过用户选择的SNR计算出相应的a值,在主控计算机内建立switch-case表,经串行接口将对应一定信噪比的a值输入到FPGA内部完成相应计算。

3 硬件测试结果与分析

3.1 噪声功率谱测试

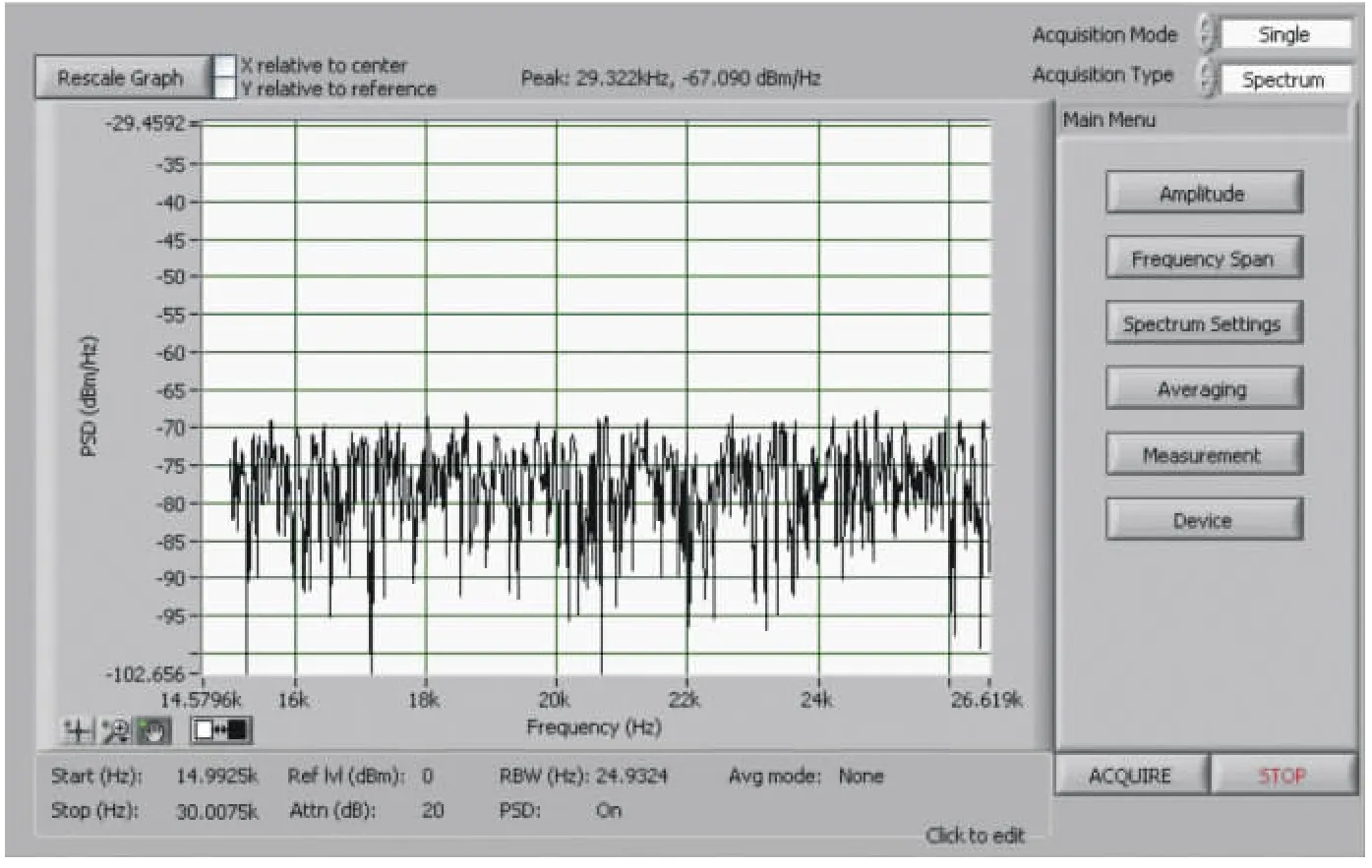

图5是使用NI公司的虚拟频谱分析仪对纯噪声频谱进行的测试,可见在所关心的频率范围内功率谱分布均匀近似为一条线,噪声体现出理想白噪声的特性,能够较好地模拟高斯白噪声信道特性。

图5 噪声功率谱测试

3.2 噪声直方图统计

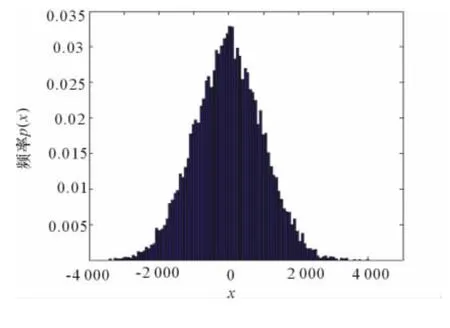

将产生的噪声导入Matlab做直方图统计,如图6所示。横轴表示区间,纵轴表示落入该区间的概率,总体上呈正态分布,可见其概率密度函数是高斯分布的,验证了噪声产生算法的正确性。

3.3 误码率性能测试

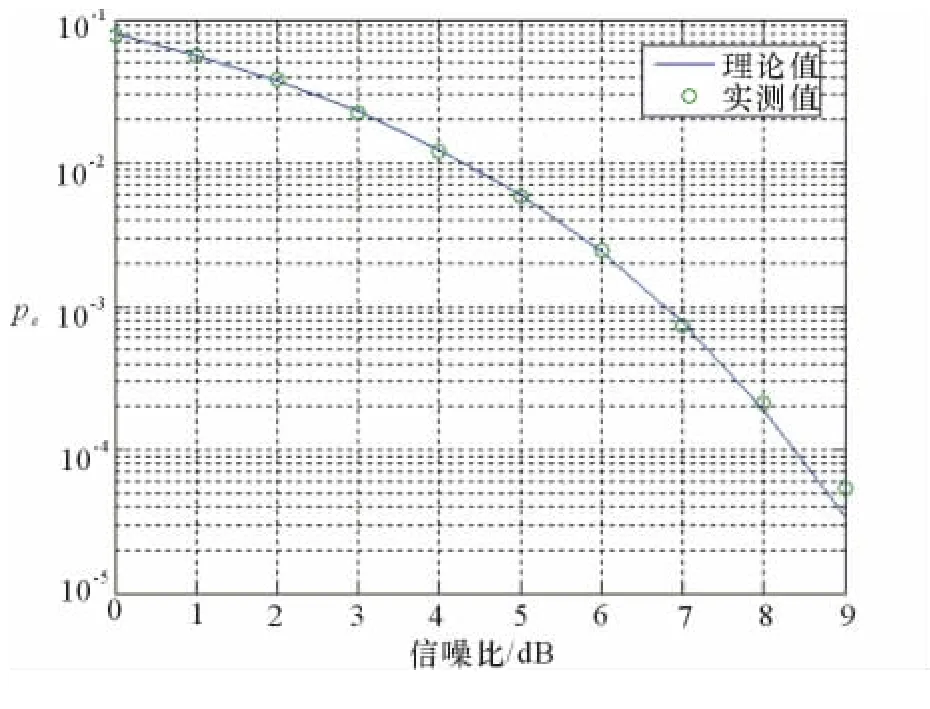

为了进一步验证本系统产生的高斯白噪声与理想噪声的相似程度,将被测系统产生的信号调整为常见的二进制相移键控(BPSK)信号,通过噪声叠加后进行相关解调,解调后的数据通过串口上传主控计算机,计算机内存储了发送数据,通过对比收发数据进行误码率统计[6]。

图6 噪声直方图统计

误码率实测的统计曲线和理论曲线如图7所示,可见由FPGA生成的噪声对系统产生的影响和理想噪声产生的影响基本吻合,说明本系统设计的合理性。

4 结束语

本文提出的基于FPGA的高斯白噪声发生器,通过算法优化节约了硬件存储资源,生成速度快。通过理论仿真验证了其特性符合高斯白噪声性质。应用到工程实践中能够满足实际需求,且取得了良好效果。

图7 BPSK误码率曲线

[1]张萍,戴光明.高斯随机噪声实时生成方法实现研究[J].电子技术应用,2004,29(4):10-12.

[2]尹中秋,石春和,陈明生,等.FPGA的可调参数白噪声与高斯白噪声生成器[J].火力与指挥控制,2008,33(8):109-111.

[3]樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2007.

[4]黄本雄,侯洁,胡海.高斯白噪声发生器在FPGA中的实现[J].微计算机信息,2007,23(7):165-167.

[5]刘正高.标准均匀随机数的产生方法分析[J].航天标准化,1996,13(5):11-13.

[6]季雄,段吉海,胡媛媛.基于VerilogHDL的UART设计[J].微计算机信息,2006,6(2):230-232.