基于PLD的VGA显示器字符显示实验设计

陈自龙,汤勇明

(东南大学 电子科学与工程学院,江苏 南京210096)

我院先后在“可编程逻辑器件的基础与应用”和“电子系统设计”等课程建设中开展了PLD 教学实验的开发[1]。本文介绍了一个基于PLD 的VGA(Video Graphics Array)显示器字符显示实验设计,它利用PS/2 键盘输入字符,然后在VGA 显示器上依次显示(可以换行)。其中涉及到的知识点包括:VGA 接口时序,RAM/ROM 读写和PS/2 键盘接口解码等。本实验涉及到PLD 设计多项通用关键知识点,对PLD 实验平台的资源要求相对较少,可移植推广到不同类型的PLD 实验平台开展教学应用。

1 实验设计和开发平台

本实验设计的目标是PLD 开发平台适用的综合开发案例,通过PS/2 键盘实现字符输入,在VGA显示器上显示英文字符的功能。本实验的设计可以划分为五大模块:VGA 显示接口模块、显示缓存RAM 模块、字模存储ROM 模块、PS/2 键盘解码模块和核心控制模块等,如图1所示。

图1 整体模块划分图

核心控制模块负责其余四大模块之间的协调和数据传送,而这四大模块功能独立并相互分工。涉及到的知识点包括:VGA 接口标准时序的发生,显示缓存RAM 的输出与VGA 显示的同步,基于流水线的ROM 读取和RAM 写入技术和PS/2 键盘接口解码技术。

本实验的VGA 显示需要外接VGA 兼容显示器,输入需要外接PS/2 键盘。本实验中PLD 芯片需要具有一定的片上存储资源,以用作显示缓存RAM 和字模ROM,建议采用FPGA 而不是CPLD。存储资源的需求大小可以调节,对于存储资源相对紧张的PLD 芯片,可以在实验设计中减少显示字符的个数,以减小显存RAM 消耗的存储资源。字模ROM 消耗的存储资源大小固定(当然也可以减小支持显示的字符个数来减小),相对显存RAM 其消耗不大。

本实验选取了我院自主开发的FPGA DSK 开发平台设计。FPGA DSK 开发平台的核心为Altera 公司CycloneII 系列型号为EP2C8Q208C8 的FPGA 芯片,逻辑资源、存储资源以及引脚资源较为丰富,同时,开发板上具有PS/2 键盘接口和VGA 显示接口,满足本实验要求。

2 PLD 实验程序设计

2.1 VGA 标准时序的实现

VGA 是IBM 在1987年推出的一种视频传输标准,具有分辨率高、显示速率快和颜色丰富等优点,在彩色显示器领域得到广泛应用[2,3]。

VGA 接口共五路信号:红、绿、蓝三路数据信号,场同步和行同步两路控制信号。

Verilog 实现VGA 时序的主要思想是,利用像素时钟(pixel_clock)生成行同步信号,在行同步信号的基础上,生成场同步信号。并输出水平坐标和垂直坐标。时序信号产生原理如图2所示。

图2 VGA 时序信号产生原理图

2.2 显示缓存RAM 控制

FPGA DSK 实验平台允许R、G、B 三基色各自1bit 编码,实现8 色显示。本实验中为了节省存储资源,对VGA 每点像素的颜色值进行二值化处理,即每个像素只有黑白两色。程序设计中引入显存RAM 模块,存储VGA 显示屏幕上任一像素点的颜色值。

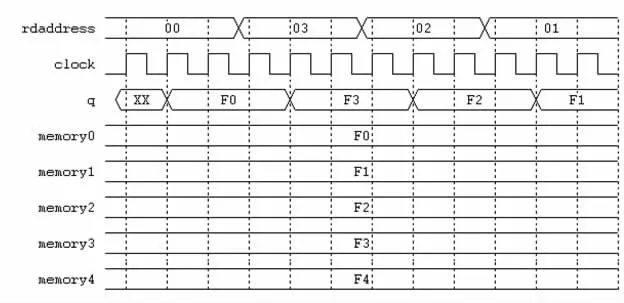

显存RAM 可调用Quartus II 的宏功能(Mega-Function)模块库,自动生成双口RAM,其读时序如图3所示。

图3 双口RAM 读时序

从上图可以看到,在第一个时钟的上升沿,读数据地址为0,表示要读取地址0 的数据,此时输出q无效,读地址被锁存。到第二个时钟上升沿时,数据输出q 端开始输出地址0 的数据(F0)。可见,双口RAM 从锁存读地址到输出相应数据需要经历(延迟)一个时钟周期。程序设计中需要处理好该信号输出延迟,保证图像显示时位置对应。

2.3 字模ROM 控制

包括英文字母、数字、标点等在内的键盘输入字模数据均存放在字模ROM 中,核心控制模块根据键盘输入信息将对应的字模数据读出并写入到显存RAM 中合适的位置。ROM 的读延时也是一个时钟周期,为了解决读延时和数据稳定问题,需要合理地设计“读ROM—写RAM”的时序。该时序设计如图4所示[4]。

图4 “读ROM—写RAM”时序图

从图中第一个时钟下降沿开始,设置ROM 读地址的起始地址(这里是地址0),到下个时钟上升沿时,该地址被ROM 锁存,再经过一个时钟周期后,该地址的数据(F0)被读出。在F0 被读出后的时钟下降沿,设置RAM 的写地址(假定为地址0),并置RAM 的写使能信号有效(高电平)。同时,将ROM 的读地址加一。当下一个(从0 时刻开始的第4 个)时钟上升沿到来时,RAM 锁存写地址,存储F0,并且在第5 个时钟上升沿处会自动加载ROM的新地址处的数据,以便下次RAM 写入。由于一个字模数据有8 ×12 =96bit,程序中ROM 和RAM的位宽都是8,所以需要读写12 次,才能完成一个字模数据的写入。

2.4 PS/2 键盘的解码

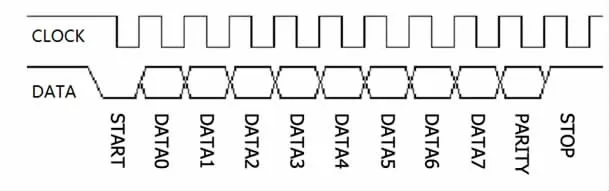

PS/2 是电脑上常见的接口之一,多用于鼠标、键盘等输入设备。PS/2 的时序如图5所示。

图5 PS/2 时序图

当PS/2 设备需要传输数据时,会在PS/2 时钟(CLOCK)的第一个下降沿拉低PS/2 数据线,表示一帧PS/2 数据传输的开始。接着是8 个数据位(都是在时钟的下降沿有效),然后是奇偶校验位,最后是停止位(高电平)。主机在接收完一帧数据后,需要将接收到的串行数据转换成并行数据[5],这就是PS/2 键盘的扫描码。

PS/2 键盘扫描码有两种不同的类型:通码(make code)和断码(break code)。当按键被按下或持续按住时,键盘会发送该键的通码;而当一个键被释放时,键盘会发送该键的断码。根据键盘按键扫描码的不同,可将按键分为如下三类。

(1)一类按键:通码为一个字节,断码为0xF0 +通码的形式。例如对于A 键,其通码为0x1C;断码为0xF0 0x1C;

(2)二类按键:通码为两字节0xE0 +0xXX 形式,断码为0xE0 +0xF0 +0xXX 形式。如Right Ctrl键,其通码为0xE0 0x14;断码为0xE0 0xF0 0x14;

(3)三类特殊按键有两个:①Print Screen 键,其通码为0xE0 0x12 0xE0 0x7C,其断码为0xE0 0xF0 0x7C 0xE0 0xF0 0x12;②Pause 键,其通码为0xE1 0x14 0x77 0xE1 0xF0 0xl4 0xF0 0x77,断码为空。

本设计中只支持第一类和第二类按键,并且认为按键被按下直至弹起才是一次按键事件。

当按下按键时,PS/2 解码模块先将按键通码保存,然后一直等待按键松开,直到接收按键断码,此时一次按键事件结束。接着,按照第二套按键扫描码的规定,将按键通码转换为ASCII 码,并产生一个按键事件信号,等待其他模块处理。PS/2 键盘事件响应流程如图6所示。

图6 PS/2 键盘事件响应流程图

3 教学实验结果

本实验案例设计目标是在VGA 显示器上显示20 行40 列,共800 个宽8 像素、高12 像素的字符(支持47 个常用的英文字符),经VerilogHDL 语言编程实现,已使用Altera 公司的Quartus II 9.0 SP2开发工具进行验证,其编译综合结果如表1所示。

表1 程序编译综合结果

从表1中可见,在FPGA DSK 开发板上最终消耗的存储资源是88192 比特,占芯片总存储资源的53%;使用的逻辑单元数目仅是401 个,占总逻辑单元的5%;使用FPGA 芯片IO 端口9 个,占总端口数的6.5%。程序下载到开发平台后,系统能顺利实现接收和显示26 个英文字母、10 个数字和11 个常用标点共47 个常用字符,行末自动换行等功能。其它一些键盘输入功能,如删除上一个字符、回车换行和大小写输入切换等,可以作为教学实验中的提高性功能加以要求。

EP2C8 芯片在FPGA 芯片中属于中低端产品,其内部逻辑资源数量较少,从上述编译结果可见,本实验对PLD 开发平台要求不高,可移植到其它多种PLD 实验平台上进行,适宜进行教学推广应用。

4 结语

目前很多高校PLD 教学实验平台给出了采用VGA 接口显示静态图形或者静态文字的案例。本文介绍了一个基于PLD 的VGA 显示器字符显示实验的设计,并且就其中涉及到的VGA 视频接口、PS/2 键盘接口和RAM/ROM 控制等一些关键技术做了详细说明。该实验对PLD 开发平台硬件要求低,可移植性强。通过该实验可实现综合性PLD 开发训练,有助于让学生对PLD 开发和应用有更深层次理解,为以后从事PLD 设计和开发打下坚实的基础。

[1] 汤勇明,郑姚生,吴忠.“可编程逻辑器件的基础与应用”课程建设与教学实践[J]. 南京:电气电子教学学报,2007,29(02):7-9.

[2] Video Graphics Array[online]. http://en. wikipedia. org/wiki/Video_Graphics_Array

[3] 廖永清等. 基于FPGA 的VGA 图像动态显示控制器的设计与实现[J]. 北京:电视技术,2011,35(17):52-54.

[4] 秦鸿刚,刘京科,吴迪. 基于FPGA 的双口RAM 实现及应用[J]. 西安:电子设计工程,2010,18(2):72-74.

[5] 陆一鸣,闫华,钟锐. 基于FPGA 的嵌入式系统PS/2 接口的实现[J]. 南京:电子器件,2007,30(03):1105-1108.