基于NiosII的自由落体分析仪的设计*

兰建平,董秀娟

(湖北汽车工业学院 电气与信息工程学院,湖北 十堰 442002)

与通用MCU相比,FPGA采用软件来设计硬件,所有的实现最终都将转化为其内部的硬件逻辑,而且FPGA可以产生精准的时间基准。然而,如果对FPGA内部所有硬件逻辑都通过编程实现,则由于FPGA本身的特点难免使系统中存在竞争冒险,系统稳定性难以保证。而且编程任务量大,难以实现。软核处理器技术是一种全新的设计理念,它将FPGA设计划分为硬件和软件两个方面。硬件可以利用芯片设计商所提供的各类标准外设实现系统所需接口及控制逻辑,软件可以专注于各种控制算法的实现。对于一些通用MCU无法满足的应用(如高精度实时测量、丰富的片内外设、硬件可定制可扩展的系统)来说,FPGA能够满足实时、高精度和硬件可定制等多方面的要求。NiosII是Altera[1]的第二代FPGA嵌入式软核处理器,其指令执行速率可达200 DMIPS。对于本文所设计的自由落体分析仪,NiosII能够满足系统各方面的需求。

自由落体分析仪在测量领域应用非常广泛,可以用来研究落体运动,准确测量地球各点的绝对重力加速度值,对国防建设、经济建设和科学研究有着十分重要的意义。

本文设计了一种基于Altera NiosII软核处理器为核心单元的自由落体分析仪。该系统在FPGA芯片中实现用户自定制的处理器,其硬件结构包括步进电机控制单元、光电编码器信号采集单元、存储器模块、电源模块、UART接口、PC显示终端及SoPC模块Altera CycloneII EP2C8。

1 系统的组成与设计原理

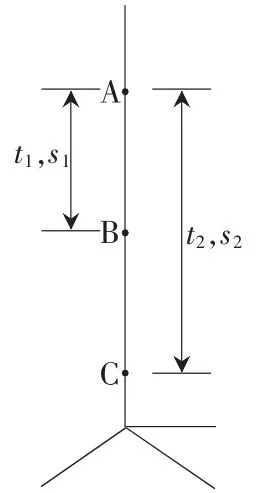

利用小球做自由落体运动来测量时间和位移,然后计算出g的值。测量原理如图1所示。A、B、C是安装在三角座上的3对光电对管(位置可以灵活地上下移动),可见系统设计的关键是精确测量光电门A、B、C之间的距离和下落时小球遮挡 3对光电门的时间间隔。

由图1可知:

图1 测量原理

其中,v0是小球下落时通过 A点的速度,t1是下落时遮挡A、B两个光电门的时间间隔,s1是A、B之间的位移。

其中,t2是小球下落时遮挡 A、C两个光电门的时间间隔,s2是 A,C之间的位移。 由式(1)和式(2)可得:

2 系统的硬件设计

硬件部分的设计可以分为两个部分。第一部分是硬件平台的设计,包含了主芯片EP2C8、外设芯片(SDRAM、配置芯片和Flash)以及它们之间的互联;第二部分是定制系统需要的硬件系统,即设计处理器软核和相关外设的控制逻辑。这部分的工作是整个系统设计的基础。

整个硬件系统的核心是基于Cyclone II系列FPGA(EP2C8Q208C8)的SoPC模块。系统的结构框图如图2所示。Nios II软核处理器定义主从设备之间的接口与通信时序,通过Avalon交换式总线连接各个控制模块和多个IP核,包括SoPC Builder工具自定义生成的IP核模块。SoPC Builder中包含3种可选的软核处理器,分别是:Nios II/f(快速)——消耗FPGA资源最多,系统性能最高;Nios II/s(标准)——性能和FPGA使用量都是中等的;Nios II/e(经济)——所占FPGA资源最少,性能最低[2-3]。根据系统的需求,Nios II/f(快速)型软核处理器完全能满足本设计的需求。FPGA中还包括锁相环、CPU与外部设备的接口,PWM输出模块对电机进行调速,数据采集模块处理光电编码器的测量数据,EPCS4用来上电时对FPGA进行配置,调试程序的JTAG_UART通信模块,此外,电源管理模块为电机、光电编码器和FPGA提供工作所需电源电压。

图2 测量系统的结构框图

在NiosII处理器电机控制端口,当out_port_from_the_motor=00时,电机正转,小球下降;当 out_port_from_the_motor=01时,电机反转,小球上升。在FPGA电路和电机驱动放大电路之间加光电耦合器 (TLP521)以实现电气隔离,可以提高系统的抗干扰性。L298片内有两个相同的模块,每个模块有3个控制输入端:一个使能端和两个方向控制端。如图2所示,NiosII产生的PWM信号经过光电耦合器连接到L298芯片的使能端,NiosII提供的两路PWM信号提供步进电机调速控制,从而小球做匀速直线运动来测量位移。通过将NiosII的并行输入输出模块(PIO)输出的信号送入L298的方向控制端,来控制步进电机的转向和制动状态。本系统还使用了光电编码器对电机进行速度检测并反馈给NiosII,实现完整的闭环控制系统。

光电编码器三相信号(A、B、Z)经整形电路后的脉冲信号送入FPGA的数据采集模块[4],数据采集模块主要是为时间和位移做准备,这里主要是测量相邻的时间脉冲和位移脉冲上升沿之间的个数,方便NiosII处理器计算时间和位移以及进行时间和位移数值转换。

片上存储器采用EP2C8 FPGA提供165 888 bit的RAM 内存,共计 36个 M4K RAM blocks,8 256个 LEs。

定时器Timer用来提供系统所需的时钟节拍。

PIO通过2 bit的二进制信号来检测操作面板的按键触发信号、判断电机控制器的参数并进行小球位置检测。

通用异步收发器(UART)提供了人机交互接口,与上位进行通信以及程序调试。这里,USB接口可视作一个虚拟的通用异步收发器来访问。系统运行中,闪存存储配置文件,而SDRAM存储各类数据。

设计软硬件接口的任务是完成驱动程序的编写工作,驱动程序是连接硬件与软件的桥梁。此外,软硬件接口的另一个重要工作是进行硬件初始化,处理器从复位状态进入操作系统能够运行的状态,也就是把控制权交给操作系统或应用程序之前,硬件和驱动必须做的一些工作。利用Altium Designer工具完成电路板的PCB版图设计。

3 处理器的定制与系统的工作原理

NiosII处理器采用 32 bit指令﹑32 bit数据和地址﹑32 bit通用寄存器和32个外部中断源[5],能在高性能的Stratix或低成本的Cyclone芯片上实现,配置最合适的处理器、选择合适的外设和接口组合。

本系统是以NiosII处理器作为实现控制的中央处理器,实验证明,NiosII软核处理器主频可以平稳运行在120 MHz,速度相当快。设置总线时钟频率为50 MHz。

利用SoPC Builder开发工具创建用户定制的NiosII处理器,其地址映射和中断优先级分配如图3所示。图4所示的本系统定制的NiosII处理器还加入了CPU核、EPCS、SDRAM、TIMER、PIO、数码管和 UART 等外围接口电路,以实现NiosII与外设的通信。

SoPC Builder将定制的处理器转化为Verilog HDL等具体的设计文件,自动生成针对硬件环境的C语言和汇编语言的头文件以及函数库。

在Quartus II中实现重力加速度测量系统用户定制的NiosII处理器模块如图4所示。主要端口包括时钟信号 clk、复位信号 reset_n、中断信号 int_port_to_the_INT、光电编码器采集数据in_port_to_the_data_out[31..0]、电机控制 信 out_port_from_the_motor[1..0]、LCD显 示 coe_seg_from_the_seg、UART发送和接收端口。由于 NiosII是在FPGA片内实现的,因此它既可以通过引脚连到外部与其他设备相连接,也可以直接连到片内的其他模块上。同样,FPGA片内未被使用的资源仍然可以被配置到其他模块使用,从而实现系统的集成。

电路板上只有一个频率为50 MHz的外部晶振,显然无法满足设计所需的各种频率要求。于是采用FPGA内嵌的模拟锁相环 PLL(Phase Lock Loop)进行分频与倍频,以满足系统设计中各个模块不同频率的要求。由锁相环模块提供CPU的时钟和SDRAM的时钟(两个时钟大小均为 50 MHz,相位相差 63°),以及光电编码器数据采集模块所需的高频时钟200 MHz。当产生测量时间按键中断时,小球做自由落体运动,下落的过程中遮挡光电门对管时,产生一系列脉冲,以高频200 MHz为基准频率测出相邻脉冲上升沿之间的时间就是要测量的时间。当产生测量距离按键中断时,小球再次通过光电门对管,遮挡光电门时会产生一系列脉冲,通过测量模块得到相邻两个脉冲上升沿之间编码器的转数N,要测的位移S=N×c,其中c为光电编码器转轴的周长。

4 系统软件设计

为了操作这些片上硬件,SoPC Builder提供了一个编写软件代码的 NiosII集成开发环境(IDE)[6],软件编程采用C语言和VHDL语言完成,在NiosII IDE下完成所有软件开发任务,包括编辑、编译、调试程序和下载[7]。在进行软件设计时,根据NiosII处理器系统的需求自动生成开发向导,避免手动设置带来的不便,节省时间,缩短开发周期[8]。基于SoPC平台NiosII处理器的整个软件系统由实现不同软件功能的模块组成,包括:主程序模块、串口中断子程序、光电编码测量子程序、电机驱动程序、数据处理子程序和上位机显示程序。

在本测量系统中,NiosII程序实现如下3个任务。(1)系统设置了多个按键,当按下按键时,由 NiosII软核识别键值完成不同的中断操作。(2)通过UART模块得到上位机发出的控制任务及控制参数,接收与步进电机同轴的光电编码器的反馈信号,经CPU计算和处理后得到纠正后的PWM控制参数并传达给自定制的PWM模块,由PWM模块输出相应的PWM信号控制直流电机的正反转状态,从而实现小球做匀速直线运动来精确测量两点间的位移。(3)进行数据运算和进制转换,中间过程要进行乘法除法运算,测量的时间换算成秒为单位,位移换算成米为单位。

图5是测量系统的主程序流程图。系统初始化时,使用函数 IOWR (SIGNAL_CAP_0_BASE,0,1) 将采集模块全局信号复位,接着判断串口是否有数据,处理串口数据,判断按键值,使用 KEY->INTERRUPT_MASK=1注册中断, 使用 alt_irq_register(KEY_IRQ,NULL,ISR_key)来建立用户中断程序,对各个按键中断响应进入中断服务 程 序 sig_cap_irq_proc_tests、sig_cap_irq_proc_testt、sig_cap_irq_proc_ up、sig_cap_irq_proc_down、sig_cap_irq_proc_stop。当完成时间/位移测量后,产生一个硬件中断,将标志flag_INT置1。当主循环程序判断flag_INT为1时,就可以从外扩的SDRAM中将时间/位移数据读入SDRAM中,其中包括用户自定义指令和硬件模块实现的数据运算和进制转换部分。最后主要使用IOWR_ALTERA_AVALON_PIO_DATA (SEG_SEL_BASE,0xff)、IOWR_ALTERA_AVALON_PIO_DATA (SEG_SEL_BASE,bittab[cnt]) 和IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_BASE,0)3 个函数来显示测量结果。

图5 主程序流程图

本文基于NiosII设计了自由落体分析仪,提出了一种软硬件综合的解决方案,同时完成了底层的硬件系统和相应的软件的实现。由于SoPC技术先天具有巨大的灵活性,因此在本文设计的基础上可以配合NiosII软核的强大功能进行功能扩展和系统升级,以提高系统的性能,拓展应用领域。不仅如此,采用IP核复用技术基于NiosII进行嵌入式系统设计可以大大缩短硬件开发周期。

[1]方茁,彭澄廉,陈泽文.基于 NIOS的 SoPC的设计[J].计算机工程与设计,2004,25(4):504-507.

[2]李羚梅,吴志勇,崔明.基于 NIOSⅡ处理器的B码解调设计[J].计算机工程,2010,36(9):263-265.

[3]李兰英.SoPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[4]马永杰,董秀娟,王轲.基于FPGA的高精度光电编码器接口电路的设计[J].西北师范大学学报,2011,47(4):43-47.

[5]任爱峰,初秀琴,常存,等.基于 FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2005.

[6]谢东辉,齐伟民.基于 NiosⅡ片上可编程系统(SOPC)实现的雷达监控系统 [J].中国科学院研究生院学报,2010,27(1):63-69.

[7]杨光辉,邬江兴.基于FPGA中 IP核的 IRL系统设计方法[J].计算机应用研究,2008,25(1):190-194.

[8]刘明贵,梁昊.基于SoPC的低应变反射波检测系统[J].电子技术应用,2010,36(7):87-89.