TM32F103ZET6最小系统设计

Cortex_M3内核主要是应用于低成本、低功耗的场合,并且具有极高的运算能力和极强的中断响应能力。Cortex-M3处理器采用纯Thumb2指令的执行方式,使得这个具有32位高性能的ARM内核能够实现8位和16位的代码存储密度。ARM Cortex-M3处理器是使用最少门数的ARM CPU,核心门数只有33K,在包含了必要的外设之后的门数也只有60K,使得封装更为小型,成本更加低廉。Cortex-M3采用了ARM V7哈佛架构,具有带分支预测的3级流水线,中断延迟最大只有12个时钟周期,在末尾连锁的时候只需要6个时钟周期。同时具有1.25DMIPS/MHZ的性能和0.19mW/MHZ的功耗。STM32F103ZET6该芯片具有Cortex_M3内核、144管脚、64KB SRAM、512 KB FLASH、2个基本定时器、4个通用定时器、2个高级定时器、3个SPI、2个IIC、5个串口、1个USB、1个CAN、3个12位ADC、1个12位DAC、1个SDIO接口、1个FSMC接口以及112个通用IO口。

一、原理图设计

一个最小的核心板原理图分为电源供电,外部时钟,启动方式,复位,下载五部分。

1.电源供电

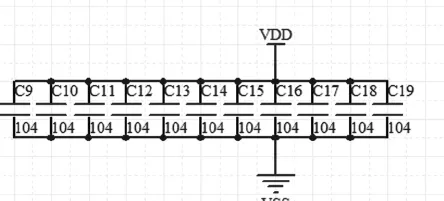

电源供电部分为主要模拟部分供电与数字部分供电,11个数字部分需要添加11个去耦电容(见图1.1)。去耦电容的作用举个简单的例子。你可以把总电源看作水库,我们大楼内的家家户户都需要供水,水不是直接来自于水库,那样距离太远了,等水过来,我们已经渴的不行了。实际水是来自于大楼顶上的水塔,水塔其实是一个暂存的作用。同样的道理如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,而器件VCC到总电源有一段距离,即便距离不长,在频率很高的情况下,阻抗Z=i*wL+R,线路的电感影响也会非常大,会导致器件在需要电流的时候,不能被及时供给。去耦电容可以弥补此不足。这就是为什么很多电路板在高频器件VCC管脚处放置小电容的原因。

模拟电源部分的地与数字电源部分的地需要连接起来(见图1.2),连接起来方式有三种。第一种是磁珠,第二种是电感,第三种是0R电阻。比较三种方法哪种比较适合模拟地与数字地的单点接地呢?磁珠的等效电路相当于带阻限波器,只对某个频点的噪声有显着抑制作用,使用时需要预先估计噪点频率,以便选用适当型号。对于频率不确定或无法预知的情况,磁珠不合。电感体积大,杂散参数多,不稳定。0欧电阻相当于很窄的电流通路,能够有效地限制环路电流,使噪声得到抑制。电阻在所有频带上都有衰减作用(0欧电阻也有阻抗),这点比磁珠强。0欧姆电阻可以设置多个,根据实际要求选择0欧姆电阻数目,达到最优的设置要求。所以我们这里的模拟地与数字地部分我们选用2个0欧姆电阻并联的形式,根据实际选择相应的0欧姆电阻的数目。

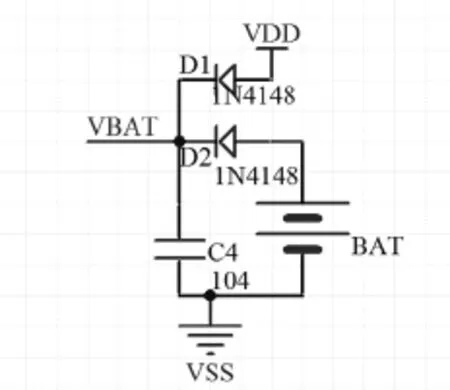

STM32F103ZET6属于低功耗产品,在主时钟关闭的情况,部分功能仍然可以保持正常(见图1.3)。但是需要装上备用电池。此处我们选用CR1220纽扣电池接上二极管的方法,在有其他外部电源的时候启用外部电源,在突然断电或者异常状况下启用备

2.外部时钟

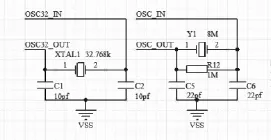

选用8M晶振并联12M反馈电阻和22pf起振电容。外部32.68KHZ的晶振并联10pf起振电容(见图1.4)。

3.启动方式

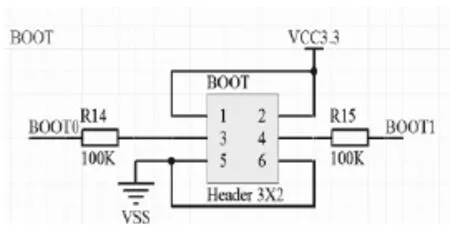

STM32F103ZET6有三种启动方式(见图1.5),如表1所示。

(1)用户闪存就是芯片内置的Flash,这种模式直接从0X08000000启动,也就是我们自己编写的代码的启动方式了.正常情况都应该用这种。

(2)SRAM就是芯片内置的RAM区,就是内存,从0X20000000启动的,也就是说在SRAM模式开始之前,你要确保SRAM里面已经有代码了,否则就是死机。

(3)系统存储器就是芯片内部一块特定的区域,芯片出厂时在这个区域预置了一段BOOTLOADER,就是通常说的ISP程序。这个区域的内容在芯片出厂后没有人能够修改或擦除,即它是一个ROM区。这种模式就是STM32复位后就执行固化在内部的BOOTLOADER程序(固化的,我们无法读写),然后等待串口数据,从而实现串口BOOTLOADER功能。这种模式不会从用户存储区启动(除非用串口控制其从0X08000000启动),所以在更新了代码之后,需要设置为其他模式(FLASH模式)。

4.复位

复位按钮设置,因为复位按钮低电平有效,因此采用下拉方式(见图1.6)。

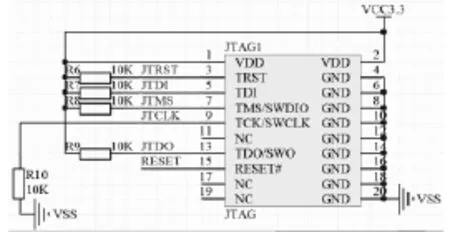

5.下载方式

JLINK V7(见图1.7)支持JTAG/SWD两种下载方式。JTAG采用五线制(见表2)。

此外还支持SWD调试方式,只用两根线就可以完成调试过程(见表3)。

二、PCB布线

1.耦合电容需要靠近相应的数字电路部分

耦合电容必须靠近数字部分,才能起到降低干扰,提供稳定电压的功能。如果远离数字部分耦合电容排除干扰的能力将大大减弱,

表1 《STM32F103ZET6最小系统设计》启动方式表

表2 《STM32F103ZET6最小系统设计》JTAG五线制定义

表3 《STM32F103ZET6最小系统设计》SWD两线制定义

图1.1 耦合电容

图1.2 模拟地与数字地

图1.3 备用电源

图1.4 晶振电路

图1.5 BOOT选择电路

图1.6 复位电路

图1.7 JLINK电路图

图2.1 导线厚度35um

图2.2 导线厚度70um

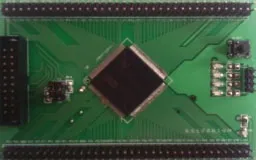

图3.1 实物图正面

图3.2 实物图反面

2.布线粗细要适当

PCB的敷铜厚度常常用盎司做单位,它与英寸和毫米的转换关系如下:

1盎司=0.0014英寸=0.0356毫米(mm)

2盎司=0.0028英寸=0.0712毫米(mm)

GB-T_4588.3-2002关于单面板的热耗规定如下:

对于以铜为导线材料、标称厚度为1.6mm~3.2mm(0.063in~0.125in)的单面印制板,不同宽度和常用厚度的导线温升与电流之间的关系(忽略如镍、金或锡附加镀层的影响),如图2.1、2.2所示。

根据上表我们有了一个直观的认识,但是作为日常布线仍然不够。我们接着来看看MIL-S TD-275(美国军方标准)提到了温度、电流、与导线截面的关系。

相关的计算公式:I=KT^(0.44)A^(0.725)W=A/d

I=最大的电流,单位为:A

K=降额常数:导线在内层时取值为:0.024;导线在外层时取值为0.048.

T=最大温升,单位为:℃

A=导线截面积:单位为:mil^2

W为线宽

d导线厚度(即为覆铜厚度)算出的线宽即为布线的宽度。根据此可以计算相应的线宽,再加上25%的余量就能满足大部分的设计要求。

3.覆铜与导线的间距适当

STM32F103ZET6具有144个管脚,管脚最近的距离仅为9mil,如果覆铜距离过近,可能造成焊接过程管脚与覆铜短路的情况。所以在覆铜的时候需要格外加大间距。我个人设置为30mil。

4.模拟部分与数字部分分区布置

我们选用的系统属于低频电路,模拟电路部分与数字部分需要分开布置,同时采取单点接地的方式,避免数字电路部分干扰模拟部分,从而影响芯片内部模拟电路部分的正常工作。

至此我们完成了STM32F103ZET6的最小系统的设计(见图3.1,图3.2)。这套最小系统可以帮助了解和学习STM32,深入了解Cortex_M3内核。同时这套最小系统可以帮助我们进行开发项目前的验证测试阶段的工作,从而设计和开发更加复杂的项目。

[1]中华人民共和国国家质量监督检验检疫总局.印制板的设计和使用[Z].2002-11-25.

[2]DEPARTMENT OF DEFENSE Washington.DC 20301.MIL_STD_275E.31 December 1984.

[3]北京三恒星科技公司.Altuim Designer 6设计教程[M].2007年2月第1次印刷.北京:电子工业出版社,2007,2:293-318.