一种应用于线列TDI型红外焦平面的数字化读出电路

尹士畅,喻松林,于 艳

(华北光电技术研究所,北京100015)

1 引言

近年来,为了提高红外焦平面阵列输出信号的信噪比,以及线列型焦平面阵列的扫描速度,人们越来越倾向于在读出电路的选择上采用时间延迟积分TDI(time delay integration)的结构[1-3]。同时逐次逼近(successive approximation register,SAR)型 ADC也由于其转换速率快、面积小、功耗低在许多便携式以及低功耗场合中应用越来越广泛。本文提出了一种将SAR型ADC应用于线列TDI型红外焦平面的电路设计,并通过电路仿真得到了很好的结果。

2 TDI结构和逐次逼近型ADC的简介

2.1 TDI

TDI的结构如图1所示,TDI结构需要一行n个红外探测器像元,其中n表征TDI的级数。在线列型红外焦平面阵列在扫描的过程中,该n个红外探测器像元在不同的时刻探测同一位置,最后将n个探测器像元的信号累加[4-6]。我们总是假定在不同的时间内,各个像元上的噪声都是非相关噪声,那么根据多相关采样原理,经过n个像元的数据累加之后,总信号的信噪比是单个像元信噪比的倍,从而提高了信号的信噪比。虽然是多个像元的数据的累加,但是通过在TDI结构中插入存储单元(可以是模拟存储或者是数字存储),便构成了流水线结构,使得数据的输出速率很高,整个系统的扫描频率也可以提高。

图1 TDI结构图

2.2 SAR 型ADC

SAR型ADC是众多ADC结构中的一种,该结构的ADC最大的特点就是面积小、低功耗并且转换速率相对比较高。该结构通过特定的搜索算法来逐步确定转换后的数字量的各位的权重值,从而完成一次模数转换。最基本的逐次逼近型的结构如图2所示。

图2 SAR型ADC结构图

该结构由一个比较器、一个采样保持器和一个DAC组成。在图2的结构中DAC通常选择用电容阵列来实现。但是常规的电容阵列较大,造成面积和功耗相对较高,难以很好地集成在红外焦平面读出电路内。同时考虑电容匹配受到工艺的限制,该类型的ADC位数增加时引起的非线性等因素,都限制了常规的SAR型ADC在红外焦平面读出电路中的使用。

3 两步式ADC的TDI结构

3.1 两步式权重搜索算法

两步式逐次逼近[7]的原理如图3所示,与基本的逐次逼近型的ADC不同,该结构中每个电容的信号输入端由原来的两个输入增加到四个输入0 V

图3 两部式逐次逼近ADC原理

在采样阶段,首先SW1导通,通过采样电容进行电压采样。在采样完成后,打开SW1,闭合SW0,对于C6参考电压选择VREFP2,其余电容参考电压选择为VGND,如果比较器输出为1,则获得D11的权重值为1,否则为0。依照此方法按照从高到低的顺序依次获得高6位的权重值。在获得了高6位的数据之后,按照从高位到低位的次序依次获得各数据位的权重,具体方法为:如果D11为1,则参考电压选择VREFP1,如果D11为0,则参考电压选择为 VREFP1,此时比较器的输出值即为D5的权重值。同时在D11为1的情况下,如果D5为1,则C6的输入接所选择的参考电压为VREFP1,如果D5为0,则将该电容接VGND;相反,在D11为0的情况下,如果D5为1,则C6的输入接所选择的参考电压为VREFN1,如果D5为0,则将该电容接VGND。按照此算法,便可以依次搜索低几位的权重值直到得出数字转换值。

该种结构的最大的特点就是通过电容的复用极大的减小了电容的面积,从而降低了SAR型ADC的动态功耗[8],使得该结构可以很好的应用于红外焦平面的数字化电路中。分析SAR型ADC的功耗主要在于电容阵列的动态功耗和比较器的功耗。其中电容阵列的最大功耗为:

经过电容复用的电容阵列,单位电容C选为50 fF,SMIC18工艺下电源电压 VDD选为1.8 V,在转换速率 f为500 kHz的情况下,电容最大功耗PCmax为0.7μW,电容功耗只相当于文献[9]中的常规搜索方法的几百分之一,极大地降低了电容阵列的动态功耗。相比较文献[7]中的设计,由于只设计了12位的ADC,因此可以保证参考源的精度要求,从而减少了校准电路的开销。

3.2 SAR型ADC构成的TDI结构

传统的TDI结构是通过在模拟域将像元信号的信息相叠加的方法,提高整个焦平面阵列的性噪比。本文以1024×32元的TDI为例,采用的结构如图4所示,TDI的处理部分在数字域完成。考虑到32级TDI可以提高 4倍的信噪比,故设计中采用12 bit的SAR型ADC,该ADC依次对单个显示像元所对应的32个物理像元进行模数转换,然后将各个像元的值在数字域进行叠加,叠加结果以16 bit输出。该结构不但实现了长波器件在较短的积分时间内完成模数转换的功能,同时降低了由于ADC在转换过程中带来的噪声的影响。相比较传统的在模拟域进行数字TDI的方法,减少了模拟域的加法器和除法器的各种误差所带来的精度和噪声方面的影响,更好地降低了整个系统的功耗的同时完成了整个系统的数字化读出。而且,由于转换时间快,转换结果在数字域存储,对于Memory部分稍加改动就可以完成长波器件的多小帧积分,对于长波器件难以实现长时间积分提供了新的思路。

图4 SAR型ADC整体结构

4 仿真结果分析

4.1 线性度分析

通过给电路加斜坡电压来仿真整个ADC系统的线性度,如图5所示为整个ADC的微分非线性,在整个16 bit的码值输出范围,ADC的DNL都可以保持在±1 LSB的范围内,从而可以很好地保持系统的单调性。

图5 ADC的微分非线性(DNL)

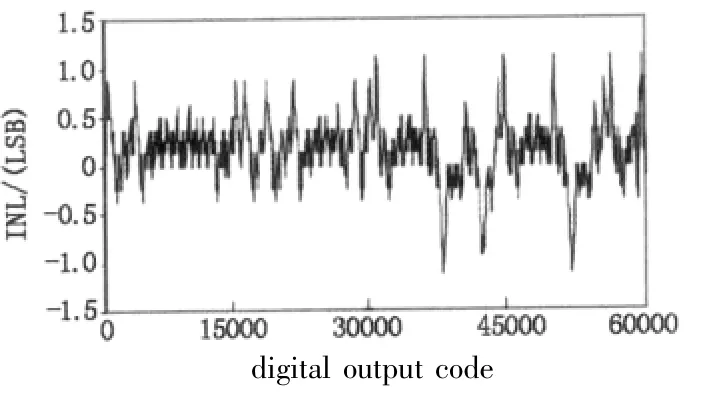

整个ADC的积分非线性(INL)如图6所示,在整个码值的输出范围内,INL都合理地控制在±1 LSB范围内。中间值处的非线性偏大,是由于电容阵列中的 mismatch引起来的,但是 SMIC 0.18μm工艺下,当电容尺寸大于10μm2时精度可以达到0.03%,从而保证在12 bit的情况下,INL值不超过±1 LSB。

图6 ADC的积分非线性(INL)

4.2 SNR 分析

通过给电路加正弦波电压信号,电压信号不包含噪声信息,只测试电路的性能。采样后的信号的频谱如图7所示,虽然单个ADC的采样率可以达到1 MHz,但是对于单个像元的转换速率只达到了30 K。从仿真结果可以看出,SFDR可以达到90 dB,整个读出电路最高可以达到80.2 dB的信噪比。对于长波器件而言,32μs的积分时间下器件的信噪比远远低于该电路的信噪比,所以读出电路对于长波线列型红外焦平面具有很好的应用前景。

图7 采集信号频谱

4.3 功耗分析

经过仿真后,整个电路(32个物理像元,一个显示像元)的最大功耗为230μW,其中功耗的最大来源在于比较器的功耗,由于采用了两步式SAR型结构,电容阵列的动态功耗最高值为1μW,很好地验证了之前的理论分析。从而可以看出,该种结构在功耗方面可以很好的满足红外焦平面器件低功耗的设计要求。

5 结论

通过对于两步式SAR型ADC和长波线列型红外焦平面的技术分析,以及实际上电路上模型的仿真可以看出,将两者相结合的读出电路,不但完成了长波积分器件在较短积分时间内完成数字化,而且相比较模拟读出的读出电路电路而言,提高了精度和噪声性能,相比较对于长波线列型红外焦平面数字化技术提供了一个新的思路。

[1] Liu Liping.Status and trend of the readout circuit technology for IRFPA [J].Laser & Infrared,2007,37(4):598 -600.(in Chinese)刘莉萍.红外焦平面读出电路技术与发展趋势[J].激光与红外,2007,37(4):598 -600.

[2] Liu Xiaolei,Yu Shonglin.Design analysis of ROIC for LWIR application [J].Laser & Infrared,2009,39(2):119 -122.(in Chinese)刘晓磊,喻松林.长波红外焦平面读出电路设计分析[J].激光与红外,2009,39(2):119 -122.

[3] Tang Ju,LuWengao,etal.288 ×4 IRFPA ROICwith TDI[J].Infrared Technology,2007,29(4):206 - 210.(in Chinese)唐矩,鲁文高,等.具有时间延迟积分(TDI)功能的288×4红外焦平面读出电路[J].红外技术,2007,29(4):206-210.

[4] Byunghyuk Kim,Nanyoung Yoom,et al.Novel concept of TDI readout circuit for LWIR detector[J].Infrared Detectors and Focal Plane Arrays,2000,4028(7):166-167.

[5] Zhongjian Chen,Wenggao Lu,et al.A CMOSTDI readout circuit for infrared focal plane array[C].Solid-State and Integrate-Circuit Technology,2008:1765 -1768.

[6] Zhang Yacong,Liu Dan,Lu Wengao,et al.A TDICMOS readout circuit for IRFPA with linearity improvement[C].Solid-State and Integrate-Circuit Technology,2005:598-600.

[7] M SShin,O K Kwon.14-bit two-step successive approximation ADC with calibration circuit for high-resolution CMOS imager[J].Electronics Letters,2011,47(14):790-791.

[8] Mehdi Saberi,Reza Lotfi,et al.Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs[J].Circuits and Systems,2011,56(8):1736 -1748.

[9] 8.9-Megapixel Video Image Sensor With 14-bit Column-Parallel SA-ADC[J].Electron Devices,2009,56(11):2380-2389.