基于自偏置技术的低噪声锁相环研究

曹羽欧,李章全

(1.上海交通大学微电子学院,上海 200240;2. 中芯国际集成电路制造(上海)有限公司,上海 201203)

1 引言

锁相环在集成电路中有非常广泛的应用,如时钟发生器、频率综合等。传统锁相环需要一个固定的电荷泵电流、线性的VCO增益,这些都制约了锁相环在低功耗、低电压下的设计,本文提出的自偏置锁相环采用自适应环路的方法,降低了电路对PVT的要求,同时可以获得更大范围的锁定频率。本文描述的自偏置锁相环达到从500 MHz到1500 MHz的锁定范围。测试均方抖动为3.8 ps, 峰-峰值抖动25 ps。表现出非常好的噪声性能。

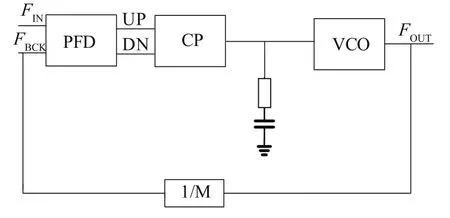

2 锁相环的基本架构

如图1,锁相环主要是由鉴频鉴相器(PFD)、电荷泵(Charge Pump)、环路低通滤波器(LPF)、压控振荡器(VCO)和环路除法器(Loop Divider)组成。由于电荷泵的充放电需要一个稳定精准的电流,锁相环一般还需要一个较高精度的电流源。其中FOUT是输出频率,FIN是输入频率,M是环路除法器的值,当确定输入频率FIN时,输出频率为输入频率与环路除法器M的取值的乘积,公式为FOUT=FIN×M。

图1 锁相环基本结构

3 锁相环的线性模型与环路稳定性

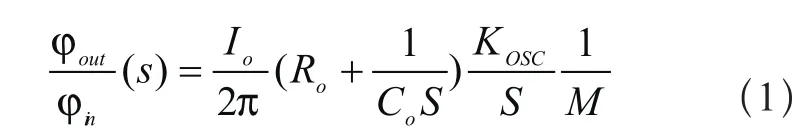

锁相环的线性模型如图2,将锁相环反馈通路在PFD与环路除法器之间打开,可以得到锁相环的开环传输函数:

其中IP是电荷泵的电流,RP、CP是环路滤波器的电阻、电容值KOSC是压控振荡器的增益。给出闭环传输函数:

根据二阶控制系统函数,得到带宽与阻尼系数表达式如下:

ωN、ξ不仅受到RP、CP、IP、KOSC(PVT)的影响,同时受到环路除法器的取值M的影响,这些值的变化都会影响到锁相环的稳定性和抖动性能。

图2 锁相环线性模型

4 自偏置锁相环的设计架构图

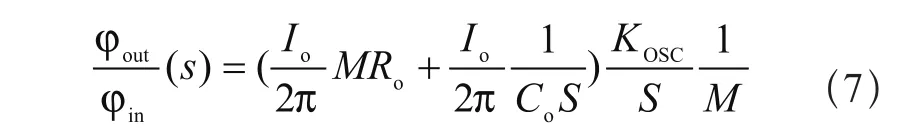

与传统锁相环一样,ωN/ωREF<1/1 0且damping>0.707是保证锁相环稳定性的基础。本文采用了对称性负载型VCO结构,如图4。为了消除环路除法器取值对稳定性的影响,我们利用VCO的偏置电流作为电荷泵的电流源,同时将VCO的偏置电流作为低通滤波器的电流源,图3中的两个电荷泵分别给电容CP和电阻充电。其中对电容CP充电的电荷泵需要引入M作为因子,但是对电阻充电的电荷泵则不需要,给出电荷泵充电电流:

根据图3可计算自偏置锁相环的开环传输函数如下:

闭环传输函数:

图3 自偏置锁相环的架构图

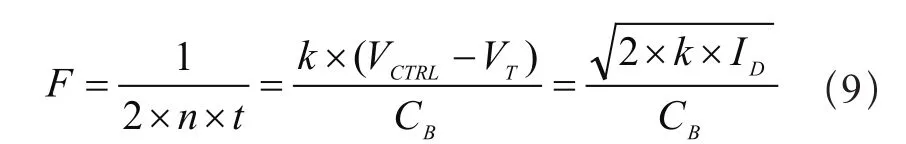

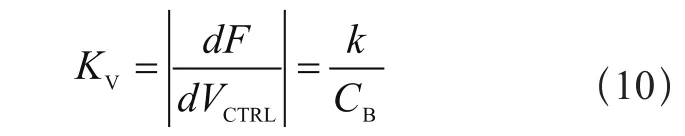

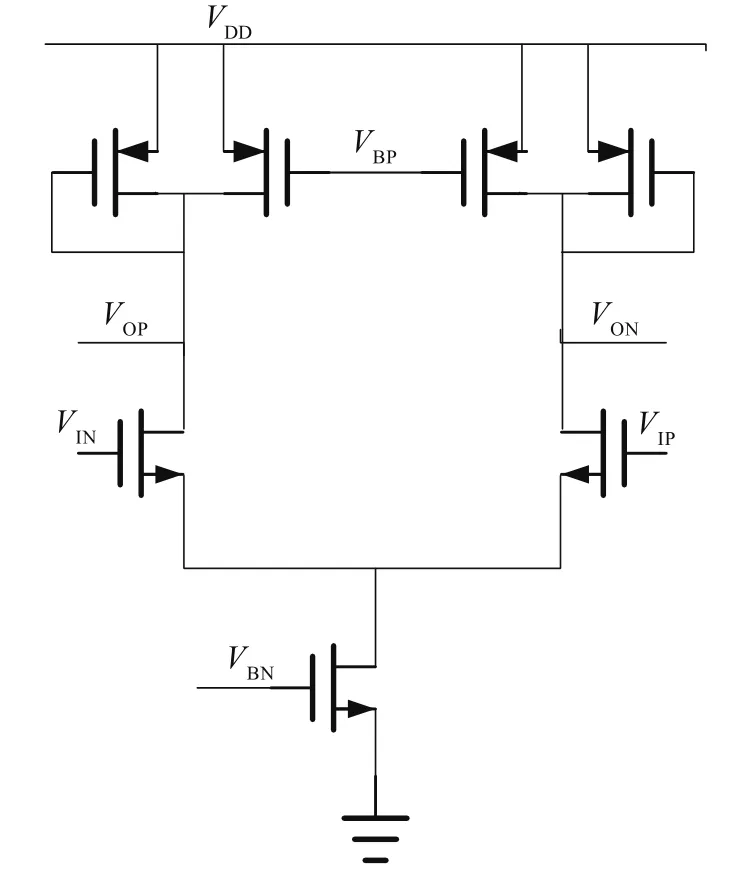

图4为压控振荡器的基本延迟单元,对称性负载型VCO结构,根据这种结构,得到输出频率的公式:

F是输出频率,n是VCO的级数,t是每级延迟单元的延迟时间,k是工艺参数,ID是每级延迟单元消耗的电流,VT是阈值电压,VCTRL是控制电压,CB是VCO寄生电容的总和。对输出频率求导得到VCO的增益:

将VCO增益表达式与输出频率表达式代入闭环传输函数得到ωN/ωREF、ξ的公式如下:

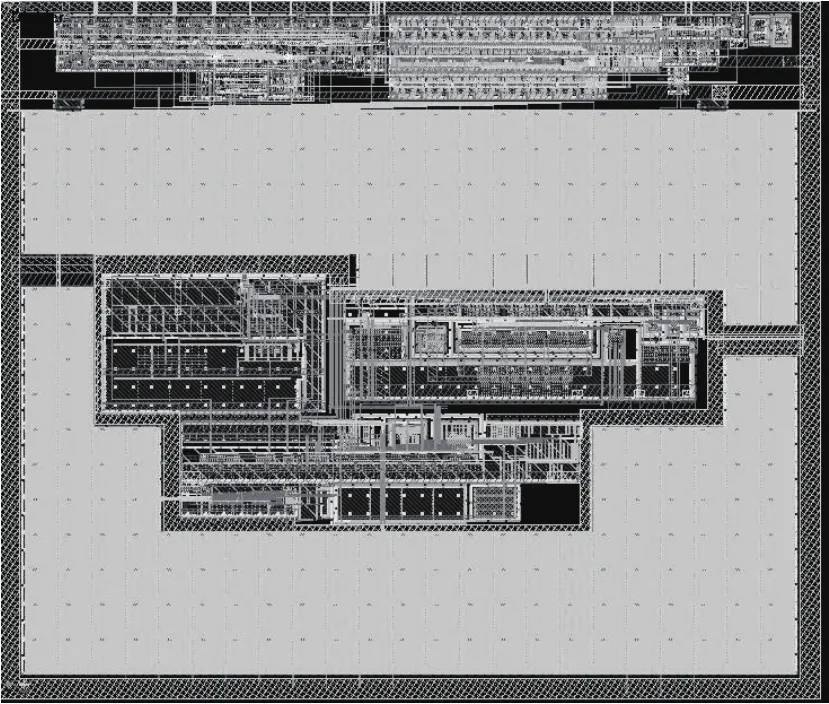

由ωN/ωREF、ξ的表达式看出,它们的取值只和CP与CB的比值相关,与RP、CP、IP、KOSC(PVT)和M取值相关的量都可以用相应的参数抵消。这样,锁相环的ωN/ωREF、ξ就可以维持一个常数,不再有稳定性随电压、温度、工艺参数变化的问题,图5是锁相环的整体版图布局,图6是在1.5 GHz频率下测试得出的抖动。

图4 压控振荡器的基本延迟单元

5 结论

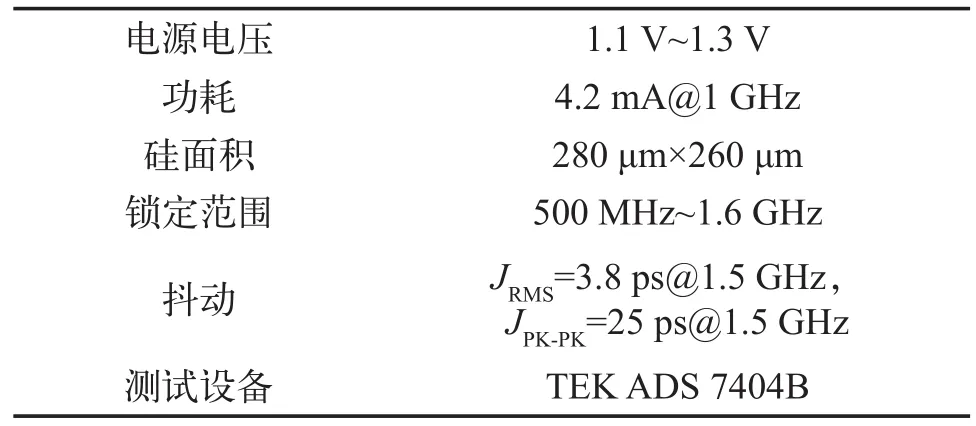

本文给出了在低电压、深亚微米工艺、较大频率范围实现低抖动以及好的相位噪声锁相环的一个实例,利用自偏置的理论,有效地扩大了压控振荡器的等效线性范围,通过环路内部各模块间的偏置电流相互作用,使环路特性不依赖于电压、温度以及工艺参数的变化,使得整个环路更加稳定。经过后提取参数仿真,电路可以工作在500 MHz到1.6 GHz。芯片面积为280 μm×260 μm。表1是锁相环性能一览表。

图5 锁相环版图

表1 锁相环性能一览表

[1] Keliu Shu. CMOS PLL Synthesizers: Analysis and Design[M]. 北京:科学出版社,2007.

[2] Behzad Razavi著,陈贵灿等译. Design of analog CMOS integrated[M].西安:西安交通大学出版社,2003.

[3] John G Maneatis. Low-jitter process-independent DLL and PLL Based on Self-Biased Techniques[J]. IEEE J. Solid-State Circuits, 1996,31(11).

[4] John G Maneatis. Self-Biased High-Bandwidth Low-jitter 1-to-4096 Multiplier Clock Generator PLL[J]. IEEE J Solid-State Circuit,2003,38(11).