基于ATF54143平衡式低噪声放大器的设计

尹治强,谢扩军

(电子科技大学 物理电子学院,四川 成都 610054)

根据接收机噪声理论,其第一模块的噪声性能将对整个接收机的噪声指标有着决定性的影响[1]。文中基于噪声和性能的折中考虑,设计一款工作于890~960 MHz的平衡式LNA,其增益等于 18.5 dB,输入/输出 VSWR≤1.5,NF≤0.6。 ,该设计主要分为两部分:1)3 dB 90°定向耦合器,2)2个并联的高电子迁移率晶体管(E-HEMT)ATF54143[2]。 ATF54143 拥有优异的低噪声系数、放大倍数以及很少的外围器件,可以工作于 450 MHz~6 GHz。作为平衡式结构,3 dB 90°相移定向耦合器的性能是很重要,为尽量小的PCB面积,采用电容和电感制作分立定向耦合器。总之,平衡放大器有单个放大器相同的增益,但其有“故障软化模式[3]”。在制作时一定要意2个有源电路的对称性。

1 3 dB 90°相移定向耦合器

1.1 3 dB 90°相移定向耦合器原理及电路

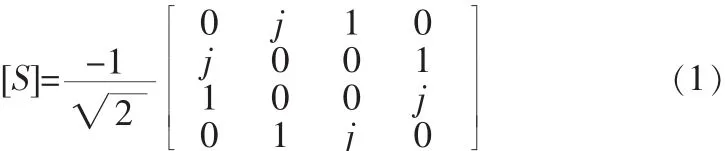

3 dB 90°定向耦合器的作用是把一路信号分成两路信号,且这两路信号之间相位相差为90°。其S参数表示为:

从式(1)可以看出,所以端口都是匹配的,从端口1输入的功率对等的分配给端口2和端口3,这两个端口之间有90°的相移,且没有功率耦合到端口4(隔离端)。电路如图1所示,计算公式[4]如式(2)(3)(4),其中 R=50 Ω:

图1 3dB90°相移定向耦合器Fig.1 3dB90°phase-shift directional coupler

1.2 ADS仿真结果

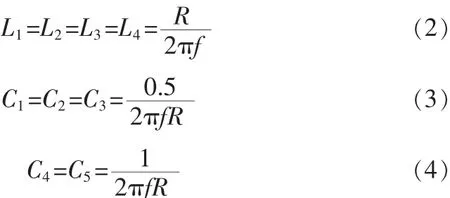

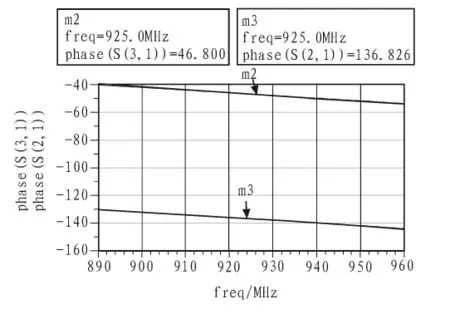

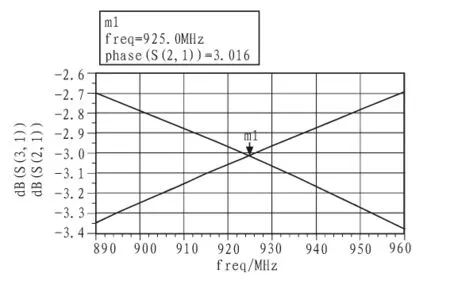

从图3可以看出,S21、S31在整个所需频带内几乎相等,达到了把信号一分为二的目的。由图2可以看出S21、S31的相位差为90°。以上2个指标很好地满足设计要求。

图 2 S21、S31相位仿真图Fig.2 S21、S31 phase simulation diagram

图 3 S21、S31幅值仿真图Fig.3 S21、S31 phase simulation diagram

2 低噪声放大器电路设计

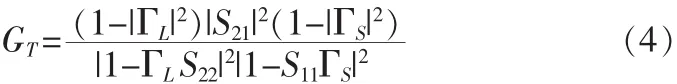

2.1 低噪声放大器的功率增益

放大器的转换功率增益GT定义为负载吸收的功率与信号源的资用功率之比:

对于低噪声放大器,首先考虑的是最小噪声系数,故在匹配时必须满足输出端负载共轭匹配,输入端满足最佳源阻抗匹配[5],以达到最小噪声的目的。 即 ΓL=,Γs=得出:

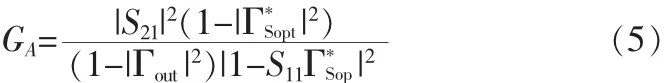

2.2 稳定性分析

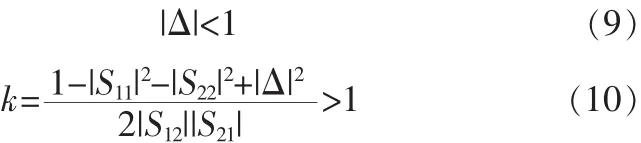

放大器电路工作的首要条件是在其工作频段内保持绝对稳定,否则将导致电路的震荡,必须满足:

其中Δ=S11S22-S12S21,最后得出绝对稳定的条件为

2.3 噪声分析

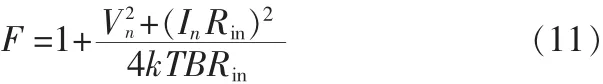

噪声系数(F)定义为输入端口的信号与噪声比与输出端口信号与噪声比之比。如果把放大器电路看做一个二端口网络,则噪声系数写作如下的表达形式:

Vn为二端口网络的噪声电压源,In为噪声电流源,Rin为二端口网络的输入阻抗。k为玻尔兹曼常数,T为绝对温度,B为测量系统的噪声带宽。为了计算最佳源阻抗Zopt,通过一系列变换我们的得到表达式[6]:

rn=为归一化噪声电阻,其值的大小代表噪声变化的灵敏度[6]。 从(13)可以看出当 ys=ySopt时,F=Fmin。

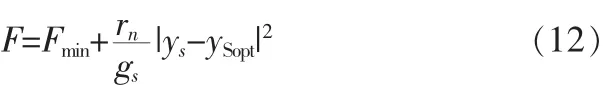

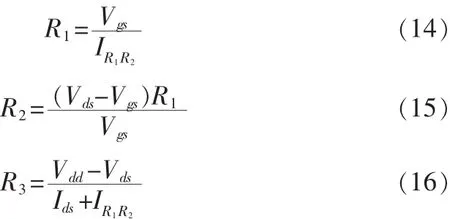

2.4 偏置电路设计

射频放大电路不可或缺的电路单元是有源或无源偏置网络,偏置网络的作用是在特定的工作条件下位有缘器件提供合适的静态工作点,并抑制晶体管参数的离散型以及温度变化的影响从而保持恒定的工作特性。参考ATF54143 datesheet,偏置电路设计为 Vdd=5 V,Vds=3 V,Ids=40 mA,Vgs=0.60 V。偏置网络采用分压拓扑结构,计算公式如下:

其中IR1R2是流过R1和R2的电流,Ids为晶体管的静态偏置电流,Vdd为电源电压,Vds为晶体管的漏源电压,

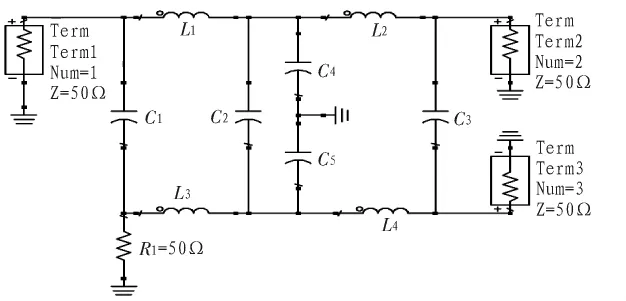

2.5 电路设计

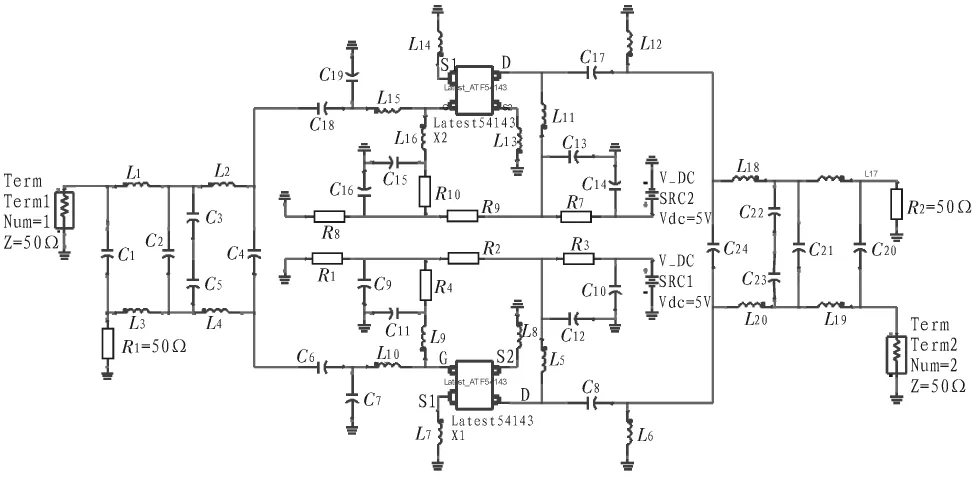

为了获得偏置电路所规定的静态工作点,假定IR1R2=1 mA,根据式(14),(15),(16),计算出 R1=500 Ω,R2=2 500 Ω,R3=48Ω。其偏置电路如图4所示,在ATF54143的源极串接一个小电感,可以使ATF54143在工作频带内达到稳定,以及使最佳源阻抗与输入阻抗尽量接近,但此电感会恶化放大器的噪声系数和增益,所以就必须在噪声系数,稳定性和增益之间折中。由于是LNA设计,首先满足低噪声系数,根据式(5),(13)可知,在匹配时需遵守输入端最佳源阻抗匹配和输出端负载共轭匹配。其最终电路和仿真结果如图4~8所示。

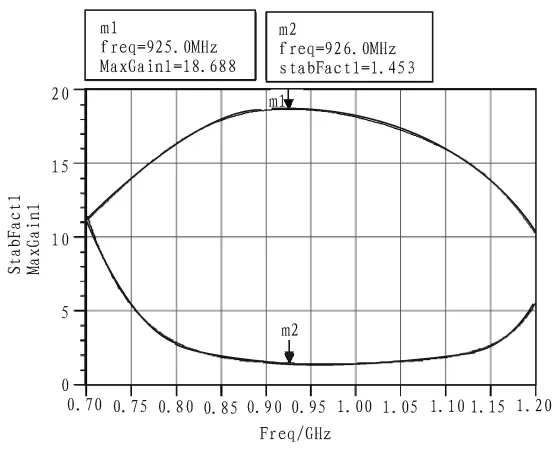

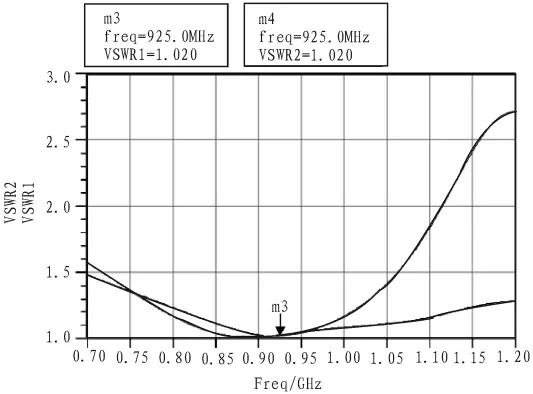

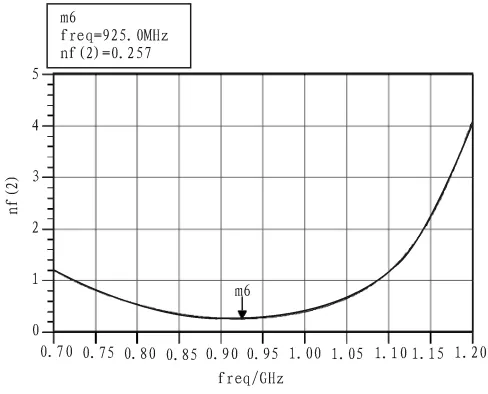

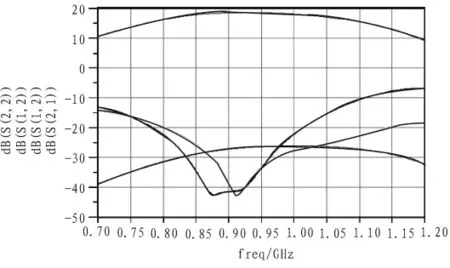

从图6~8可知此设计满足以下指标:在频率为890~960 MHz,偏置在 Vdd=3 V,Vgs=3 V,Ids=40 mA 时。 增益 Ga=18.5±0.5 dB,输入 输出 VSWR≤1.5,NF≤0.6 dB。 |S12|≤25 dB。

3 结束语

文中针对低噪声放大器的电气指标,对LNA的增益,噪声系数,驻波比稳定性及偏置点进行了设计并用ADS进行仿真。采平衡式结构使指标达到要求,为后面的制板和调试提供了理论支持。

图4 平衡式LNA电路图Fig.4 Balanced LNA circuit diagram

图5 增益和稳定系数仿真结果Fig.5 Gain and stability figure simulation

图6 输入/输出驻波比Fig.6 Input/output VSWRdiagram

图7 噪声系数仿真结果Fig.7 Noise figure simulation diagram

图8 S参数Fig.8 S Parameter

[1]Gilmore R,Bessor L.Practical RF circuit design for modern wireless systems volumeⅡ:Active Circuits and Systems[M].Beijing:Publishing House of Electronics Industry,2006.

[2]Agilent.ATF-54143 low noise enhancement mode pseudomorphic HEMTin a surface[M].Mount Plastic Package Date Sheet,2005.

[3]李缉熙,著.射频电路工程设计[M].鲍景富,唐宗熙,张彪,译.北京:电子工业出版社,2011.

[4]Sayre CW无线通信电路设计分析与仿真 [M].李正权,燕峰,译.北京:电子工业出版社,2010.

[5]Ludwig R,Bretchko P.射频电路设计-理论与应用[M].张肇仪,徐承和,译.北京:电子工业出版社,2002.

[6]Pozar D M.微波工程[M].周乐柱,吴德明,译.北京:电子工业出版社,2006.