基于可编程逻辑器件的弹载存储测试仪

王永芳,范锦彪,王 燕

(1.中北大学电子测试技术国家重点实验室,山西 太原 030051;2.仪器科学与动态测试教育部重点实验室,山西 太原 030051)

0 引言

弹载存储测试是在被测装置体内置微型存储测试仪,对被测装置无影响或影响在允许范围的条件下,现场实时完成信息采集与存储,事后回收测试,由计算机处理和再现被测信息的一种动态测试技术[1]。

高性能火炮发射时的高膛压、高初速使记录仪中电路模块的抗冲击能力成为测试能否成功的关键,而惯性短时飞行的特点要求信号采样频率高,记录时间短。虽然各种测试装置经过处理后均能满足抗高过载的要求,但是因为单片机容易跑飞[2],很难实现对被测信号的高速采样与存储;专用集成芯片ASIC功能固定,需添加电路模块,进而会造成硬件体积偏大,增大整个系统的体积[3]。为此,本文提出了基于CPLD的可编程弹载姿态存储测试仪。

1 基于单片机的存储测试仪与CPLD

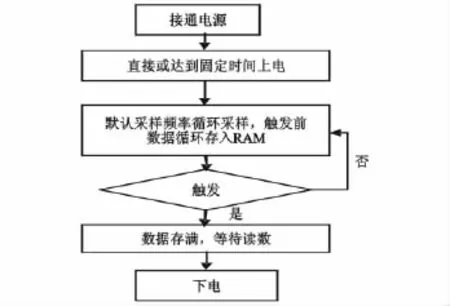

测试仪的区别主要在于主控芯片实现上的不同,主控芯片的功能是对整个电路的电源管理及电路各个模块的时序控制和与计算机通信模块。主控芯片目前主要有单片机、ASIC和CPLD。但本实验室自主研发的专用集成芯片HB0202,开发周期长,成本高,功能固定,不能更改,应用时经常需要额外增加电路部分,会增加系统体积,并且由于国内制作工艺的问题,有时会出现功能不稳定的情况。基于单片机的存储测试仪的软件流程图如图1所示。

图1 单片机存储测试仪软件流程图Fig.1 Software flow chart of MCU memory tester

单片机作用在有较强电磁干扰或恶劣的环境下,虽然在设计时可能针对特定环境采取了一些保护措施,诸如外壳屏蔽、电磁隔离等方法,但还是较难彻底解决程序运行中可能产生的跑飞现象,达不到要求。并且,单片机因为外设所限,一般几个到十几个脉冲输出口,往往需要多片单片机来实现。

单片机是执行代码的器件,代码只能逐句运行,限制其最大采样频率的“瓶颈”在于写数据到FLASH中的速度,在数据转换、传输和写入的采样过程中,写入占据了大部分的采样时间。

目前的存储测试仪主要为单次性单变采样,功能固定,难以扩展,不能适应多条件的测试要求。CPLD芯片具有集成度高、速度快、可自定义其功能及其可重复编程和反复擦写等优点[4]。并且弹载存储测试在不同条件下,尤其是在研发阶段需要测试装置在不同采样频率下的数据。而CPLD芯片为复杂可编程逻辑器件,集成度高,可反复擦写上千次,使用灵活。CPLD是逻辑阵列,I/O口均可以作为脉冲输出口,里面有很多基本的逻辑单元可以方便地实现计数、分频等功能,且芯片性能稳定,具有很高的抗冲击性能,并且与冲击方向无关[5]。同时CPLD管脚之间的延迟时间为纳秒级,且内部程序为并行执行,相对于程序顺序执行的单片机来说,在处理速度上有绝对的优势,可处理高达几十兆赫兹的采样信号。因此,CPLD芯片应用于弹载存储测试具有明显的优势。

2 基于CPLD的存储测试仪

本文提出的弹载存储测试仪增加了上电前的编程设计,通过计算机发送编程指令到装置,编程软件为Visual Basic6.0,界面如图2所示。测试仪可以根据实际情况设定信号采样频率和存储器容量,同时增加了是否防误上电及负延迟时间选择,还可根据实际情况设置默认值,通过设计CPLD芯片的逻辑设定常用的值为默认值,省去每次测试编程的步骤。

图2 测试仪编程界面Fig.2 Programming interface of the test

本文实现的CPLD存储测试仪可以实现高达200kHz的采样频率,同时还具有防误上电、采样频率可选、负延迟容量可选的功能,整体流程图如图3所示。

2.1 防误上电原理

CPLD的庞大的逻辑阵列可以轻松地实现计数器和触发器,可以通过编程设定上电延迟时间,外部一上电触发计数器根据外部提供的时钟信号开始计时,若上电持续时间达到设定时间则完成上电操作,否则系统仍然处于休眠状态。本测试仪针对不同的实验环境,防误上电时间设计了5种:2.1s、4.2s、8.4s、16.77s、33.55s。

图3 CPLD存储测试仪软件流程图Fig.3 Software flow chart of CPLD memory tester

2.2 采样频率选择原理

测试仪的AD转换芯片采用的是Analog Devices公司的芯片AD7472,转换精度为12bit,信噪比高,转换时间为880ns,处理能力为1.5MSPS,AD7472在CONVST的时钟的下降沿开始转换,因此AD的转换频率是由CONVST决定的。而CPLD内部的程序都是并行运行的,运行时间为纳秒级,因此可以轻松实现高速率采样。只要通过CPLD编程设定内部计数器和触发器的触发条件即可将提供的时钟信号进行分频得到相应频率的CONVST信号。因被测炮弹在空中飞行的时间为十几秒,故测试仪根据精度的不同信号采样频率有三种:50kHz、100kHz和200kHz。

2.3 负延迟容量选择原理

测试仪的存储总容量512K×12bit,存储器的存储数据的地址信号是由CPLD产生的,因此若要实现不同的负延迟容量只要改变内部程序中的触发后产生的地址信号个数即可。测试仪上电开始采样后,存储器将采样数据循环存入存储器中,地址信号随着数据的存入依次加1,当触发信号到来时,测试电路触发,进入负延迟工作状态,即计数器计数达到设定个数后停止采样,最后一位地址信号存入地址计数器,等待数据读出,随后计算机读出测试数据,地址信号依次加1,当计算机读完规定长度的数据后,地址计数器又回到凝固态。根据有效数据在前或在后,信号的采样策略分为两种:一种负延迟为128K×12bit(有效数据在后),一种为负延迟为384K×12bit(有效数据在前)。

3 实验验证

主控芯片采用可抗高过载的芯片XCR3064XL,经实验证明可以承受30 000 g的过载。根据应用场合的设备承受的冲击过载范围,用环氧树脂对装置进行真空灌封处理,设计了抗冲击机械壳体,将电路固结在保护壳中以抗高过载。经过上述处理,测试仪能够承受高达10 000 g的过载。测试仪尺寸小,仅为Φ30×60mm。

本存储测试仪功耗低,休眠状态电流为0.2 μA,待触发态电流为5.6mA,触发后电流变为12 mA,采样完毕后电流仅为0.42mA。

为了验证该测试仪的性能和精度,进行了大量的实验室静态测试。将测试仪在三维无磁性转台上进行飞行体运动的模拟实验,试验结束后将转台闪存数据与测试仪的数据进行比较,计算出测量误差,进而验证测试仪的可靠性。

考核所使用的无磁性转台全部由木质和铝质材料改造而成,可实现自转、俯仰、偏航的三维运动,模拟弹体飞行。频率调节范围:0~60Hz。俯仰角度、偏航角度范围±180°。转台使用灵敏度高的脉冲码盘,对俯仰、偏航的输出角度值将精确到0.1°,缩小了因转台精度低引起的误差,提高了测量精度[6]。

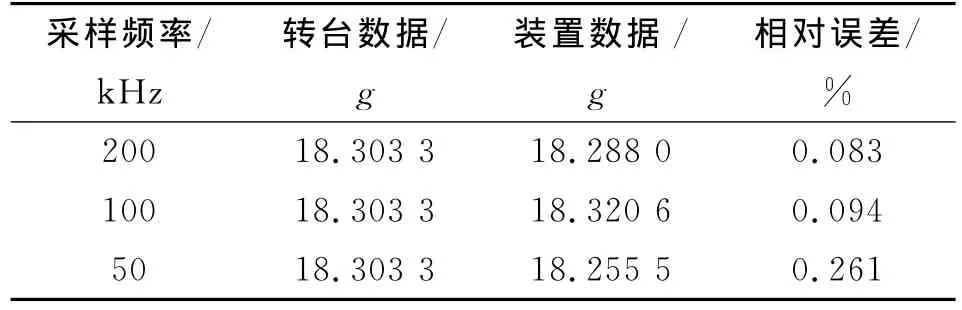

加速度考核方法采用离心加速度的方法,先测量好装置安装半径r,然后设定转速,设定装置采样频率,实验结束后将转台测试结果根据a=w2×r,计算出加速度值与测试仪的数据进行比较。测试结果如表1和表2所示。

表1 X轴加速度精度考核数据表Tab.1 X-axis acceleration data accuracy assessment table

表2 Y轴加速度精度考核数据表Tab.2 Y -axis acceleration data accuracy assessment table

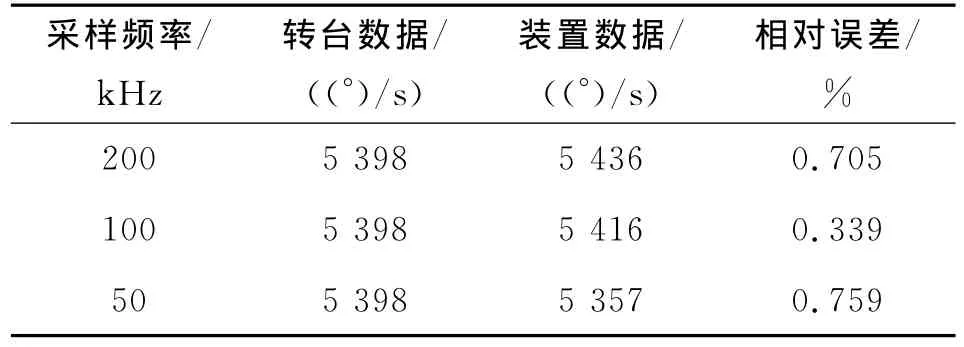

角速度考核方法为预先设定转台转速,装置预先编程设定不同的采样频率,测试结束后根据读数软件读出值,与转台闪存读出数据进行比较。测试结果如表3和表4所示。

表3 Y轴角速度精度考核表Tab.3 Y -axis angular velocity accuracy assessment table

表4 Z轴角速度考核精度表Tab.4 Z-axis angular velocity accuracy assessment table

经计算不同采样频率下测试结果基本一致,角速度绝对误差最大值为1.15%,误差主要来源于测量误差。加速度绝对误差最大值为0.27%,误差主要来源于为测量误差,误差大小达到测试要求,测试结果与转台数据得到很好的吻合。

4 结论

本文提出了基于复杂可编程器件的弹载存储测试仪。测试仪采用可反复擦写的CPLD芯片作为主控芯片,利用其内部丰富的逻辑单元实现了可高速采样且使用灵活的存储测试方案,设计通过休眠防止误上电;通过并行实现高速率采样,通过分频实现50kHz、100kHz和200kHz三种频率可选;通过计数实现8K×12bit、448K×12bit负延迟可选。测试仪具有抗高过载,稳定可靠,低功耗,尺寸小,成本低等优点,适用于弹载存储测试。同时测试仪的电路部分使用灵活,适用性好,还可应用于其他短时间的动态测试。

[1]李红旗,李东光,李世义.基于CPLD的弹载高速存储测试系统关键技术研究[J].弹箭与制导学报,2007(1):360-362.LI Hongqi,LI Dongguang,LI Shiyi.The key technology study based on the high-speed storage measurement and test system attached to bullets[J].Journal of Projectiles,Rockets,Missiles and Guidance,2007(1):360-362.

[2]李海燕.单片机测控系统的抗干扰技术[J].船电技术,2005(6):30-33.LI Haiyan.Anti-interference technology of measurement and control system within single-chip computer[J].Marine Electric & Electronic Engineering,2005(6):30-33.

[3]朱仕永,祖静,范锦彪.基于CPLD的弹载加速度存储测试仪[J].探测与控制学报,2009,31(3):43-45 ZHU Shiyong,ZU Jing,FAN Jinbiao.Missile-borne storage measurement and test instrument of acceleration based on CPLD[J].Journal of detection &control,2009,31(3):43-45.

[4]郭红英,祖静.存储测试专用集成电路成测试研究[D].太原:中北大学,2007.

[5]徐鹏,祖静,李乐.CPLD芯片抗高g值冲击性能分析[J].振动与冲击,2007,26(1):148-150.XU Peng,ZU Jing,LI Le.Performance analysis of the impact of resistance to high gvalue of the CPLD chip[J].Journal of Vibration and Shock,2007,26(1):148-150.

[6]段精婧,马铁华,范锦彪.基于无陀螺捷联惯导系统的四元数算法[J].探测与控制学报.2010,32(1):15-18.DUAN Jingjing,MA Tiehua,FAN Jinbiao.Quaternion arithmetic of projectile based on GFIMU[J].Journal of detection &control,2010,32(1):15-18.