铁路区间通信系统中的数字语音终端设计

黄池翔,罗 斌,胡祖翰

(西南交通大学 信息科学与技术学院,成都 610031)

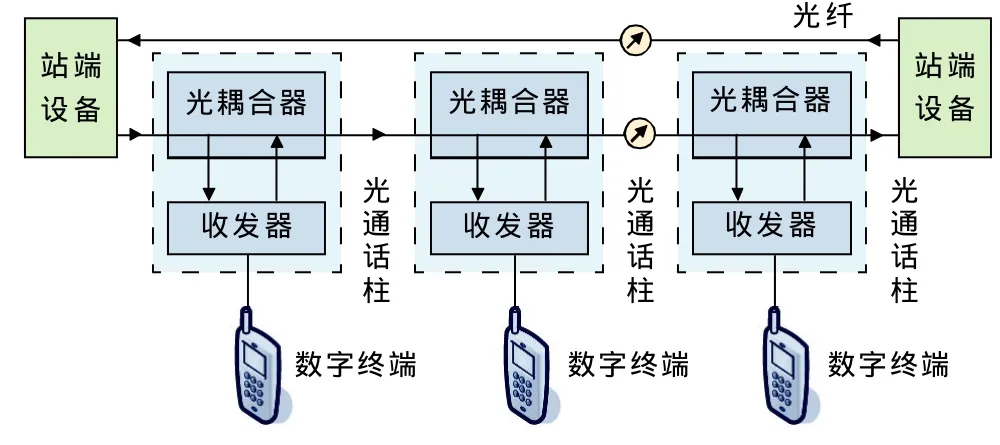

根据《铁路运输通信设计规范》(TB10006-2005)要求,铁路区间通信的服务包括车务、工务、电务、供电、水电等专用电话以及站间行车电话、区间电话、道口电话、桥隧守护电话和数据传输等。为了降低铁路通信的成本,提高信息的传输效率,实现多业务综合接入,本文提出了一种适用于铁路区间的光纤通信系统,结构如图1。

图1 铁路区间通信系统结构图

该铁路区间光纤通信系统可以实现站端设备与各个数字终端之间通话,数字终端的信号通过站端设备的转发与外界电话通话,数字终端和站端多方通话等语音服务。也能实现数字终端与站端之间的2 M和64 k的数据传输功能。

铁路区间光纤通信系统的优点:实现单光纤通信、一对光纤的T型光纤链路连接,在满足铁路区间通信业务带宽要求下,节约了光纤资源;实现了铁路区间的无源光网络,具有高可靠性、维护方便、维护成本低的特点;业务接口丰富,满足铁路区间的多业务接入需求,如语音、视频、各种监测数据等的综合接入;组网简单、方便;造价较低。

本文主要介绍了用在该系统中的数字语音终端的设计。该终端能对语音信号进行编码传输,同时要能从系统中接收相应的数字信号,重建语音信号,实现系统内以及系统相连的外部终端通话。数字语音终端为手持式独立供电所以功耗要尽可能低,该数字语音终端设计选用的语音芯片是MC145481。

1 数字语音终端的结构设计

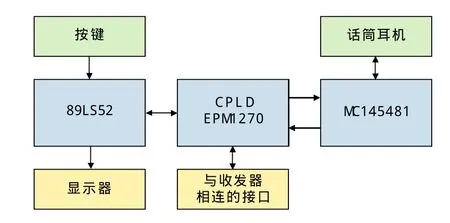

数字语音终端主要由MC145481为中心的语音编解码模块,CPLD(复杂可编程逻辑器件)为核心的数据处理模块,控制模块89LS52,键盘,显示器,耳机话筒构成,其结构如图2。单片机89LS52通过CPLD可以与系统中的控制站端设备交互,建立业务的请求或接收。终端的语音编解码数据,在单片机的控制下,通过CPLD的处理,实现与系统的对接。

图2 数字语音终端结构图

2 MC145481的结构功能及相关设计

2.1 MC145481的结构功能

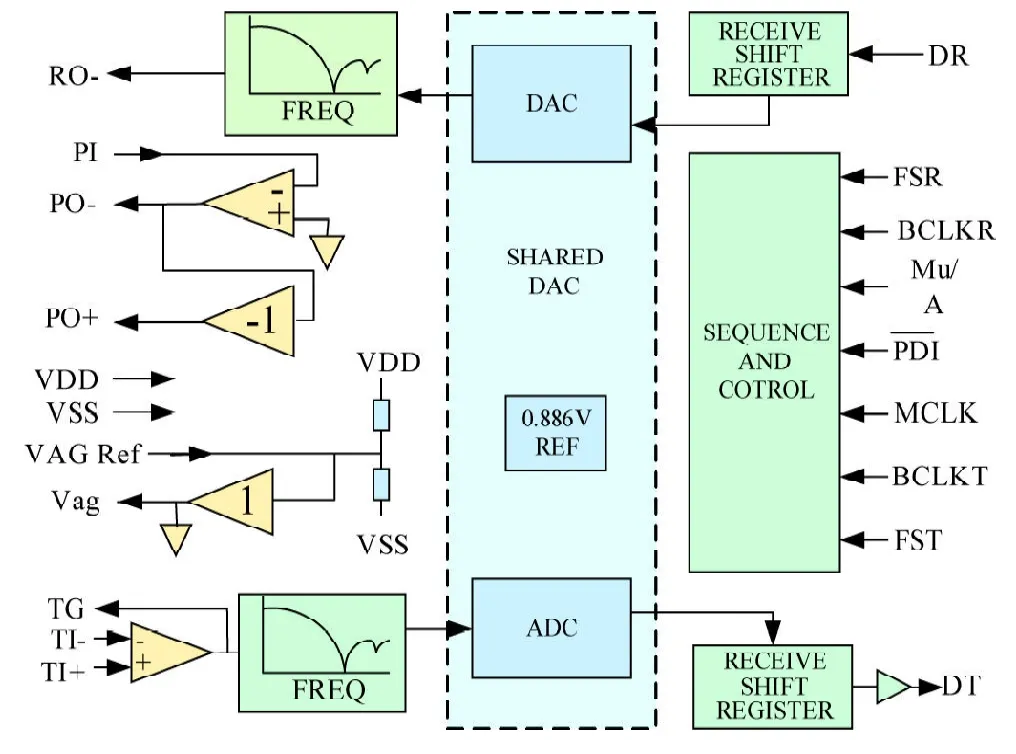

MC145481是单通道PCM编解码滤波器,它能实现语言的编码重建以及带宽限制,滤波等功能。它的结构如图3,支持A律编码和μ律编码选择使用。芯片的16脚μ/A为选择脚,接高电平时选择μ律编码,接低电平时选择A律编码,本设计选择μ律编码。

器件编码部分的输入端有一个低噪声的运算放大器,它的输入端是TI+和TI-输出端是TG。TI+端可以与电源相连使传输运算放大器关闭,这时TG脚为高阻抗状态 ,模拟信号可以直接输入TG。TG的内部是一个三阶抗锯齿处理前置滤波器,此后是一个工作频率在512 k的单端到差分的转换器,接着是一个截止频率为3.4 kHz的五阶开关电容的低通滤波器,再往后是一个截止频率为200 Hz的3阶开关高通滤波器,因此芯片的工作频率范围是200 Hz~3.4 kHz。

编码的接收部分包括DAC,采样单元,放大器,五阶3.4 kHz,修正率为SINX/X的开关电容低通滤波器和两阶有源平滑滤波器。平滑滤波器的输出端经放大器缓冲从RO-脚输出,这个输出能驱动2k的负载。

MC145481还有一对连接成推拉结构的功率放大器,PI脚连到PO-放大器的反相端,正向输入端从内部连到Vag脚,这个放大器可以通过两个外界电阻组成反向放大器。PO+放大器增益为-1它的输入从内部连到PO-的输出。这两个推拉式放大器构成一个差分式放大器,能驱动300 Ω负载。把PI脚连接到VDD上功率放大器可以独立于芯片的其他部分关闭。

图3 MC145481的结构图

2.2 MC145481的时序设计

MC145481芯片支持多样化的时钟模式,包括长帧同步模式,短帧同步模式,IDL和GCI时钟环境。长帧同步模式的帧同步时钟可以使用占空比为1/2的标准时钟,在终端的数据处理上实现方便,所以设计使用的是长帧同步模式。

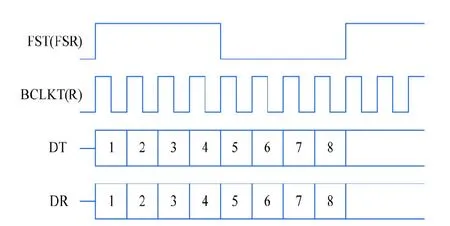

在长帧同步模式中, FST为传输帧同步脚,FSR为接收帧同步脚,帧同步有2个功能:同步数据的传输,控制内部数模和模数之间的转换。FST和FSR的输入要求8 k时钟且高电平至少保持带2个下降沿的数据时钟周期。在长帧同步时钟的上升沿处,开始收发一帧的数据,即编码部分在FST的8 k时钟上升沿后编码器顺序输出一次采样8位数字信号,语音重建部分在FSR接收到的8 k时钟上升沿后,送入芯片的8位数据也要是语音信号一次编码产生的8位数据,这样才能正确重建语音[2]。

本文的设计按要求,时钟的输入如图4,FSR和FST来自共同的8 k时钟源。BCLKR和BCLKT在长帧模式下可以接收64 k到4.096 M的时钟。MCLK的频率可以是256 kHz,512 kHz,1.536 MHz,1.544 MHz,2.048 MHz,2.56 MHz或4.096 MHz中的任何一个。设计中BCLKR,BCLKT用共同的64 K时钟源。MCLK输入2.048 M时钟。设计中输入的8 k,64 k和2.048 M3个时钟源由一CPLD芯片产生且按要求三时钟源的上升沿对齐,且芯片的收发数据按要求也要与8 k的帧同步时钟保持同步。

图4 MC145481的输入时序

2.3 MC145481的掉电模式状态设置

MC145481有上电模式和掉电模式2种工作状态,当语音终端不工作时可以将芯片设置在掉电工作状态,芯片就基本没有功耗,节约用电延长终端电池寿命。有两种方式可以使芯片工作在掉电模式,芯片的是掉电模式使能输入脚,当输入为低电平时芯片工作在掉电模式,另外一种方式是脚输入为高,让FSR和FST脚输入持续为低电平。当芯片在掉电模式时,VAG, TG, RO-, PO+, PO-和DT脚输出为高阻态,而VAG Ref脚被拉到VDD,形成一个非线性的高阻态电路。要让芯片恢复成正常工作态,芯片的FST,BCLKT和MCLK脚要输入时钟。

本文的设计运用接入高电平,由CPLD的8 K,64 K和2.048 M的时钟输出或低电平输出控制芯片的工作状态。

3 CPLD的功能设计

CPLD芯片是MAXII系列的EPM1270,选用TQFP封装,144引脚,1270个逻辑单元。

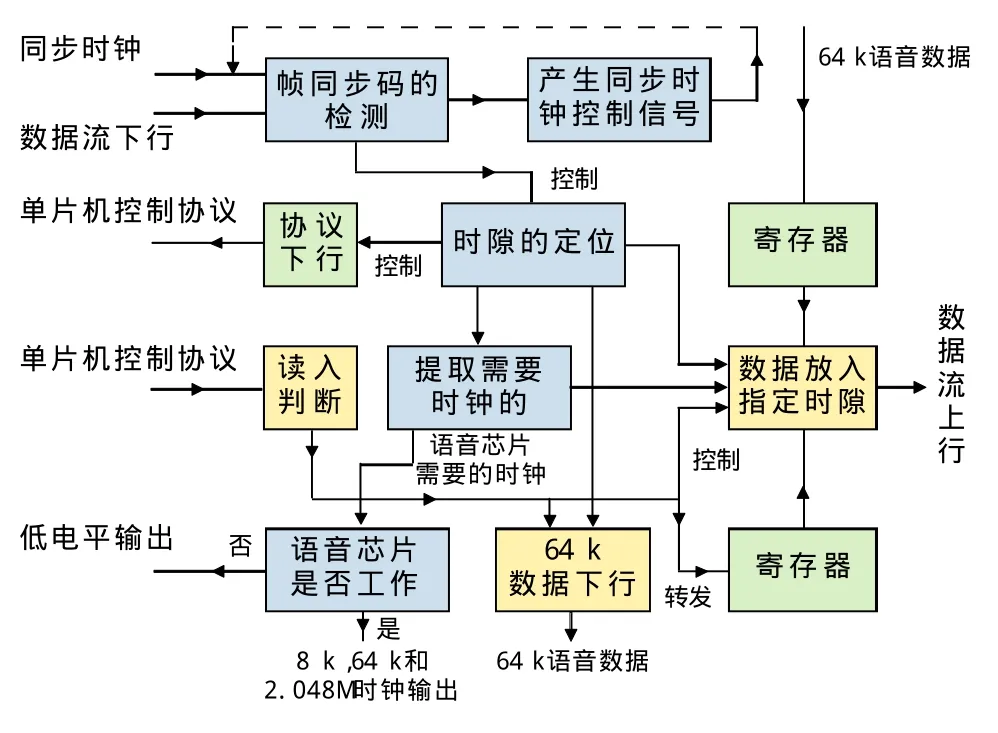

语音终端上CPLD的功能结构设计如图5。当语音终端接入系统中后,CPLD检测下行数据中的帧同步码,产生锁定同步时钟的控制信号,控制快速锁定同步时钟,在同步时钟的控制下确定对应帧和时隙的位置,解下控制协议时隙的数据送给单片机。终端单片机的控制协议,经过CPLD转发送到系统中实现与控制主机交互,当有业务建立时控制主机给终端分配上下行数据的时隙,然后终端的单片机控制CPLD把对应时隙的数据下行到缓存中,同时产生与数据同步且上升沿对齐的8 k,64 k和2.048 M时钟,满足MC145481的时序要求。下行的数据再经速率转换成64 k数据送到MC145481的DR端。此时要求8 k时钟上升沿后一周期内的8 bit 64 k数据要是语音一次编码产生的8 bit数据,否则语音芯片就还原不出正确的语音信号。若语音终端工作时,CPLD就输出8 k,64 k和2.048 M时钟,否则输出低电平,使编码芯片就工作在掉电状态。同时CPLD读入语音芯片编码的64 k数据,在单片机控制下把数据放在终端上行数据的时隙中。

图5 CPLD模块的功能结构图

4 结束语

本文按照新型的铁路区间通信系统的要求,设计了一个简便的,能满足铁路区间用户语音要求的语音终端。语音终端数据在系统中传输使用的是光信号的时分复用方式,终端与系统使用T型的组网方式,组网简单、方便、节约光纤、造价较低,每个语音终端即插即用,终端是否接入或工作不影响系统的其它功能。

[1]铁道第二勘探设计院. 铁路运输通信设计规[S]. (TB10006-2005). 2005(4):16-19.

[2]罗力凡. 基于VHDL的FPGA开发快速入门·技巧·实例[M]. 北京:人民邮电出版社,2009.

[3]周润景,图 雅,张丽敏.基于QuartusII的FPGA/CPLD数字系统设计实例[M]. 北京:电子工业出版社,2007.