高效硬件可重构单片机最小系统设计

贾立新,曹全君

(浙江工业大学信息工程学院, 浙江杭州310023)

0 引言

单片机最小系统是构成各种不同功能单片机应用系统的核心模块,在综合电子技术实验、大学生电子设计竞赛、毕业设计等教学环节中具有广泛的应用。现有的单片机最小系统种类繁多,各有特色,但始终无法很好地解决高效和通用灵活的矛盾,即最小系统既要硬件电路简洁、功耗低、性价比达到最佳,同时又要扩展方便,能适应各种不同类型的单片机应用系统。随着集成电路技术的发展,出现了硬件可重构的CPLD/FPGA和高速、高集成度的SOC单片机。在单片机最小系统设计中,将CPLD/FPGA和SOC单片机相结合,使得最小系统的硬件电路可重构,是解决高效率和通用性矛盾的有效途径。将可重构的单片机最小系统应用于电子信息类专业的实验教学以及科技实践中,可以有效的提高创新型教学水平和提升电子系统的开发效率[1-4]。可重构的单片机最小系统的设计和应用[5],为电子系统的灵活开发和重复利用打开了广阔空间。

1 方案设计

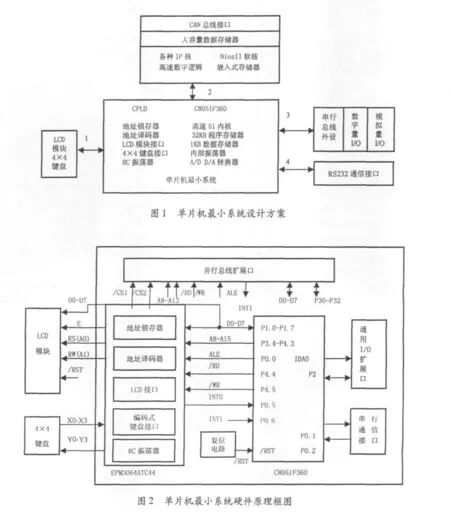

单片机最小系统选用美国芯科公司的集成混合信号系统级芯片C8051F360单片机。由于C8051F360片内程序存储器容量足够大,已不需要扩展程序存储器,同时集成了10位A/D转换器和10位D/A转换器,除非分辨率和转换速度难以满足系统要求,很少需要扩展A/D和D/A转换器。在设计系统扩展口时,主要考虑人机交互设备、大容量(大于64kB)数据存储器、FPGA等外部设备的扩展。单片机最小系统设计方案如图1所示。

2 主要硬件电路设计

C8051F360单片机有5个并行口P0~P4,按其功能可为3部分:第一部分用于外部数据存储器扩展接口,实际上就是构成单片机的并行总线;第二部分I/O引脚用于单片机最小系统自身扩展,如键盘中断INT0、C2调试接口、异步串行通信等;第三部分用于通用I/O扩展口。考虑到C8051F360单片机内部振荡器的精度可达2%,能满足一般单片机系统的要求,为了节省单片机的I/O引脚,同时降低电磁干扰,单片机的系统时钟由内部振荡器产生。复位电路采用专用复位芯片TCM811。TCM811芯片体积小,具有上电复位和手动复位功能,可同时向单片机和LCD模块提供低电平有效的复位信号。单片机最小系统的硬件原理框图如图2所示,CPLD内部逻辑电路可通过Quartus II软件设计。

(1)LCD模块接口电路

C8051单片机与LCD模块通过并行总线相连。通过对单片机和LCD模块的时序分析,可用单片机地址总线中的A1、A0作为LCD模块的RW、RS信号,将单片机控制总线中WR和RD相与非作为LCD模块的使能信号E。E信号的产生加一片选信号LCDCS。

(2)编码式键盘接口设计

采用CPLD设计了编码式键盘接口。Y0~Y3为4根列扫描信号输出线,轮流将每一列置为低电平。X0~X3为4根行输入线,当没有键按下时,X0~X3被外部上拉电阻拉成高电平。2位二进制计数器CNT4A和2-4译码器DECODER用于产生键盘列扫描信号。行值编码器ENCODE将行输入信号转换成2位二进制编码。因为CNT4A的输出C1、C0确定了闭合的键处于哪一列,ENCODE的输出C3、C2确定了闭合键处于哪一行,C3~C0实际上构成了闭合键的4位键值。CNT16A为消抖计数器,当键闭合时间超过16ms时,CNT16A输出由高到低的键有效信号DAV。DAV一方面作为键值寄存器REG4锁存信号将键值锁存,另一方面作为单片机的外部中断INT0的请求信号。键值数据端口采用三态输出,由TS4模块实现。

(3)由CPLD实现的RC振荡器

采用RC振荡器来产生KEYCLK信号。用CPLD实现的改进型RC振荡器原理图[7]如图3所示。图3中G2输出和G3的输入虽然连在一起,但不能共用一根I/O引脚;要注意RC振荡器的振荡频率不能太低,否则虽然能产生振荡波形,致使键盘接口中的计数器工作不正常。

图3 CPLD实现的RC振荡器

3 单片机最小系统在电子系统设计中的应用

数字化语音存储与回放系统是一个典型的电子系统,其系统框图如图4所示。利用上述单片机最小系统,配以键盘显示电路、外部数据存储器、放大滤波电路,就可以实现语音存储回放系统的硬件电路。

虽然C8051F360单片机内部含有1KB的XRAM,但对语音存储与回放系统来说,仅靠单片机内部的数据存储器是无法满足需要的。当外部扩展的数据存储器的容量大于64K时,可采用存储器分页的方法进行扩展,将容量为2N的存储器划分为容量为2L(L小于16)的存储页面,单片机通过页地址选中其中一页,然后再访问页内存储单元。通过FPGA可以轻松的实现存储器扩展,充分体现了硬件可重构单片机最小系统扩展的灵活性。

图4 数字化语音存储与回放电路

4 结束语

采用SOC单片机和CPLD实现的单片机最小系统具有集成度高、资源丰富、系统扩展方便的特点,已广泛应用于大学生电子设计竞赛、本科生毕业设计、大学生创新计划等实践教学环节,也可用于科研项目的前期预研。实践证明,通过将CPLD/FPGA引入单片机系统设计,使硬件电路可以像软件一样修改,可有效缩短电子系统的开发时间,提高设计灵活度。对教学仪器的研发、单片机应用系统的设计具有借鉴意义。

[1] 查建中.研究型大学必须改革本科教育以培养大批创新人才[J].高等工程教育研究,2010,(5):14-25.

[2] 姜丽华,赵红艳.创新能力培养学科与活动课程相结合[J].教育科学,2010,(10):51-54.

[3] 毕立恒,刘玉宾.一种实用单片机和CPLD最小应用系统的设计[J].自动化技术及应用,2009,(8):111-113.

[4] Ian Grout.基于FPGA和CPLD的数字系统设计[M].北京:电子工业出版社,2009:405-438

[5] 秦兴,王文,李为健,等.基于FPGA的硬件可重构数控系统的研制[J].仪器仪表学报.2002,23(3):407-409.