FPGA低功耗的设计研究*

何艳霞 何永泰

(楚雄师范学院物理与电子科学系,云南 楚雄 675000)

FPGA低功耗的设计研究*

何艳霞 何永泰

(楚雄师范学院物理与电子科学系,云南 楚雄 675000)

本文根据串行、并行两种算法,利用VHDL语言设计八位加法器,分析研究不同算法对基于FPGA设计特性的影响。所设计的两种加法器,在QuartusⅡ7.2中基于EPM240F100C5进行了功耗、运行速度、逻辑单元占用等性能的分析。分析与实验结果表明,不同算法会对设计系统的特性产生影响,所设计的并行加法器对FPGA逻辑单元、动态功耗的占用与串行加法器相比占用资源少,功耗低,具有较好的特性。

VHDL程序;低功耗;逻辑单元;设计方法

1.引言

基于FPGA设计的数字系统中,降低FPGA的功耗可带来许多好处,例如提高系统的工作速度,缩短运行时间、降低使用成本、减小器件的体积、延长电池的使用寿命,同时低功耗的器件可以延长器件的使用时间和实现更低成本的电源供电系统。而影响FPGA设计系统功耗的因素有很多,例如系统的工作电压,在FPGA中占用资源的大小等。在本文,为研究不同算法对FPGA系统特性的影响不同,根据串、并行算法,利用VHDL语言设计了两种不同算法加法器,并对其特性进行了分析。

2.不同加法器的基本原理

在二进制加法器中常用的主要有并行加法器和串行加法器两种[1]。设计中使用8位串行与并行加法器。

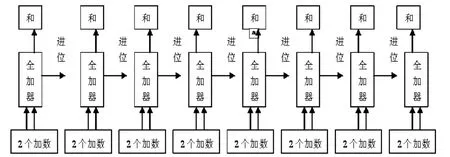

2.1 8位串行加法器的基本原理及算法

8位串行加法器是将8个全加器作为一个基本组件级联构成的,运算时低位的加数与被加数相加运算求得和与进位,将和输出,但是求得的进位需传给下一位的全加器。基本运算结构如图1所示[2]。在图中,低位全加器进位输出端直接与相邻的高一位全加器的进位输入端相连,只有上一位全加器加法运算完成时下一位的全加器加法运算才能进行。

图1 8位串行加法器结构图

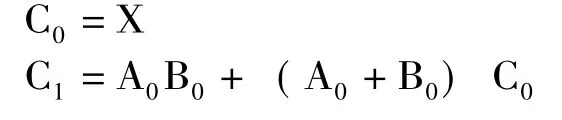

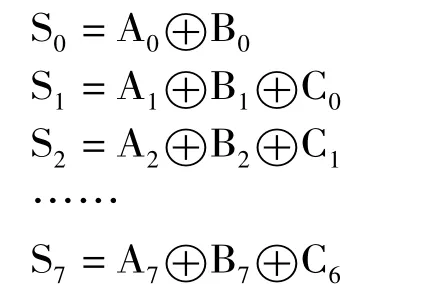

根据8位串行加法器的运算结构图,可得出串行加法器进位表达式为:

同时,从8位串行加法器的运算结构图和进位表达式还可以得出运算结果表达式为:

从上式可知,高位的进位产生与相邻低位的进位输出有关,只有低位的进位运算完成,与之相邻的高位的进位才能运算出。同时从公式也可得出和的产生也依赖于相邻低位的进位输出。

2.2 8位并行加法器的基本原理及算法

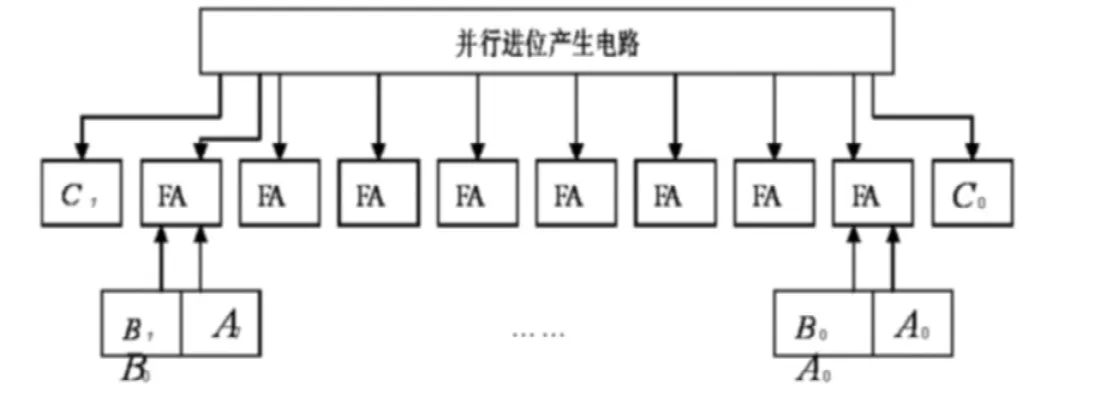

8位并行加法器是采用2个4位的并行加法器级联构成的,而4位的加法器则是采用4个一位的全加器级联成串行加法器。运算时加数与被加数相加运算求得和与进位。参加运算的两个加数与被加数可以直接确定进位C的值,不依赖于上一位的低位的进位值。因而每一位全加器都可以同时进行加法运行求出进位。基本运算结构如图2所示[2]。在图中,低位全加器进位输出端不与高一位全加器的进位输入端相连。8位全加器FA各自产生进位在通过并行进位产生电路直接算出所有进位 (低FA的进位输出直接与并行进位产生电路,并不与高位FA的进位输出相连)如图所示:

图2 8位并行加法器结构图

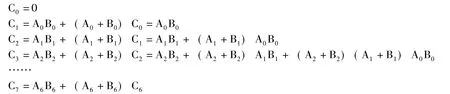

根据8位并行加法器的运算结构图,从而可得出下面的进位表达式:

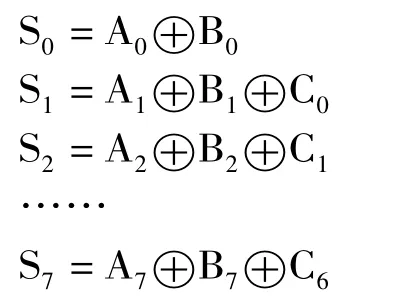

从8位并行加法器的运算结构图和进位表达式还可以得出运算结果表达式为:

从上式可知,所有位的进位的产生都不依赖与低位的进位。

3.8位串行与并行加法器的VHDL语言程序设计

在设计中,根据VHDL语言程序的结构特点,采用元件例化语句实现八位加法器串行与并行的设计,在元件例化语句中,主要分为两个文件,插入一个一位加法器、插入一个四位加法器以及顶层文件,各层之间通过信号传递值。

3.1 8位串行加法器的VHDL程序设计及功能仿真分析

在该方法中,采用VHDL语言的元件例化语句描述方式来实现FPGA低功耗的设计。在设计程序时,首先要先定义全加器顶层设计元件端口信号,即输入端口:A,B,数据类型定义为IN STD_LOGIC_VECTOR。CIN是输入的进位,数据类型也定义为IN STD_LOGIC;输出端口:S为和,数据类型被定义为OUT STD_LOGIC。CO为输出的进位。定义好端口后要在结构体中申明一位全加器最为各层之间的信号传递值。其中每一个全加器都定义了1个信号C作为器件内部的连接线,最后采用映射语句port map()将8个一位的全加器连接起来构成一个完整的全加器[3]。在编写程序时要注意低位全加器进位输出端作为高一位全加器的进位输入端,每前一位的全加器加法运算完成后后一位的全加器的加法运算才能进行。

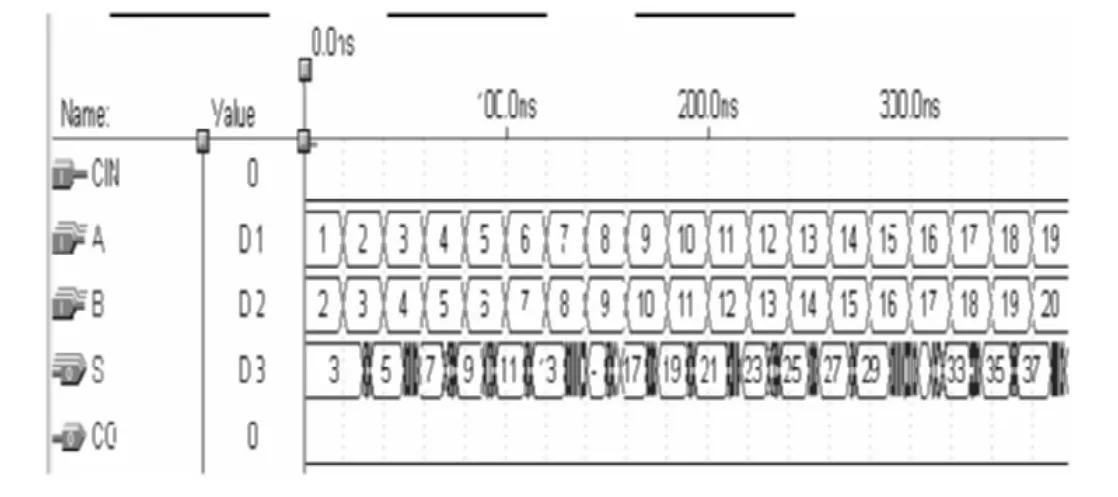

仿真波形如图所示:

图3 8位串行加法器的仿真结果图

仿真结果显示:

该设计是正确的,输出的值与理论值一致。仿真图显示出和值小于256时全加器的CO没有进位,而当和值加到256,CO=1,S输出0。

3.2 8位并行加法器的VHDL程序设计及功能仿真分析

在该方法中,因为FPGA是现场可编程门阵列,其基本单元是查找表,采用查找表的可以快速实现加法功能,即可以直接实现并联加法功能。所以8位并行加法器采用VHDL语言的元件例化语句描述方式来实现FPGA低功耗的设计。其中利用元件例化语句调用了4位并行加法器生成的底层文件,随后把这两个加法器进行级联实现运算功能,最后将结果的最高位赋值给进位输出端CO8。在设计程序时,首先要先定义8位全加器顶层设计元件端口信号,即输入端口:A,B,C数据类型都被定义为IN STD_LOGIC_VECTOR。输出端口:S为和,数据类型定义为OUT STD_LOGIC。CO为输出的进位。定义好端口后,在结构体中才能运用元件例化语句作为各层之间的信号传递值。在整个设计中定义了2个信号C1,C2作为器件内部的连接线,最后采用映射语句port map()将2个4位二进制全加器连接起来构成一个完整的全加器。在编写VHDL程序时,低4位的全加器进位输出端连到高4位全加器的进位输入端,各位全加器可以同时进行加法运算。

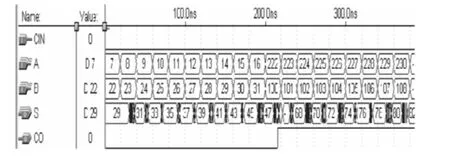

仿真波形如图所示:

图4 8位并行加法器的仿真结果图

仿真结果显示:

该设计是成功的,输出的值与理论值一致。仿真图显示0到255之间的和值全加器的CO没有进位,而当和值加到256,CO=1,S输出0,当加到的和值大于256,CO=1,S输出为和与256的差。

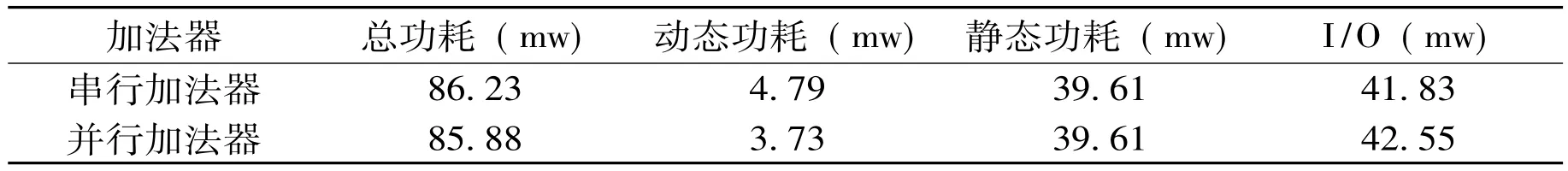

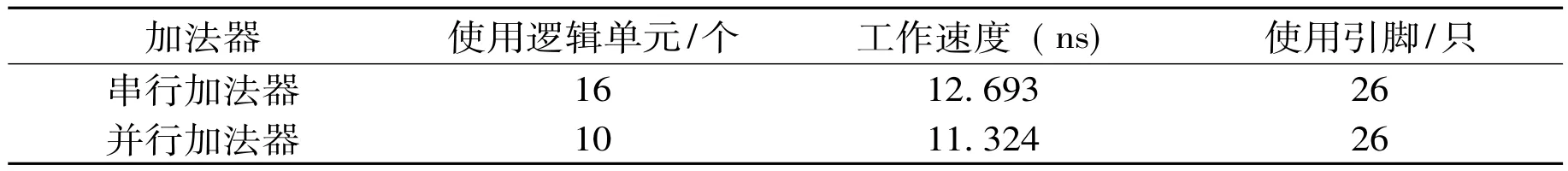

4.两种加法器在FPGA中实现的特性分析

为了分析不同算法设计的加法器在FPGA中实现的特性,分别在MAXⅡ系列下的EPM240F100C5器件中,利用QuartusⅡ7.2对两种不同设计的加法器VHDL程序分别进行逻辑单元的占用的大小、时钟速度及功耗等的结果分析。仿真之后主要选择了两组结果进行比较。分析结果如表1、表2所示。从分析结果中可以看出,在并行加法器中,逻辑单元的占用、总功耗和动态功耗与串行加法器相比较分别减少了2.5%、0.358mw和1.06mw,运行速度提高了1.369ns。表明并行加法器设计有利于减少器件资源的占用与提高工作速度。

表1 分析结果比较

表2 分析结果比较

5.结语

根据实验和仿真结果的分析,利用VHDL语言设计的串行与并行加法器其对FPGA特性的影响不同。通过比较,利用并行加法器,所使用的逻辑单元、动态功耗与串行加法器相比较分别减少了2.5%和1.06mw,运行速度提高了1.369ns。因此,并行加法器设计有利于减少器件资源的占用与提高工作速度。

[1]马龙.8位加法器实现原理 [C].http://202.115.21.138/wlxt/ncourse/EDA/web/zhidao/EDA41.htm.2003.1~4.

[2]丁洪鑫,秦磊华.组成原理课下报告_8位并串行加法器 [R].组成原理课下实践报告,2011.2~3.

[3]潘松,黄继业.EDA技术实用教程 [M].科学出版社,2002.1~3.

[4]周奇勋,王勉华,乐春峡 [J].基于FPGA的VHDL语言设计优化.仪器仪表学报,2003.24(4).1~5.

[5]赵亚威,吴海波.基于fpga的快速加法器的设计与实现 [J].现代电子技术,2005.28(10).1~2.

[6]褚振勇,翁木云.FPGA设计及应用 [M].西安:西安电子科技大学出版社,2002.154~167.

[7]安印龙,许琪,杨银堂.并行加法器的研究与设计 [J].晋中学院学报,2003,(4).1~2.

[8]雷伏容,李俊,尹霞.速加法器的设计 (1)[M].清华大学出版社,2010.1~2.

Research of FPGA Low Power Consumption Design

HE Yan-xia;HE Yong-tai

(Department of Physics and Electronic Science,Chuxiong Normal University,Chuxiong 675000,China)

According to serial and parallel algorithm,the influences of different algorithm on FPGA design characteristics are analyzed by using VHDL language 8 bits adders in this paper.Two adders are analyzed in QuartusⅡ7.2 based on EPM240F100C5 to test power consumption,running speed and logic cells occupancy.The results show that the parallel adder has lower power consumption,lesser occupancy of FPGA logic cells and dynamic power compared with serial adder.

VHDL program;low power consumption;logic cell;adder

TN741

A

1671-7406(2012)06-0022-04

2012-04-25

何艳霞 (1989—),云南姚安人,大学本科,电信2008级学生。

(责任编辑 司民真)