SAA7115视频解码芯片寄存器的配置与应用

段建宏,梁海波,张 广

(西安电子科技大学 技术物理学院,陕西 西安 710071)

SAA7115[1]是飞利浦半导体公司推出的9位视频解码芯片。可提供双9位低噪音、2x过抽样模拟到数字转换,其信噪比仅为10~15 dB,是同类产品中解码性能最高的解码芯片,主要特点有:1)6通道模拟信号的输入,内有源选择器;2)2个改进的 9-bit COMS 模数转换器;3)可实现对 CVBS、Y、C、信号的自动控制;4)加强型行、场同步检测,自动延迟矫正PAL制式相位误差;5)TV/VCR信号源自动检寻。

1 引脚说明

SAA7115内部框图如图1所示。其主要管脚及其功能如下:45 脚(ICLK):图像主时钟输出;46 脚(IDQ):图像数据限制;47 脚(ITRI):图像端口控制信号;52 脚(IGPV):多目标场基准信号; 53 脚(IGPH):多目标行基准信号;54~57,59~62 脚(IPD0-IPD7) 图像数据输出端口;64~67,69~62 脚 (HPD0-HPD7):主端口数据输入/输出;81~82,84~87,89~90(XPD7-XPD0):扩展端口视频输出数据。

其中模拟输入管脚由 20(AI11)、18(AI12)、16(AI21)、14(AI22)、12(AI23)、10(AI24) 6 个视频输入管脚的不同组合来控制,具体由SA02寄存器的位(D0~D4)来进行控制,信号由 14管脚(AI22)输入,亮度信号由 18管脚(AI12)输入,其余4个管脚用电阻电容接地以保证系统的稳定性。

图1 SAA7115的部分引脚排列Fig.1 Part of the pin arrangement of SAA7115

2 具体应用及寄存器配置

2.1 总体系统设计

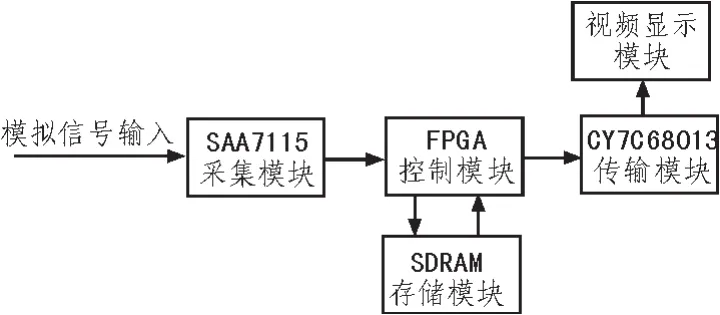

一个简单的视频采集系统框架机[2-3]图如图2所示。

图2 视频采集框架Fig.2 Frame work of video collection

该系统中模拟视频信号经过CCD采集进入SAA7115解码芯片进行A/D信号处理再由FPGA存储到SDRAM阵列中,然后通过单片机CY7C68013控制进行数据上传。SAA7115解码芯片的寄存器是在CY7C68013单片机的下位机程序里进行配置。

2.2 SAA7115的时序

系统中SAA7115的芯片时序如图3所示。

2.3 SAA7115解码芯片寄存器的配置

在解码过程中需要对芯片里256个寄存器逐一进行配置机[4-5]才能达到正确的视频解码数据,由于只需要得到视频信号输出,本次实验不需要音频寄存器(SA30~SA3A)、字幕寄存器(SA6B~SA71)及事件 B 寄存器(SAF8-SAF9)进行配置,根据SAA7115的datasheet及所需要的输出视频格式来配置,本实验采用PAL制式输出配置。在所有寄存器中,一些寄存器如 SA1C(水平差增益)、SA1D(垂直差增益)、SA59(水平补偿)、SA5A(垂直补偿)等按芯片资料的默认配置便可,视为不关键寄存器,而像SA96H-SA9BH、SA88H(ADC_PORT)等寄存器的配置结果会直接影响视频图像的正确输出,因此需要精心配置与重复配置,可视为关键寄存器,配置如下:

图3 8位数据输出的时序图Fig.3 8 bits of data output timing diagram

SA02:模拟输入控制寄存器,输入从 AI2输入(D0~D3),放大反向滤波器有效(D4~D7),故配置为0xc1H;

SA09:亮度控制寄存器,采集过程在4.1 MHz时钟频率下,低通滤波器在 2 dB通道有效 (D0~D3),小调制带宽(D4),延时采用内部通道延时 (D5),亮度梳状滤波器有效(D6),色度陷阱梳状滤波器旁路(D7),故配置为0x48H;

SA0E:色度控制寄存器,在4.4 MHz时钟频率下采用PAL 制颜色标准(D4~D6),色度梳状滤波器有效(D0),自动色度标准控制(D1)与标准色度时间常数(D2)在视频行有效情况下采用垂直滤波器进行PAL制误差纠正(D3),故配置为0x81H;

SA83:X-port输出时钟相位及I/O端使能控制寄存器,X-CLK引脚用于输出, 使用默认配置 (D4~D5),X-port在XTR1 为“1”时输出有效(D2~D0),故配置为 0x33;

SA84:I-port输出信号定义寄存器,输出为4种信号IGPH、IGPV、IGP0、IGP1。输出模式中 IGPH 是行门(h-gate)信号(D1~D0),IGPV 是场门(v-gate)信号(D3~D2),IGP0 在默认极性时输出为 0(D5~D4),IGP1 为输出场 ID(D6~D7),故配置为0x30H;

SA86:I-port信号定义寄存器,串口空标志与满标志采用双字节16位(D3~D0),视频数据包通过ITRDY引脚控制输入(D7),对 I-port输出视频数据进行传输(D6),故配置为0x40;

SA93:I-Port输出格式设置寄存器,输出数据为4:2:2字节格式(D0~D2)的 YUV(D3~D4)视频格式,需要跳过只含有Y信号的数据行(D5),在行消隐间的无效数据用0x00填充(D6),输出的数据流中应含有 SAV,EAV 标准(D7),故配置为0xC0;

SA96~SA9B:输出窗口大小寄存器,SA96、SA97为水平输出窗口定义,SA97为高8位,SA96为低8位,当输出行为720,其二进制为:10 1101 0000,故配置为 SA97=0x02,SA96=0xd0;SA9A,SA9B为垂直输出窗口定义,由于视频扫描时采用隔行扫描,因此一场图像垂直输出为配置长度的2倍,当输出为576时只需配置成288,其二进制为:1 0010 0000,故配置为 SA9B=0x01,SA9A=0x20;

SAA8~SAA9:水平亮度比例增量,选择比例为1(即1024/1024),故增量为 1 024 即(100 0000 0000),SAA9 为高位,SAA8 为低位,故配置为 SAA9=0x04,SAA8=0x00;

SAAC~SAAD:水平色度比例增量,水平色度增量为亮度增量的一半(水平扫描有奇偶场),故增量为1 024/2=512即(10 0000 0000),SAAD 为 高 位 ,SAAC 为 低 位 , 故 配 置 为SAAD=0x02,SAAC=0x00;

SAB0~SAB1:垂直亮度比例增量,配置方法同水平亮度增量相同故SAB1=0x04,SAB0=0x00;

SAB2~SAB3:垂直色度比例增量等于水平亮度增量(1024),故 SAB3=0x04,SAB2=0x00。

寄存器中有些寄存器需要重复多次配置具体为:

SA88:ADC_PORT输出控制、起始控制与低功耗省电控制,最初时对其进行输出控制配置为0xf8使其达到正常的运行模式;最后需要配置3次0x00,使得其复位时计数器、输出通道重置,考虑到音频时钟产生的输出情况还需配置1次0xf0。故总共5次重复配置。

SA85:I-Port基准信号极性与信号定义,4个输出信号端口 IDQ(默认高有效),IGPH(默认高有效),IGPV(默认高有效),IGP0(反转),IGP1(默认高有效)的极性, D4-D0 缺省配置值0000,高三位为视频数据标志位选择可以选择4种数据标志位因此有000、010、100、1104种选择;故SA85H有四种配置选择 0x00、0x40、0x80、0Xc0,当 IGP0 输出为高电平时需要对其进行反转,因此D4-D0也可以01000对SA85H配置还有0x08,总共5次重复配置;

SA0E:色度控制寄存器,在选择梳状滤波器、PAL制式、标准时间常数、相位进行校正、清除位有效的模式下其配置为0x81;当选择梳状滤波器无效时,则清除位也无效故该模式下的配置为0x00,总共2次重复配置。

传输数据程序与配置好的代码加载到keil软件,在EZUSB-F2X(及CYYC68013)界面的运行下进行数据采集机[6],配置完成后实时采集图像数据的界面如图4所示。

图4 采集数据界面Fig.4 Interface chart of acquisition data

在单片机数据上传输过程中采用的是批量传输(bulk)方式,对采集的数据进行数据上传显示的图像窗口如图5所示。

3 结束语

文中对SAA7115在图像采集系统中的寄存器应用进行了研究,关键寄存器进行了配置,最后采集到了图像的正确数据并得到了很好的显示,在以后的情况下将对视频窗口的控制,输出制式的控制,亮度的控制,音频,字幕的显示进行更深一步的研究。

图5 图像窗口显示界面Fig.5 Interface of image window

[1]张海峰.多制式视频解码芯器SAA7115H在图像融合的应用[J].电子产品世界,2006,3(11):104-106.

ZHANG Hai-feng.Appliacation of Multisystem video decoding SAA7115H core lifter in image fusion[J].Electronics World,2006,3(11):104-106.

[2]张林勇.基于USB与FPGA的视频采集系统设计[D].西安:西安电子科技大学,2011.

[3]李虹.CCD信号采集系统的USB接口设计 [J].现代电子技术,2005(8):17-19.

LI Hong.Design of USB interface in CCD signal acquisition[J].Modern Electronics Technique,2005(8):17-19.

[4]张晓健.视频解码芯片SAA7113的初始化与控制[J].芯片应用,2003(8):84-85.

ZHANG Xiao-jian.Initialization and control of video decoder chip SAA7113[J].Chip,2003(8):84-85.

[5]高星.基于SAA7115视频解码器的应用设计[J].西安电子工程研究所,2006(1):10-13.

GAO Xing.SAA7115 video decoder application design based on SAA7115[J].Xi’an Electronic Engineering Research Institute,2006(1):10-13.

[6]周剑波.利用FPGA和USB总线的视频图像的采集与处理系统的设计[J].北京科技大学学报,2006,28(9):887-889.

ZHOU Jian-bo.Design of video image acquisition and processing system using the FPAG and USB[J].Journal of University of Science and Technology Beijing,2006,28(9):887-889.