SOI材料片缺陷研究

孙建洁,吴建伟,陈海峰

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

绝缘体上硅(Silicon on Insulator,SOI)技术凭借其全介质隔离结构,能有效抵抗瞬态辐射和单粒子辐射,因而是制造抗辐射集成电路的首选技术。

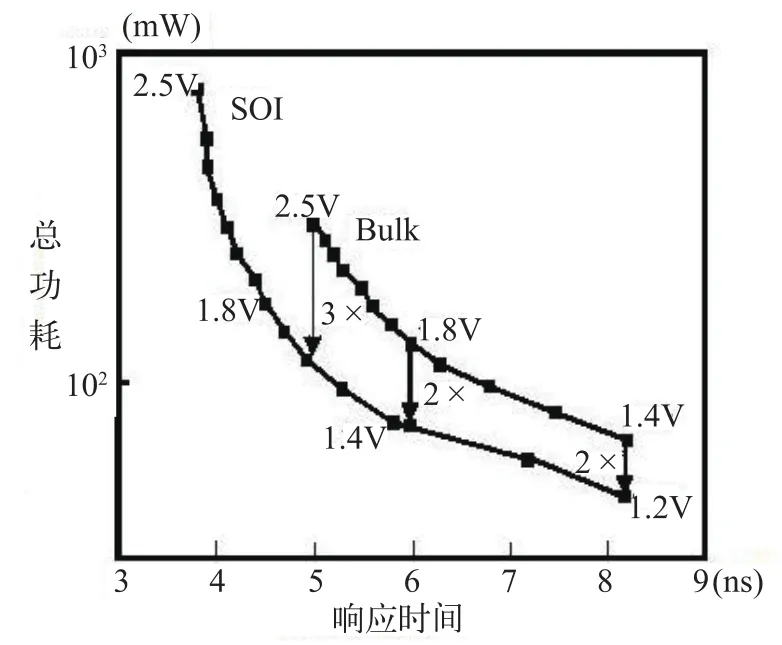

基于SOI材料的电路具有高速、低压、低功耗、耐高温等优点,因此SOI技术在亚微米VLSI中有较大的应用前景,被国际上公认为“21世纪的硅集成电路”[1]。

SOI材料片的主流制备技术分为两种,一种是采用SIMOX(注氧隔离方法)形成的SOI圆片,另一种是采用Bonded Smart-Cut(键合后智能剥离)方法制备的UNIBOND SOI圆片。两种圆片一种采用氧离子注入结合高温退火形成绝缘氧化埋层,另一种的绝缘埋层则是通过热氧化方法产生,并且键合前在器件层通过注入氢离子来完成起泡和剥离。

SOI材料片由体硅片加工而成,在加工过程中不可避免的会引入缺陷,缺陷的引入会导致后续电路加工过程中出现许多未知的隐患,本文主要介绍各种缺陷的形成及特征,以及对其检测的手段。

图1 SOI与常规MOS集成电路性能比较

图2 两种SOI材料片制备工艺流程图

2 缺陷定义及影响

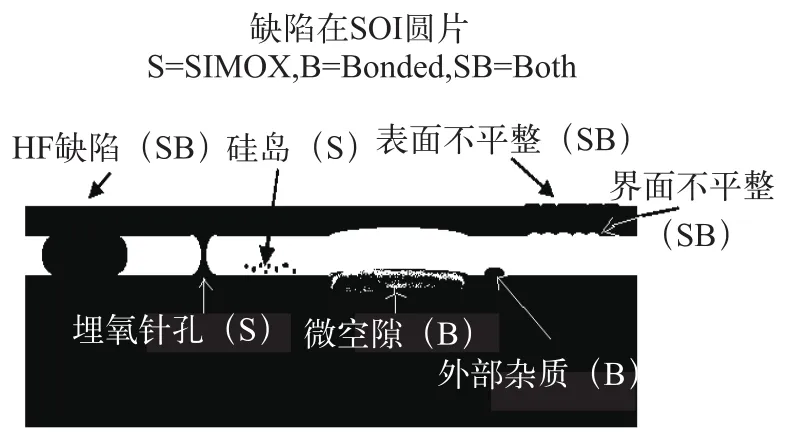

SOI材料具有三层结构:顶部硅层,绝缘层和硅衬底。SOI材料片的缺陷按照SOI结构的不同界面分为表面顶层Si缺陷、Si/SiO2界面缺陷和BOX中缺陷。

图3 SOI圆片中主要缺陷示意图

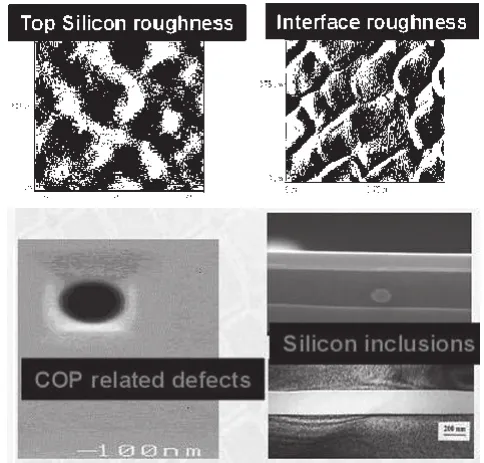

其他缺陷还包括硅剥落(Silicon peelings)、硅侵蚀(Silicon pitting)、坑洞(Craters)、层错/位错(dislocations /stacking faults)、残余应力(residual stresses)、边缘翘曲(wafer edge lifting)、COP-related defects等。

表面顶层Si界面缺陷主要表现在表面粗糙不平整,清洗腐蚀后缺陷。不管是SIMOX或是Bonded Smart-Cut SOI材料片均存在上述缺陷。顶层Si表面粗糙很大程度上是由于Si/SiO2界面的不平整造成的。为了保证材料片的制备过程中表面颗粒可控,通常清洗步骤是不可或缺的,清洗中引入的表面缺陷通常是由腐蚀造成的硅侵蚀。此外,由于SIMOX是由氧注入工艺形成的BOX氧化层,表面硅还存在由氧离子注入带入的晶格损伤,随着顶层硅厚度的降低,SOI层电性能影响不断增大。2006年“Nature”上有文章称当顶层硅厚度减薄至10nm后,由于表面缺陷能级与SOI/BOX界面能级互相影响,会改变顶层硅的费米能级,促进其导电性,这种促进甚至会掩盖掺杂的效果[2]。

标准的SOI材料片有两个Si/SiO2界面:上界面和下界面。Si/SiO2界面缺陷主要表现在Si/SiO2界面粗糙不平整、存在界面态缺陷中心、位错/层错、微空隙缺陷、外部引入颗粒缺陷。对于SIMOX的SOI材料来说,由于高能氧离子注入造成的下界面自由隙硅原子增加,虽然自由隙硅原子会在体内再聚,但是增加速率大于再聚速率时,就会在下界面产生较大应力,当应力过大后就会通过形成位错等缺陷释放,从而在下界面处形成复杂的损伤层。这些损伤层会进一步变成各种金属吸收的缺陷中心[3]。金属杂质的存在会引起PN结漏电流增加,并降低SIMOX MOSFET的抗辐照能力。对于Bonded Smart-Cut的SOI材料片来说,由于下界面是由两片圆片键合而成,不可避免的会在键合过程中对下界面产生微空隙缺陷。由于两个键合表面不可能去除所有的外部沾污杂质,因此在键合后这些杂质也将被引入到下界面处。

BOX层缺陷主要是硅岛缺陷、针孔缺陷及杂质缺陷。前两种是SIMOX的SOI材料片最为常见的缺陷。由于SIMOX是由高能氧注入退火后形成的,如果在注入过程中氧离子的实际要求剂量偏低,就会在BOX中形成硅岛;如果在注入过程中部分区域被颗粒阻挡,该区域无法被注入到氧离子,因此也就无法形成BOX,这就是BOX中针孔缺陷形成的原因。对于Bonded Smart-Cut的SOI材料片,BOX是由热氧氧化生成,因此内部缺陷较少,主要是键合的下界面可能引入的杂质缺陷。

3 缺陷检测

SOI缺陷的检测可以分为两大类:可直接测试的表面及内部缺陷;间接的材料性能特征检测。

同体硅材料片的表面缺陷检测一样,光学检测是必不可缺的手段。由于SOI材料片的特殊性,光学检测会遇到复杂的光学干涉、反射和折射。光学检测完全依靠SOI材料片顶层Si/BOX/衬底的界面形态。

图4 光在Bulk和SOI圆片中路线示意图

美国Ibis提供的标准SOI技术文献中目前提及的缺陷分析仪为KLA公司生产的KLA Tencor 64XX系列以及KLA 213X系列,其中设定模式为SOI菜单定义,目前可侦测的缺陷最小分辨率约为0.2μm~0.25μm[4]。

图5 KLA机台侦测到的缺陷图

SOI材料性能主要是对顶层硅膜、界面态状况和BOX氧化层的表征进行评估。SOI材料特性的表征技术大致可分为三大类:第一类,测量手段先进、精确,但对材料有破坏性,如TEM。第二类,测试灵敏度稍低,但无破坏性,且可在数秒内完成检测,如用反射光谱法测量SOI材料顶层硅厚度。第三类,要检测的参数不能直接测量,需要通过器件的特性获得,如载流子寿命。以下为SOI材料的各种表征技术及其评价[5]。

顶层硅膜的表征主要是对顶层硅膜厚度均匀性、杂质含量、晶化程度和少子寿命评估。对于顶层硅膜厚度的测量,目前常见的椭圆偏振光谱法就能够满足要求。对于杂质含量的检测,目前常用的为二次离子质谱(SIMS)技术。由于SOI材料的制作过程中引入的一些损伤,破坏了顶层硅的晶体完整性,因而检验顶层硅的晶化程度非常重要。针对SOI材料的特点,主要有卢瑟福背散射谱(RBS)和紫外光(UV)反射谱两种方法。由于紫外光(UV)反射谱法具有无损伤、简单、快速的优点,可广泛应用于SOI材料片顶层硅结晶度和缺陷的监测,特别适用于工艺生产过程中的监测。该方法的原理为:利用半导体表面晶格损伤的失序引起光学常数的减少,特别是在光子能量大于能带间隙这一范围,在UV反射谱测量中观察到的反射系数随着表面损伤而减少,因而可以利用光反射技术来确定表面的损伤状况[6]。少数载流子(少子)寿命是与器件特性紧密相关的,因而可以利用器件特性的测量求得少数载流子寿命。目前使用较多的两种方法主要是二极管反向电流法和类Zerbest技术。二极管反向电流法适用于厚硅膜的少子寿命测量,类Zerbest技术适用于薄硅膜的少子寿命测量。

SOI界面态状况评估目前采用较为传统的C-V法,利用该技术测量整个SOI结果的电容,得到一个复杂的C-V曲线。

表1 SOI材料特性的一些表征技术

图6 SOI结构顶部金属电极与衬底之间的C-V准静态测量

在这个曲线上包括有硅膜的正界面(栅氧与硅膜的界面)、背界面(硅膜与埋氧层界面)和埋氧层-硅衬底的积累、耗尽和反型状态。对于这种复杂的结构,通过计算机模拟计算,将模拟结果与测试结果对比,从而可以估算出Si/SiO2界面处的电荷[7]。

4 结束语

由于SOI材料的特殊性,其在集成电路中的战略意义极其重大。目前世界各大半导体制造商均已经涉足SOI材料的研发,有的采用自主模式,有的与材料厂商共同开发。近年来上海新敖科技依托上海微系统信息研究所已经生产出我国自主的SIMOX SOI 100mm~150mm材料片,各项指标已经符合美国Ibis标准,这为我国SOI集成电路的发展提供了广阔前景。但是我国的SOI技术起步较晚,因此对SOI材料的缺陷检测及分析处于一个相对落后的阶段,这需要我们在实践中不断地摸索前进。

[1]Silicon-on-insulation: materials aspects and application[J].Solid-State Electr,2000,44:775.

[2]Zhang Pengpeng,Tevaarwerk Emma,Park Byoungnam,et al.Nature,2006,439(9):703.

[3]Skorupa W,Kreissig U,Hensel E,et al.Electron Lett,1984,20:426.

[4]Ibis Presentation on SOI Technology[S].

[5]黄如,张国艳,李映雪,张兴.SOI CMOS技术及其应用[M].北京:科学出版社,2005.

[6]P.T Zanzucchi and M.T.Surface damage and the option reflectance of single-crystal silicon[J].Duffy Applied Optics,1978 ,17(21):3 477.

[7]D.Flandre and F.Van De Wiele.A new analytical model for two-terminal MOS capacitor on SOI substrate[J].IEEE Electron Devices Letter ,1988,9(6):296.