超高速数字分幅相机中快门控制电路设计

朱寅非,吴云峰,唐 斌

(电子科技大学光电信息学院,成都 610051)

超高速数字分幅相机通过镜头后部的光学分幅系统分束,影像光束被均匀分为8 路,每一路投射到像增强器的光电阴极表面成像,快门控制电路产生极快脉冲选通开启和关闭像增强器[1-2],从而实现分幅高速摄影。像增强器从选通开启到关闭的时间就是曝光时间。超高速数字分幅相机的拍摄速度由选通像增强器的脉冲直接决定。因此,快门控制系统就是相机实现超高速摄影的核心模块。选用脉冲电路作为快门的控制系统,可以将电脉冲的优点转移到相机快门上,主要表现在:脉冲速度快,对应快门动作迅速;电路集成度高,占用空间小;系统受物理环境影响较小,稳定度高;脉冲承载能量少,功耗较低。当然脉冲电路也存在时序控制复杂的缺点。

1 超高速数字分幅相机快门电路系统设计方案

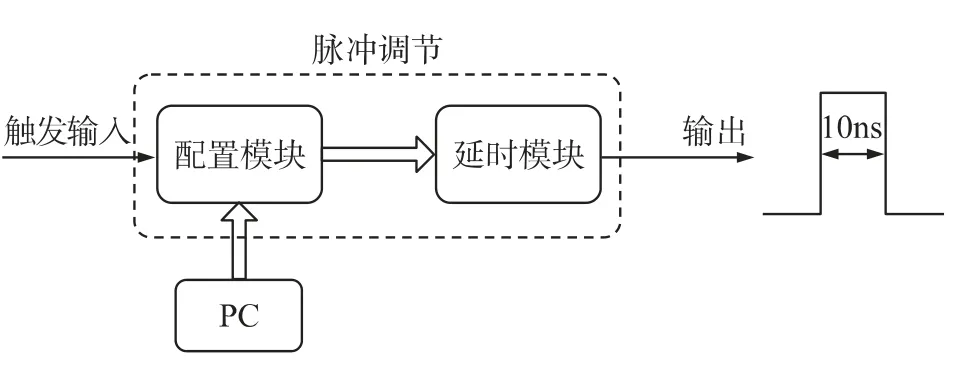

由于电路的最终输出是一个正脉冲,而在实际应用直接对高压信号进行幅值、脉宽调节并不方便,所以我们选择操作灵活的数字电路对触发信号进行延时处理,以获得合适宽度的低压脉冲。因此整个快门控制电路由配置模块和调节脉冲的延时电路两大块组成。如图1所示。

图1 快门控制电路系统框图

(1)输出脉冲幅值为+5 V;

(2)输出脉冲宽度最小达10 ns;

(3)脉冲宽度10 ns 可调;

(4)系统数据掉电不丢失,再次上电时电路功能不变;

(5)可实现与外部通信。

1.1 控制信号脉冲形成方案

在数字电路中,输入到输出经历的时间与其工作的系统时钟周期存在逻辑关系,可以通过定义不同的数字逻辑来改变延迟时间;模拟电路中,模拟器件会对传输信号产生固有延迟,这两种延迟时间可用来实现脉冲的延时。因此实现脉冲延时有两种方法即数字方法和模拟方法,我们称之为数字延时和模拟延时。下面将对这两种延时实现进行介绍。

护理3个月后,由医院自行设计问卷调查表,对患者饮食控制、运动锻炼、规律用药、定时血糖检测、足部护理、定期复诊等依从性进行调查;采取EQ-5D生活质量量表对患者护理前后行动能力、自理能力、日常生活能力、疼痛或不适、焦虑或抑郁等生活质量进行评分,该评分量表每项为100分,分数越高则患者生活质量越好。

(1)数字延时

数字延时通常通过计数器法和存储器法实现。

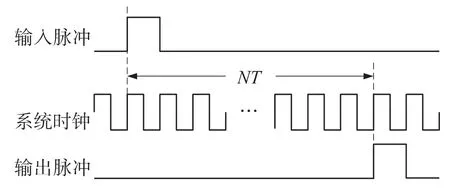

计数器延时的方法类似于分频的方法,当计数器计数到设定值(N)时,计数时间等于延迟时间(t),延时完成。延迟时间的运算表达式如下:

式(1)中T为计数器工作时钟周期,f为时钟频率。

例如若需延迟时长0.5μs,系统时钟为100 MHz,则由上式计算得设定值N=50。以加法器为例,首先将N=50 设置到计数器内,计数器清零等待计数,当需要延迟的脉冲信号到来时,以脉冲上升沿触发计数器开始计数,每经过一个系统时钟计数器加一,直到到达设定值50,停止计数并清零,在第51个系统时钟的上升沿输出一个与原始脉冲等脉宽的脉冲信号,即完成脉冲的延时,输出的延迟时间是0.5μs。如图2所示。

图2 计数器延时示意图

但在实际应用中受系统时钟频率的限制,达不到较高的延迟分辨力。另外计数器的计数长度也限制了最大延迟时间。

数字延时的第2种方法是存储器延时[3-4]。

存储器法延时是将需要延迟的脉冲信号进行采样,变成数据写入FIFO或双口RAM。写入FIFO 时先设置写入长度,写满写入长度后读出,则写入时间就是延迟时间,再通过控制FIFO 的触发点来实现输入数据的输出延时。

利用双口RAM 延时的方法也是对脉冲信号采样之后,将数据输入双口RAM,输出数据时,从读地址线到写地址所需的时钟就是延迟时间,所以延时可以通过设置读地址线和写地址线的差值来控制输出数据延时。

存储器法相对于计数器法,延迟时间不再受脉冲间隔时间影响,而且存储器容量较大,可以实现大范围的时间延迟。不过延时分辨力同样受系统工作频率限制。存储器法延时在时序控制上比计数器法要复杂,需要的系统资源也更多。所以,根据不同的延时要求选择合适的延时方法是很有必要的。

另外,要实现动态延时,则需要单片机或其他外部控制器与延时器配合使用,利用控制器将延迟值动态写入计数器或存储器。

(2)模拟延时

模拟延时主要是利用门传输延迟实现,逻辑门是集成电路的基本单元,因此模拟延时相对于数字延时具有更高的精度。将不同数量的逻辑门串联在一起即可获得不同的延迟时间,现在的模拟延时器正是采用这种方法,将多位锁存器控制的逻辑门延时线(Delay Line)封装到一起,组成高速可编程延时线芯片。多位锁存器相当于一个地址锁存器,向其中写入不同的值,即可选择串联逻辑门数目,获得不同的延时输出。如图3所示。

图3 延时线结构示意图

近年来随着半导体技术和声表面波技术SAW(Surface Acoustic Wave)的发展,相继出现了全硅延迟线和基于声表面波技术的固定和抽头式延迟线SAWTDL(SAW Tapped Delay Line)。例如SYNERGY公司生产的数控延时芯片SY100E195,MAXIM 公司生产的延时线芯片DS1021,Data Delay Device 公司生产的DDU75F,ADI 公司生产的AD9501 等[5]。这些延时线的延时分辨力能达到亚ns 级甚至ps 级,具有很高的精度,并且都可以通过可编程多位数控端口调整延迟时间。

综上所述,在搭建延时电路时,考虑到数字延时动态范围大、模拟延时精度高的特点,采用二者相结合的方式以达到延迟时长和精度要求,即脉冲经过数字延时来实现延时的粗调,经模拟延时来实现延时的细调。如图4所示。

图4 数字方法模拟方法结合延时

1.2 硬件电路设计与实现

考虑到脉冲延时电路对时序要求较高,逻辑运算量不大等特点,系统选择速度较快、适合小规模集成电路的CPLD(复杂可编程逻辑器件)作为数字逻辑电路部分的实现平台,利用CPLD 对延时信号进行预处理,并对多路模拟延时器件进行配置[6-7]。

因此,整个用来产生控制脉冲信号的动态高精度延时电路由单片机控制模块、CPLD 以及DS1021延时模块以及系统供电模块。

CPLD 延时电路的硬件电路设计主要包括延时模块、接口电路、系统时钟、供与电接地以及测试端口。下面给出脉冲延时电路具体设计图,如图5所示。

图5 CPLD 控制延时模块引脚配置

采用CPLD和DS1021模拟延时线芯片和逻辑门的配合使用,利用CPLD 配置模拟延时线线DS1021,这样做既可以发挥将延时线芯片0.25 ns的延时精度,又可以获得大范围的时间延迟,具有良好的延时效果。

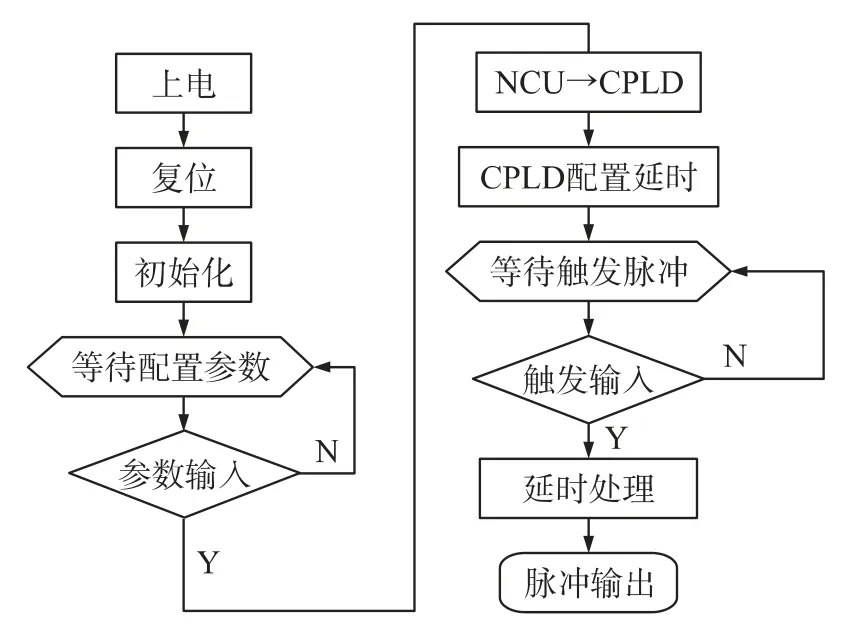

2 可编程脉冲延时发生器软件设计

对脉冲的延时处理通过数字延时和模拟延时相结合实现。由于CPLD 的高速特性,我们选用CPLD对延时信号进行预处理,并配置延时线芯片;由于单片机的易操控性,使用单片机向CPLD 发送延时数据,与PC 通信,通过人机交互界面实现计算机设定延时参数。上电后首先执行系统的复位操作并进行系统初始化,单片机通过RS232 接收PC 机发来的延时时间参数,当单片机接收到延时时间参数后进行数据的整理,单片机通过SPI 总线与CPLD 通信,将延时时间传送给CPLD,CPLD 通过SPI 总线配置DS1021 的模拟延时时间,配置成功后进行状态显示并等待外部触发脉冲,当外部触发到来时,首先通过CPLD 进行10 ns 分辨率的数字延时,数字延时结束后再通过DS1021 进行分辨率为0.25 ns 的数字延时,最后输出脉冲。软件工作流程如图6所示。

图6 延时电路系统总体流程图

3 系统实验结果与分析

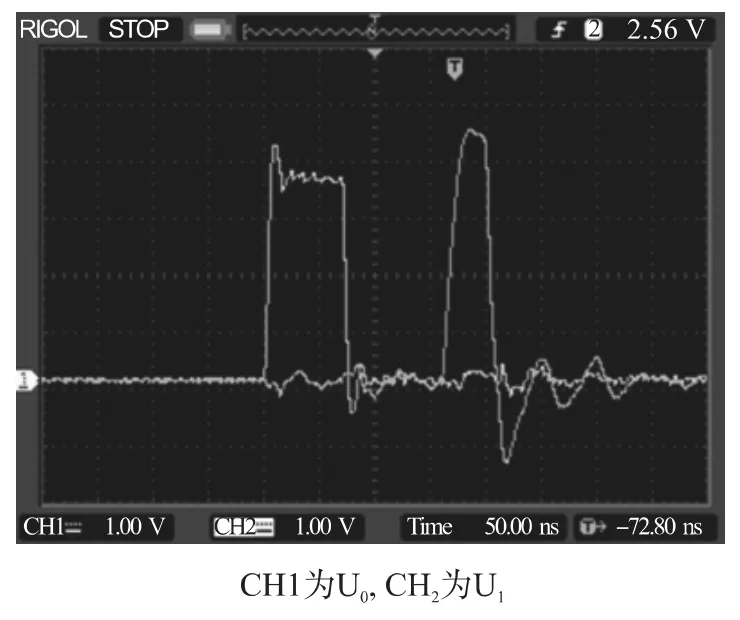

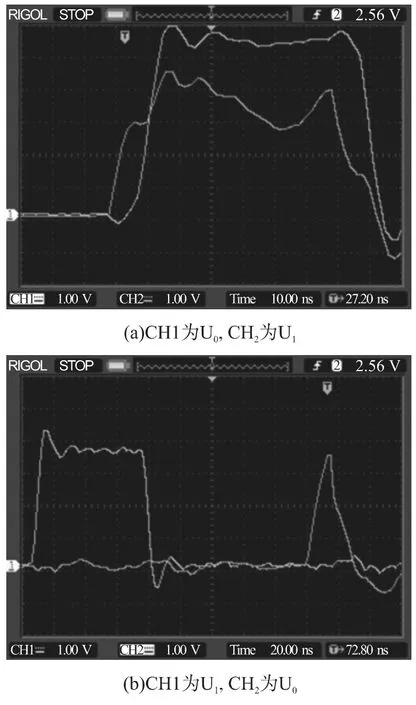

完成整个电路系统的硬件、软件设计之后,对系统进行测试和记录,并对实验结果进行分析。利用示波器的两个通道对原始脉冲和延时后的脉冲进行测量,我们得到了如下结果,如图7所示(原始脉冲为U0,延时后的脉冲为U1)。

图7 脉冲延时

通过向各延时芯片写入不同的延时设定值,可以实现脉冲延迟时间和脉冲宽度的调节,如图8所示。

图8(a)所示为单级DS1021 产生的最小延时,我们可以看到U1相对于U0的延迟为10 ns,测试结果与设计方案相符合。图8(b)中所示为通过调节获得的窄脉冲,脉冲中部宽度约为10 ns。波形质量与标准波形有一定差距,其中也有示波器的原因。

图8 最小延迟时间(a)和最小脉宽(b)

由以上测试结果可见,本设计实现脉冲延迟时间和脉冲宽度的调节,达到预期设计指标。但延时脉冲下降沿有振荡,经过多次测量分析,是由于示波器测试信号线阻抗不匹配引起的,阻抗匹配后该问题可以得到解决。

4 结论

本设计通过对快门系统的各项指标分析,结合传统分幅相机方案以及现代数字电路技术,设计了一种可获得超高速数字分幅相机所需的高速快门控制电路的应用方案。利用CPLD 技术和单片机控制技术,实现整个系统的控制和通信。CPLD 内部资源丰富,高速处理能力强,应用灵活性极大,为实现数据的高速处理、信号的精确传输以及多路外设控制提供了功能保证;单片机操作简单,应用广泛,为系统和外部通信提供了便利;利用模拟器件进行精确延时,将模拟延时线与数字锁存器封装到一起,实现可数控调节延迟时间功能,为进行脉冲信号时序的精确处理起到了关键作用。本设计实现了ns 级脉冲延时和ns 级脉宽可调,可靠性高,稳定性与抗干扰性强,具有很强的实用价值。

[1]彭小勋.超高速数字分幅相机中光学分幅系统的设计[D].成都:电子科技大学,2008,1-65.

[2]Sultanoff M.A 100,000,000-Frame-per-Second Camera[J].Review of Scientific Instruments,1950,21(7):653-656.

[3]王克家,周宝宇.用CPLD 实现可变延时芯片的设计[J].应用科技,2001,28(4):12-13.

[4]唐鹏,吴国安,马晖.基于FPGA和FIFO 的信号延时系统设计[J].航空电子技术,2009(2):61-64.

[5]钱卫明,阴泽杰,吴孝义.可编程延时芯片及其在系统时序控制中的应用[J].核电子学与探测技术,2000,20(4):305-307.

[6]孙国栋.超高速数字分幅相机驱动电路与图像采集系统设计[D].成都:电子科技大学,2009:1-67.

[7]Graham W Smith,David S George,David Harrison,et al.Ultrafast Imaging of Nanosecond Pulse x-Ray Simulators.Proc.SPIE,2008,7126(3):1-11.