适用于数字锁相环的快速建模方法*

陈 娟,陈 鑫

(1.南京工程高等职业学校电子工程系,南京 211135;2.南京航空航天大学电子信息工程学院,南京 210016)

最近几年,数字锁相环[1]广泛应用于嵌入式芯片的时钟产生电路。与传统的电荷泵锁相环相比,数字锁相环用时间-数字转换器替代了电荷泵[2],用数字滤波器替代了由电容组成的模拟滤波器[3],用数控振荡器取代了压控振荡器[4]。因此,在数字锁相环中,从时间-数字转换器[5]的输出到数控振荡器的输入,传递的都是数字信号,提高了信号对数字切换噪声的抗干扰能力。

但是,和模拟锁相环一样,数字锁相环在设计过程中,也需要对电路的结构进行仔细的仿真和验证。由于数字锁相环自身的特性,数字锁相环的结构非常多变[6-7]。如果在电路完成之后再基于晶体管级仿真[4],每次设计迭代的时间将会十分漫长。

为了能够快速建模并仿真,研究者提出了多种快速建模方案。文献[8]直接利用所编写的VHDL 代码对电路的数字模块进行仿真,并取得良好的精度。为了解决模拟模块的快速仿真问题,文献[9]对数控LC 振荡器系统进行了行为级建模。文献[10]对数控振荡器和时间数字转换器对了行为级建模,文献[11-12]基于S 域对锁相环电路进行了建模。

但是,目前尚未有对锁相环频率捕获过程进行快速高精度建模的方法。本文针对数字锁相环[13-14]数模电路混合的特点,数字模块直接用其可综合的Verilog 设计代码作为仿真输入文件,对于模拟模块则根据其仿真结果基于Verilog-A 进行行为级建模,最后利用Spectre Verilog模拟器进行了数模混合仿真。该仿真方法的特点在于建模速度快和仿真精度高。首先,数字模块直接用其设计代码进行系统仿真,不需要额外花费时间进行建模,并且仿真结果和实际结果基本一致。其次,Verilog-A 是专门用于模拟电路来的建模语言,利用该语言建模可以有效对模拟模块的各种电路特性进行建模。最终的锁相环频率捕获仿真结果也表明,该行为级仿真可以精确地对锁相环进行系统级的仿真,有效减少锁相环在设计过程中的迭代时间。

1 数字锁相环的行为级模型

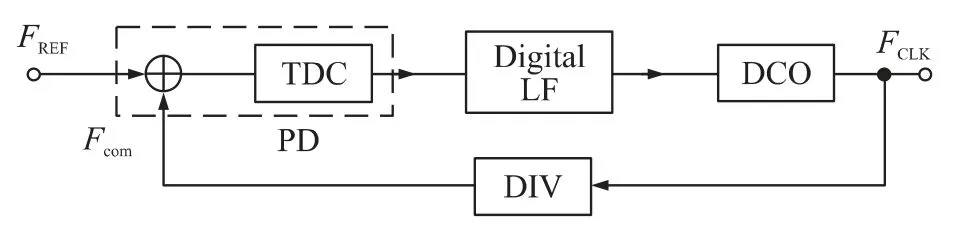

数字锁相环是数模混合电路,如图1所示,其电路结构主要包括:鉴相鉴频器(PFD)、时间-数字转换器(TDC)、数字滤波器(Digital LF)、数控振荡器(DCO)和时钟分频器(DIV)。其中,数控振荡器是模拟电路,它根据输入的控制字,输出高频时钟。其他模块都是数字电路。

图1 数字锁相环框图

数字锁相环的工作原理为:首先由鉴相鉴频器检测其参考时钟和分频时钟之间的相位差,产生与之相同宽度的脉冲信号。该脉冲信号经过时间-数字转换器,转换成数字信号,数字信号经过数字滤波器被滤去高频成分后,再送往数控振荡器,控制其振荡频率。数控振荡器输出的高频时钟经过时钟分频器分频后反馈到鉴相鉴频器,与参考时钟进行比较。

根据数字锁相环各个模块的特点,其中数控振荡器的行为级模型由Verilog-A 语言设计,而其它各模块的行为级模型均是由Verilog 语言设计完成。

1.1 鉴相鉴频器

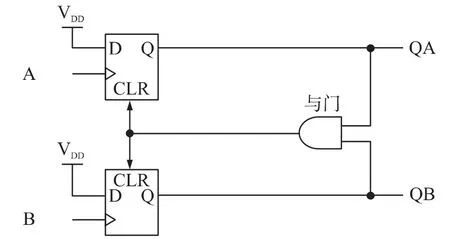

图2 PFD 的结构图

鉴相鉴频器[15]的结构图可见图2。它由两个边沿触发、带复位的D 触发器组成,触发器的D 输入端都接逻辑“1”。A和B 作为触发器的时钟。如果QA和QB 的起始值都为0 且A 由低变高,则QA输出高电平。接着若B 也由低变高,于是QB 也输出高电平,则与门使两个触发器复位。

根据PFD 的结构图,可以很容易完成PFD 的Verilog 设计,限于篇幅,在此不给出其Verilog 代码。

1.2 时间-数字转换器

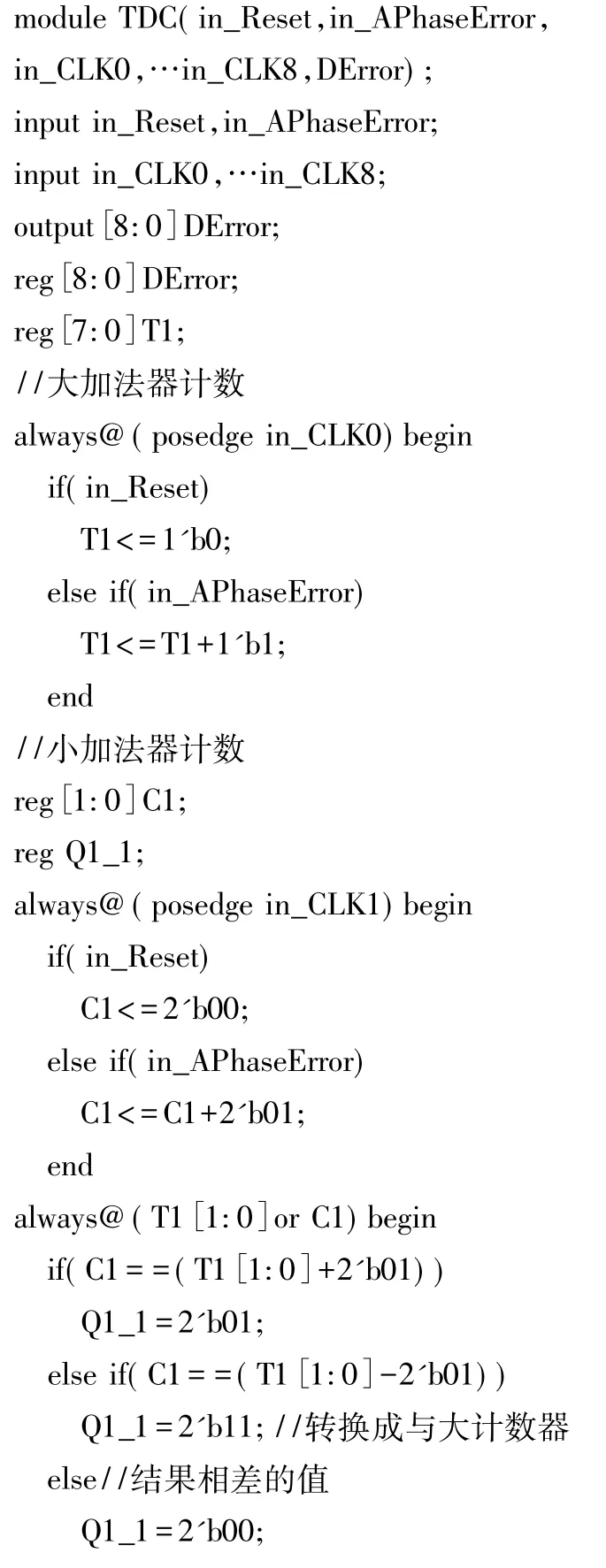

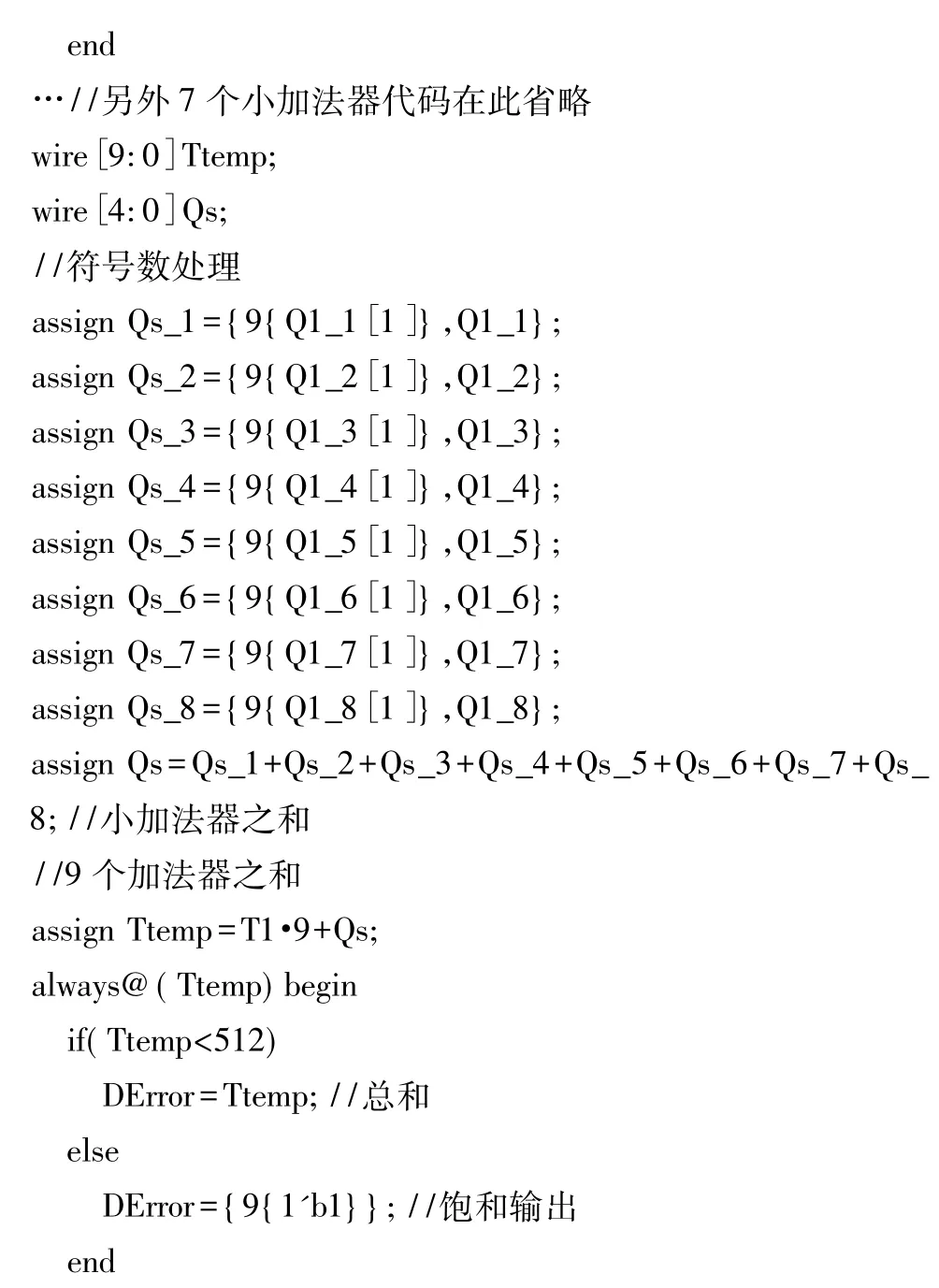

时间-数字转换器电路的作用是将PFD 输出的脉冲信号转换为数字信号。本文仿真的TDC 结构是由DCO 输出时钟驱动的计数器。假设环形DCO 的级数为9,那么DCO 可以产生9个不同相位的时钟。因为这9个不同相位时钟驱动的计数器计数结果最多只相差1。因此,可以用1个大计数器,8个小计数器共9个计数器组成一个精度很高的TDC 电路。大计数器用来保存实际的计数结果,小计数器用-1,0或者1 来表示和大计数器计数结果相差的情况。最后,TDC 统计的值为:大计数器的值乘以九,再加上所有小计数器的输出结果。主要代码如下:

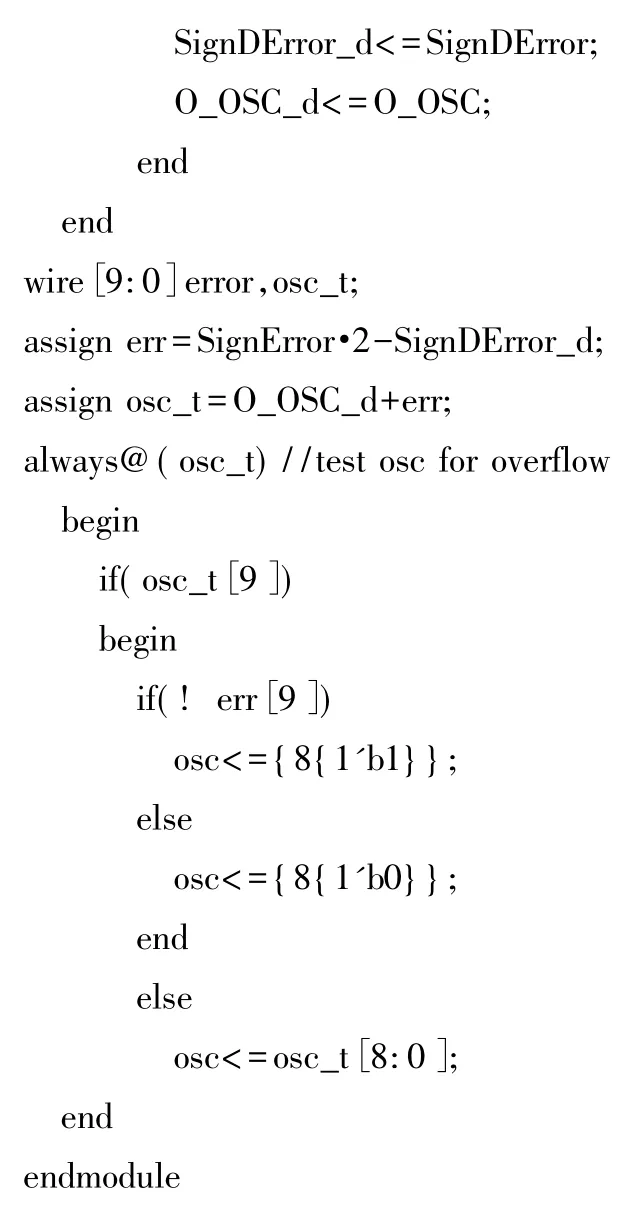

由于SpectreVerilog模拟器不支持Signed 的标识,因此,在Spectre 环境下编写Verilog 行为级模型时,需要自行处理符号位。

1.3 数字滤波器

TDC 产生的数字信号经过数字滤波器时,滤波器将滤除不需要的高频信号部分,作为振荡器的控制信号。用Verilog 语言描述该数字滤波器,仿真得到的结果与用电路图设计所得到的结果是相同的。

1.4 数控振荡器(DCO)

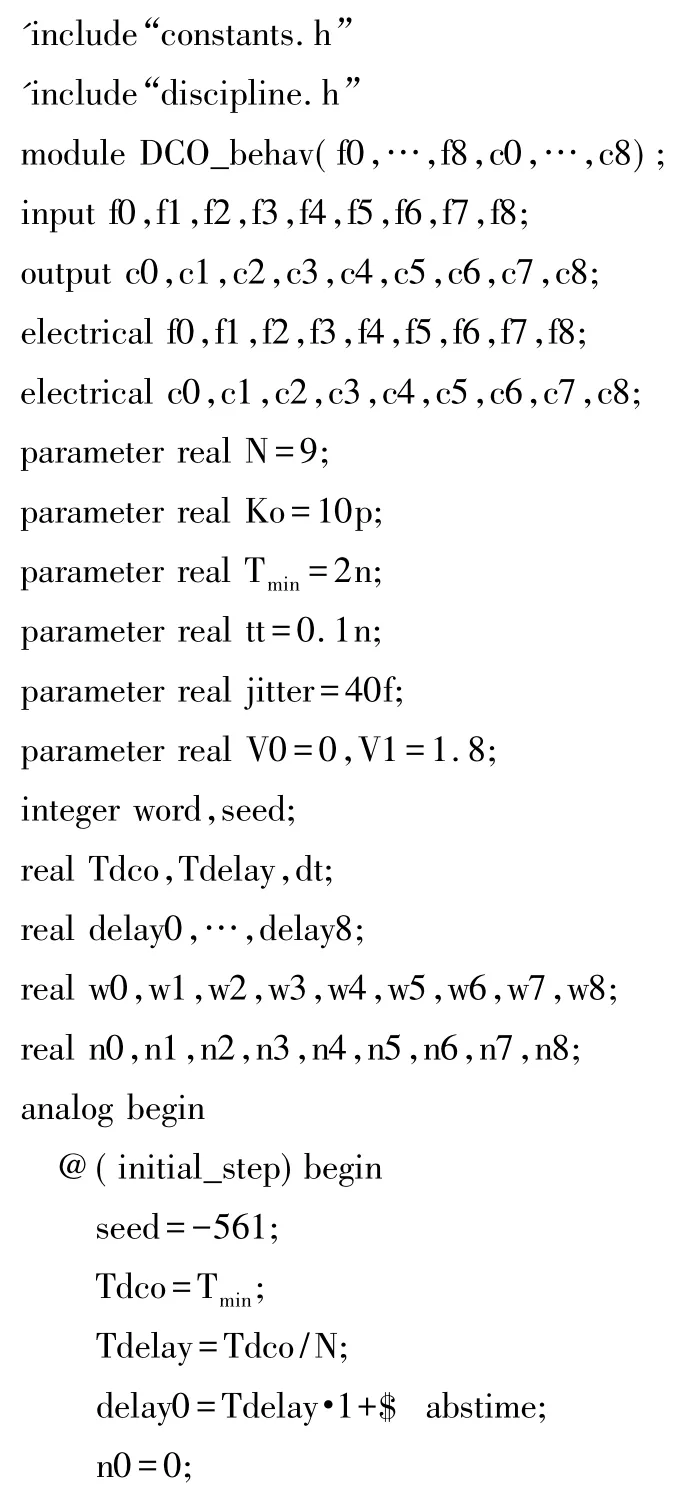

DCO 的行为级模型由Verilog-A 语言完成,这是因为DCO 的抖动特性可以通过Verilog-A 语言来仿真。主要的代码描述为:

Verilog-A和Verilog 的语法规则基本一致,但仍有一些不同之处,在建立行为级设计时需要注意:第1,Verilog-A 不支持总线定义。第2,Verilog-A不允许信号瞬变,因此需要利用transition 函数定义信号的上升下降时间。

2 数模混合仿真

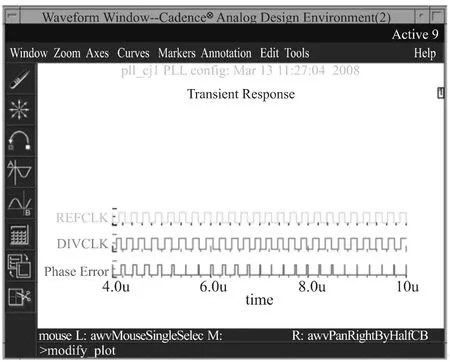

等到各个模块的行为级模型建立以后,在Virtuoso 中建立schematic 图,并用线将各个模块连接起来。此外,还需在mixed-signal opt.选项选择开关阈值电压。否则,会造成数模信号无法正确转换,使得整个仿真出现错误。图3 是锁相环仿真电路图,电路仿真时间是20μs,实际仿真时间744 s。该图的第1个信号是参考时钟信号REFCLK,第2个信号是分频时钟后的信号DIVCLK。第3个是鉴相鉴频器输出的相位差PhaseERRor。从第3个信号可以看出该锁相环相位逐渐锁定的过程,这和基于晶体管级的Spice 仿真结果是一致的。

图3 锁相环仿真电路图

3 总结

本文采用数模混合设计的方法,在Cadence 公司软件环境下,用Verilog-A和Verilog 两种硬件描述语言共同实现了锁相环电路的行为级模型的设计和仿真。采用数模混合的设计方法,可以有效缩短仿真时间,并减少仿真过程中的误差积累。通过在实际PLL 电路设计中的应用验证了该方法的可行性,值得推广。

[1]Wang Ping-Ying,Zhan Jing-Hong Conan,Chang Hsiang-Hui,et al.A Digital Intensive Fractional-N PLL and All-Digital Self-Calibration Schemes[J].IEEE Journal of Solid-State Circuits,2009,44(8):2182-2192.

[2]程知群,朱雪芳,周云芳.锁相环中克服非理想因素的鉴相器和电荷泵设计[J].电子器件,2010,33(4):442-446.

[3]林之恒,侯政雄,田秋霜,等.一种LC 型CMOS 射频带通滤波器及其自动调谐[J].电子器件,2010,33(6):691-695.

[4]张大会,张红强,王斐,等.2.06 GHz~3.43 GHz 自校准频率综合器设计[J].电子器件,2011,34(4):419-423.

[5]Volodymyr Kratyuk,Pavan Kumar Hanumolu,Kerem Ok,et al.A Digital PLL with a Stochastic Time-to-Digital Converter[J].IEEE Transcations on Circuits and SystemsⅠ,2009,56(8):1612-1621.

[6]Wu Chia-Tsun,Shen Wen-Chung,Wang Wei,et al.A Two-Cycle Lock-in Time ADPLL Design Based on a Frequency Estimation Algorithm[J].IEEE Trans.Circuits Syst.Ⅱ,2010,57(6):430-434.

[7]Xu Liangge,Kari Stadius,Jussi Ryynänen.An All-Digital PLL Frequency Synthesizer with an Improved Phase Digitization Approach and an Optimized Frequency Calibration Technique[J].IEEE Trans.Circuits Syst.I,2012,59(12):1-14.

[8]张喆元,朱劲.一种新型数字锁相环的建模和实现[J].电子技术研发,2010(6):19-21.

[9]周郭飞,苏厉,金德鹏,等.基于Verilog-A 数控LC 振荡器系统的行为级建模[J].集成电路设计与开发,2009,34(4):375-380.

[10]Ihor Harasymiv,Manfred Dietrich,Uwe Knöchel.Fast Mixed-Mode PLL Simulation Using Behavioral Baseband Models of Voltage-Controlled Oscillators and Frequency Dividers[C]//SM2ACD,2010:1-6.

[11]Jingchang Nan,Jianwei Ren,Mifang Cong,et al.Design of PLL Behavioral Model Based on the Verilog-A[C]//2011:380-383.

[12]田欢欢,张海英.全数字锁相环非数字模块仿真模型分析与建立[J].微电子学与计算机,2011,28(11):57-60.

[13]Olsson T,Nilsson P.A Digitally Controlled PLL for SoC Applications[J].IEEE Journal of Solid-State Circuits,2004,39(5):751-760.

[14]Mendel S,Vogel C,Da Dalt N,et al.A Phase-Domain All-Digital Phase-Locked Loop Architecture without Reference Clock Retiming[J].IEEE Trans.Circuits Syst.Ⅱ,Exp.Briefs,2009,56(11):860-864.

[15]Best R.Phase-Locked Loops-Design,Simulation,and Applications[M].5th Ed.,McGraw-Hill,2003.