基于FPGA的DDS信号获取与PI反馈算法设计

王存立 赵玉彬 张文志

1 (中国科学院上海应用物理研究所低温超导高频腔重点实验室 上海 201800)

2 (中国科学院研究生院 北京 100049)

世界上多个国家建成了质子或重离子治疗装置,以应对癌症对人类的威胁。质子和重离子静止质量较电子大很多,其加速过程中,随着粒子能量和速度的增加,高频腔工作腔压的幅度和频率也同步变化,即需实现腔压幅度和频率扫描,得进行算法设计,以实现高频腔压频率和幅度的同步渐变(Ramping);另外,为保证被加速的质子被俘获,稳定高频腔压信号的幅度和相位,使其分布在相稳区,须设计一套系统对其相位和幅度进行反馈控制[1]。因此,高稳定性、高精度的加速器高频低电平控制系统必不可少。

1 高频低电平控制总体框架

上海先进质子治疗装置加速器主体采用质子同步加速器,根据该加速器总体设计要求,高频系统须将质子能量从7.0 MeV加速至250 MeV,高频频率变化范围为 1.3–7.0 MHz,高频腔腔体峰峰电压值为2.0 kV。高频低电平控制(Low-Level RF Control)将采用基于DDS(Direct Digital Synthesizer),高速数模转换(DAC),模数转换(ADC)和现场可编程门阵列(FPGA)等硬件为基础的数字处理方式实现。

直接数字频率合成法的优点为:(1) 频率分辨率和切换速度高;(2) 频率切换时相位可保持连续;(3) 超宽的频率范围,能实现各种调制波和任意波形的产生;(4) 易于实现全数字化设计等。

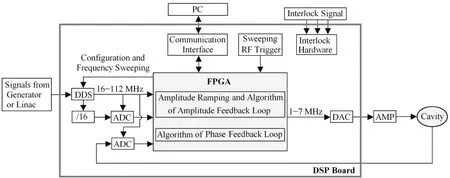

图1为低电平控制系统的硬件布局。其核心器件是FPGA Stratix II EP2S60芯片(美国Altera公司)和 AD9858芯片(美国 ADI公司),AD9858芯片用于实现直接数字频率合成(Direct Digital Synthesis),内部包含1GSPS的时钟速度,集成10位的数模转换器,相位噪声低至145 dBc/Hz@1 kHz,32位的可编程频率寄存器,SPI的串口控制接口。其工作模式为:单音(single tone)、频率扫描和睡眠模式,实验中主要用频率扫描工作模式。

图1 数字化高频低电平系统硬件总体布局Fig.1 Hardware overview of low-level RF system.

直接数字合成器(AD9858)实现频率的Ramping功能,当其接收到外部触发信号后,通过寻址功能实现不同频率的输出。在现场可编程门阵列中可实现各种算法,如幅度Ramping算法,幅度和相位反馈控制算法。

2 软件系统整体设计

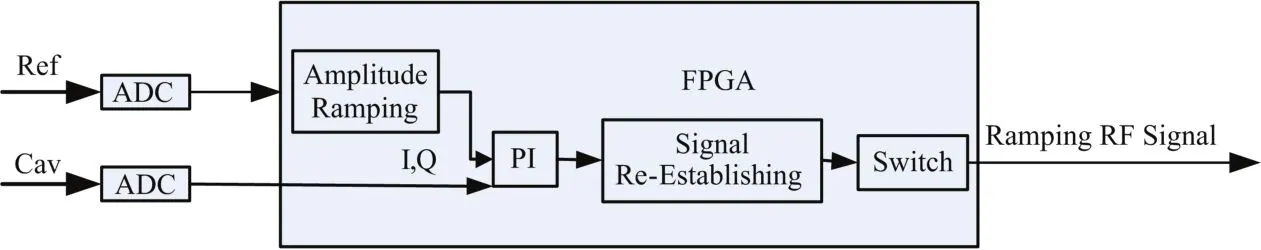

为实现数字化高频低电平控制系统,需进行模块设计:(1) AD9858配置,(2) FPGA算法设计,(3)数字信号处理板与外围设备通信设计。由图 2,经配置的AD9858工作在扫频模式(Ref信号),在FPGA内部实现幅度Ramping后与腔后反馈信号作比较,通过PI反馈算法实现输出信号随参考信号变化。

2.1 配置AD9858

AD9858扫频模式的配置主要控制以下寄存器:CFR(Control function register,控制功能寄存器)、FTW(Frequency tuning word,频率控制字)、DFTW(Delta frequency tuning word,步进频率控制字)和DFRRW(Delta frequency ramping rate word)。

图2 系统设计方案Fig.2 System design scheme.

2.1.1 设计指标

扫频范围1–7 MHz,扫频步长10 Hz,扫频周期时长0.5 s。

2.1.2 寄存器参数的计算[2]

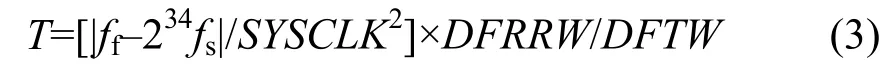

设扫频状态输出起始频率为fs,终止频率为ff,步进频率为Δf,线性调频信号扫频时宽为T,系统参考时钟频率为SYSCLK,则频率控制字为:

步进频率由下式决定:

用DFRRW表征扫频周期,其值由式(3)决定:

2.1.3 算法设计与硬件实现

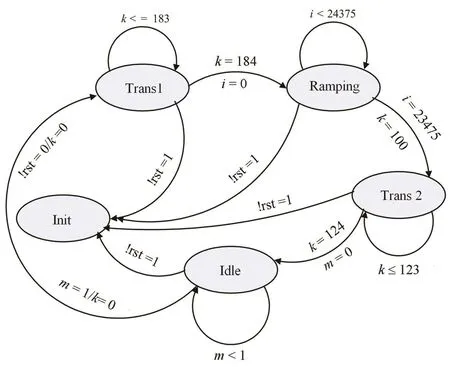

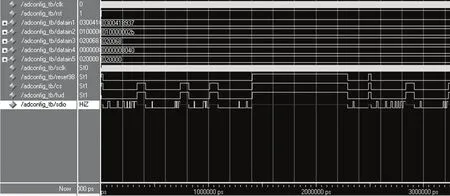

在配置AD9858实现扫频时,采用Verilog HDL作为硬件描述语言,通过有限状态机编码在ModelSim SE和Altera Quartus II 平台上进行时序仿真[3–5]。状态机编码设计中状态转换图如图3,在Modelsim SE平台上进行时序仿真得到的结果如图4所示。

图3 有限状态机状态转换图Fig.3 State transformation graph of finite state machine.

图4 AD9858扫频配置时序仿真Fig.4 Timing simulation of frequency sweeping configuration.

由图4,输入参数datain1为FTW,地址为0X03,参数的前8位为地址位,即03,后面32位为根据以上公式计算的32位二进制数据(下同);datain2为DFTW,datain3和datain5为DFRRW,其中datain3为扫频过程中的DFRRW值,当到达终止频率后,datain5写入寄存器,将DFRRW置零,停止扫频。输出信号部分,sclk为配置AD9858时的串行时钟,在算法设计中,该时钟的上升沿有效;reset98信号输出到IORESET,低电平有效;cs(chip select)为片选信号,低电平有效;fud (frequency update)信号的功能为:在其上升沿到来时,将数据由AD9858内部buffer写到其内核中。

将FTW、DFTW、DFRRW和CFR参数值分别写入后,reset98将IORESET置为高电平,cs和fud也变为高电平,然后开始计数,AD9858开始扫频,在频率到达终止频率即扫频时宽达到设计指标时,将DFRRW寄存器(地址为0X02)置零,停止扫频,并同时计数,下个周期如此循环往复,从而实现AD9858扫频模式配置。

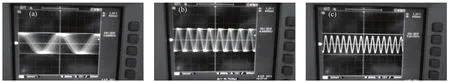

实验采用FPGA板卡和AD公司的AD9858作为核心器件,配有外围电路和稳压电源、信号发生器、示波器、滤波器等外围设备,编写Verilog HDL代码对AD9858进行扫频模式配置后,将代码下载到FPGA,在示波器上即可得到扫频输出波形如图5。

图5 扫频输出波形 (a)扫频起始频率1 MHz,(b)扫频至4 MHz,(c)扫频至终止频率7 MHzFig.5 Output waveforms of the frequency sweeping mode.(a) Starting frequency of 1 MHz, (b) Sweeping to 4 MHz, (c) Sweeping to the final frequency of 7 MHz

2.2 PI反馈控制

加速器要求不同频率下均有稳定度高的高频加速电压,若扫频输出不能跟踪高频腔的频率,将会产生失谐,引起高频电压的降低和高频信号相位的漂移,造成质子束流损失,严重时会造成高频发射机与高频腔体间的不匹配,使高频反射功率较大,高频功率无法传输到高频腔,而向其他薄弱环节反射,造成高频功率源产生自激振荡,甚至危及损坏。若腔体负载与高频功率发射机不匹配,亦导致高频腔体内产生电晕。因此,需通过反馈控制算法使扫频输出跟踪高频腔的频率。

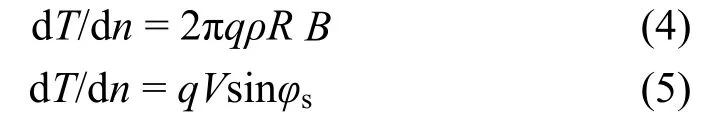

另外,RF接收相区的大小和加速效率均与同步相位相关,同步相位越大,加速效率越高,但接收相区越小;反之,同步相位小,加速效率低而接收相区大。另一方面,接收相区的大小还与所采用的RF电压有关。在RF加速过程中,应保持质子束流能量变化速率与磁场的变化率相对应,而能量的增益是从RF中获得的,即:

式中,V为加速器中所有加速腔的总电压,Bg为主导磁场随时间的变化率,ρ为在磁铁中的曲率半径,T为粒子动能,q为粒子的电荷,R为加速器的平均半径,φs为同步粒子相对RF腔的相位。

由图2,Cav信号为从高频腔取回的信号,经ADC后进入FPGA进行数字IQ解调数字化成Ifdb和Qfdb,分别与Ref参考信号数字化后的IRef和QRef经数字PI反馈算法处理,将信号恢复后送出FPGA,经DAC后即可得Ramping的高频信号,从而实现信号的 PI反馈控制。由此可见,PI反馈系统对稳定信号幅度和相位具有不可替代的作用,设计稳定可靠的数字 PI反馈系统对加速器高频腔低电平控制至关重要。

2.2.1 PI反馈控制理论[6]

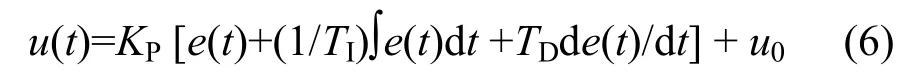

控制理论中,按偏差的比例(P)、积分(I)和微分(D)进行控制的控制器称为PID控制器,其控制规律表达式为:

其中,u(t)为调节器的输出信号;e(t)为调节器的偏差信号,等于给定值与测量值之差;KP为比例系数;TI为积分时间;TD为微分时间;u0为控制常量;KP/TI为积分系数;KP/TD为微分系数。

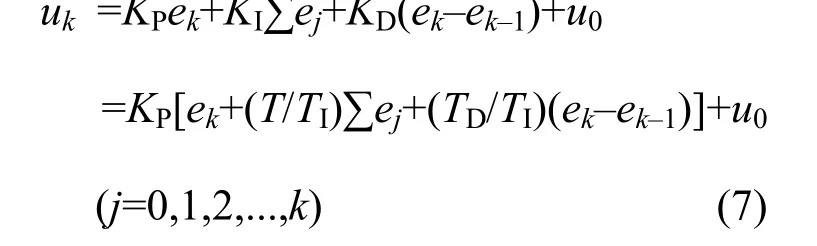

在数字PID控制系统中,以求和代替积分,差分代替微分,得到离散PID控制表达式:

式中,k为采样信号,k=0,1,2,…;u k为第k次采样时刻的计算机输出值;e k为第k次采样时刻输入的偏差值;ek−1为第k–1 次采样时刻输入的偏差值;KI为积分系数;KD为微分系数;u0为开始进行PID 控制时的原始初值(应为前一次的给定值)。

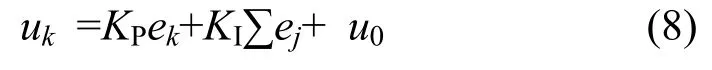

若采样周期取得足够小,则以上近似计算可获得精确结果,离散控制过程与连续控制过程十分接近。由于微分作用对输入信号的噪声很敏感,因此,在算法设计中采用数字PI算法,其离散表达式为:

2.2.2 数字PI反馈算法设计

由于比例控制可实现对偏差的快速响应,积分控制可消除静差,因而数字PI控制系统中,当高频腔压信号的幅度和相位与参考信号间发生偏离时,通过此系统可将比例与积分控制结合起来,在消除静差的同时加快对偏差的响应,以实现高频腔压信号快速准确地跟踪参考信号,使质子束流被俘获。

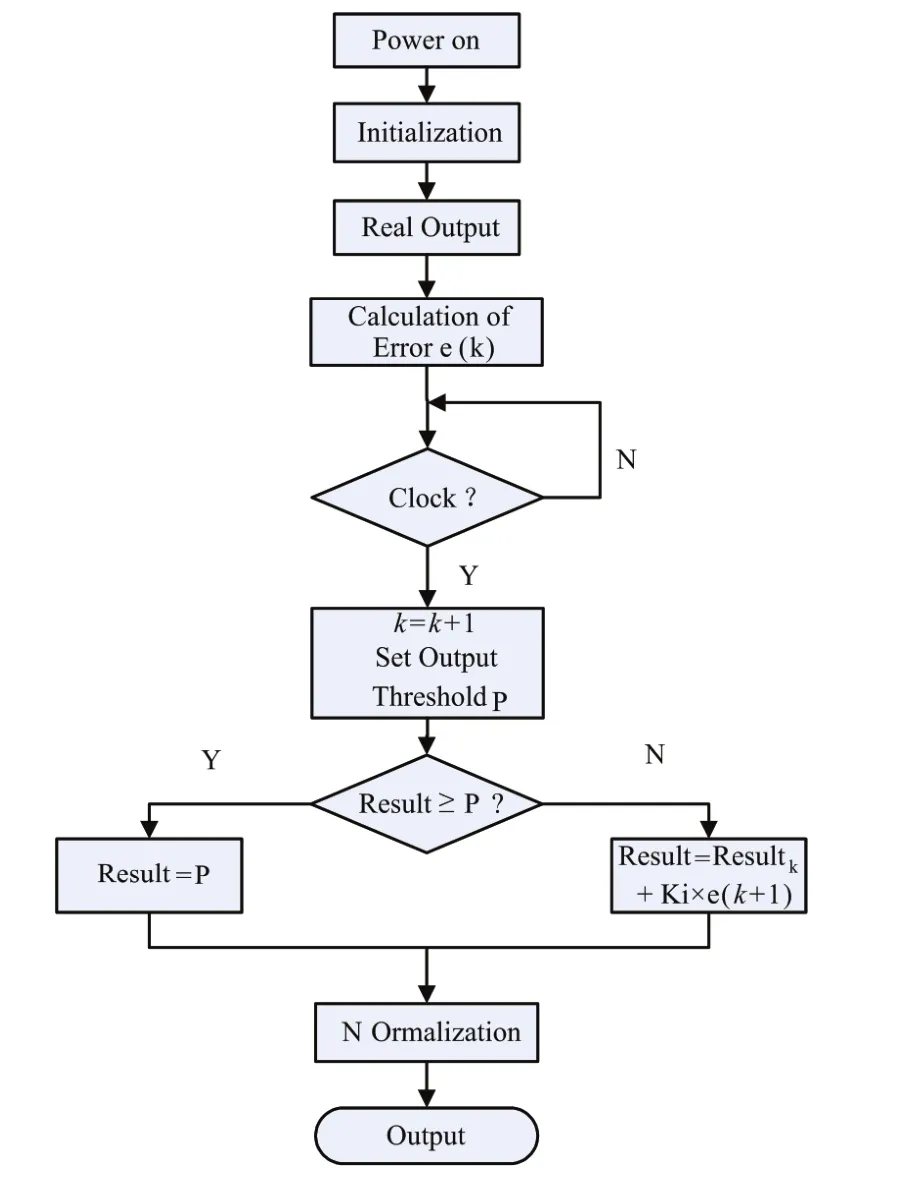

由于在FPGA内部不支持浮点运算,故在设定KP和KI时,需采用二进制整型数据对KP和KI归一化处理,在Verilog代码中通过截取n位二进制数据的高n-m位近似将该二进制数代表的十进制数缩小2m倍,算法设计流程如图6所示。

图6 PI算法流程图Fig.6 The flow chart of PI algorithm.

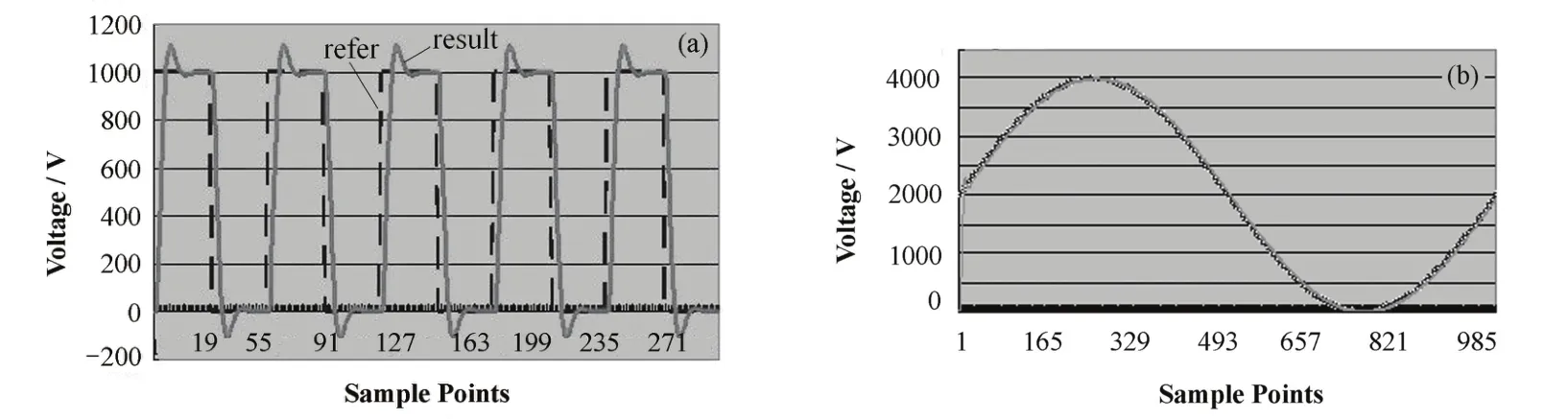

设计中,分别设定refer (参考信号)为幅度1000 V 的方波脉冲信号和 refer=2000×sin(2×pi×n/1024)+2000 (单位V)的正弦信号,先为refer信号定制一个ROM存储器(在一个周期内均匀取点个数1024个),然后作为反馈系统的输入在Quartus II下进行时序仿真,将反馈结果result数据提取后与refer信号作图,得到的数据波形如图7。

图 7中,refer为参考信号波形,result为经Verilog HDL代码编写的PI控制算法在Quartus II平台下时序仿真的数据波形。当refer为方波脉冲信号时,在PI反馈算法控制下,反馈输出信号幅度从0立即向refer逼近,同时,相位也跟踪参考信号,待输出信号幅值和相位接近参考信号后,其波形便跟踪参考信号波形变化;当输入参考信号为正弦信号时,由于正弦波形的幅度和相位变化较方波变化缓慢,通过PI算法比较,输出信号的幅值迅速向参考信号逼近,待逼近信号的幅值和相位后,其幅相便随输入参考信号变化。合理选择比例系数KP和积分系数KI,便可实现波形幅度和相位随参考信号变化,从而实现系统信号幅度和相位的反馈控制。

图7 PI反馈控制输出 (a) refer为方波波形,(b) refer为正弦波形Fig.7 Waveform output of PI feedback control with the refer being square (a) and sine (b) wave forms.

3 结语

质子治疗加速器高频低电平系统对加速器高频腔的工作状态具有不可或缺的作用。在配置AD9858实现频率Ramping的设计中,扫频范围设定为1–7 MHz,在接收到触发信号后频率和幅度同时进行扫描,当停止触发后,频率和幅度均停止扫描,回到初始状态。实验中通过设计Verilog代码,实现了扫频模式配置。在PI反馈控制算法设计中,通过调整比例系数与积分系数可控制 PI反馈的精度。设计中需对比例与微分参数作归一化处理,以满足FPGA对数据精度的要求。经配置后的AD9858

输出的扫频信号在FPGA内部经幅度Ramping算法后作为参考信号和高频腔后反馈信号作幅度和相位反馈的PI算法,进而使高频腔压信号随参考信号变化,实现高频腔的低电平控制。

1 徐建铭. 加速器原理(修订版)[M]. 北京: 科学出版社,1981: 296–304, 373–376 XU Jianming. Principles of accelerator (Revision)[M].Beijing: Science Press, 1981: 296–304, 373–376

2 Analog Devices Inc. 1GSPS direct digital synthesizer AD9858[Z]. www. analog. com, 2003

3 夏宇闻. Verilog 数字系统设计教程[M]. 第2版. 北京:北京航空航天大学出版社, 2008: 166–175 XIA Yuwen. Verilog digital system design tutorial[M].Second edition. Beijing: Beihang University Press, 2008:166–175

4 王 诚, 蔡海宁, 吴继华. Altera FPGA/CPLD设计[M] .第2版. 北京: 人民邮电出版社, 2011: 106–115 WANG Cheng, CAI Haining, WU Jihua. Altera FPGA /CPLD design[M]. Second edition. Beijing: Posts and Telecom Press, 2011: 106–115

5 Steve Kilts. Advanced FPGA design: architecture,implementation, and optimization[M]. USA: Wiley-IEEE press, 2007: 69–75

6 方康玲. 过程控制系统[M]. 第2版. 武汉: 武汉理工大学出版社, 2007: 69–101 FANG Kangling. Process control system[M]. Second edition. Wuhan: Wuhan University of Technology Press,2007: 69–101