基于降斑处理的SAR图像实时压缩系统

李 涛,田 松,许悦雷,郭 忠

(1.空军工程大学航空航天工程学院,陕西 西安 710038;2.泰山医学院,山东 泰安 271000)

合成孔径雷达(Synthetic Aperture Radar)是一种高分辨力的微波成像雷达,在军事和民用等方面都有广泛的应用。SAR图像是机载或星载的SAR对地面的探测成像,图像数据量高、尺寸大,如此大的数据量将导致网络实时传输效率的降低和庞大的在线存储需要。所以对SAR图像进行有效的压缩编码,降低数据量,以利于存储和实时传输成为SAR图像研究的焦点。

SAR图像中含有丰富的纹理信息和大量的均匀区域,且图像灰度值动态范围大。因此采用基于小波变换的JPEG2000编码[1]与采用其他编码方法相比,更具优势。但SAR图像具有的相干斑(Speckle)噪声会严重影响图像的质量,增加图像识别难度、减小相邻像素间相关性,导致SAR图像压缩效率降低[2]。因此,在进行SAR图像压缩时,先对图像进行降斑处理,抑制相干斑噪声,可增强图像像素间相关性,提高图像可压缩性,使重建图像更好地反映原始图像信息。

本文设计实现了SAR图像压缩系统,用于完成SAR图像数据的实时压缩任务,是SAR成像侦察系统的组成部分。设计中系统采用FPGA和ADV212编解码芯片,利用FPGA和空域增强Lee算法[3]实现图像降斑预处理,实现高压缩比情况下对图像细节的有效保留和压缩数据与通信信道间的高速传输,同时也达到了很好的实时性要求。

1 系统总体设计

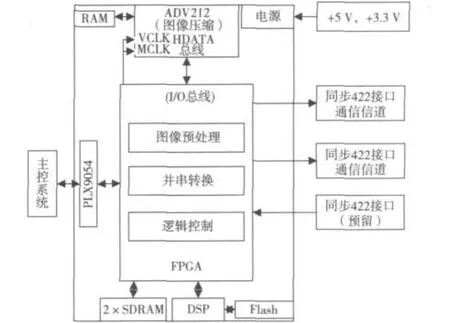

系统框架如图1所示。系统中核心的芯片主要包括ADV212,FPGA,DSP及配置电路芯片,以PMC单板形式实现。主要有PCI桥路、图像预处理、图像压缩、并串转换和逻辑控制5个模块,其中逻辑控制模块主要实现对数据流的吞吐管理和接口控制等。

图1 SAR图像数据压缩系统

来自主控系统的SAR图像数据,经过PCI桥路写入FPGA内部RAM缓存;在逻辑控制模块控制下,进入图像预处理模块进行降斑处理,后通过FPGA的I/O总线和压缩模块核心ADV212的HDATA总线,将数据送入ADV212内部,进行JPEG2000编码,产生*.jp2格式码流,压缩得到的码流经FPGA内部FIFO缓存和并串转换模块进行同步输出到串口信道,最后通过高速RS-422送至通信系统。

DSP主要配置ADV212内直接和间接寄存器,同时设置ADV212的编码参数,并加载ADV212的固件(Firmware,编码模式所需),DSP对ADV212的操作需要FPGA的总线切换控制。

由于数据缓存和暂存需大量空间,所以对FPGA的存储空间用SDRAM进行扩展。为了以后对系统功能进行拓展,进一步开发通过外界串口信号对系统进行指令控制,实现数据交互,系统在设计时预留了一路同步RS-422接口。

2 系统外围电路设计[4-6]

考虑到数据传输对带宽的要求高,系统与主控的通信桥路设计采用PLX9054芯片。该芯片是PLX公司生产的一种性价比很高的PCI桥路芯片,作为一种接口芯片,数据可在PCI总线和LOCAL总线之间传递,支持DMA传输。利用PLX9054可降低PCI总线的复杂性,完成数据的顺利传输。PCI桥路接收主控的图像数据,1帧图像数据的典型有效像素点为4096×4096个,每个像素输出精度为8位,图像帧的速率为6 s/幅,所以要采用32位总线宽度传输,时钟为33 MHz,接收的图像数据存储至RAM中进行缓存。

整个系统需要5 V和3.3 V的电源。系统的5 V电源由外部提供,TI公司的TPS767D301芯片通过转换提供3.3 V电源,同时该芯片也可产生系统复位信号。

SDRAM选用三星公司的K4S561632E,来配置FPGA的存储单元,其存储容量为4×4 M×16 bit。参照数据手册,FPGA分配 给 SDRAM 39个 I/O。DSP选 用TMS320F2812完成对ADV212的初始化,并扩展Flash芯片来存储固件程序和配置数据。

3 基于FPGA的功能模块[7]

考虑成本和设计需要,FPGA选用Altera公司的CycloneⅢ系列 EP4C115器件,其具有528个用户 I/O、114480个可用逻辑单元、255个嵌入式乘法器单元和4个锁相环,其内存资源丰富、速度等级高,完全可满足功能需求。FPGA外挂了PLX9054,ADV212,2×SDRAM和DSP,主要实现数据流管理、图像预处理、并串转换等功能,同时通过对DSP控制来完成ADV212的初始化。

3.1 数据流管理

要实现系统数据高速协同工作,通过逻辑控制模块管理数据流起着重要的作用。该模块要对系统的各芯片接口进行控制,同时还要控制数据高速接收、分块缓存、乒乓读写、流水线处理和管理ADV212数据。

为了完成数据的无缝缓存与处理,提高数据处理速度,系统采用流水线式并行处理。采用流水线结构在提高系统处理速度的同时会造成输出延迟,且还需更多的寄存资源,因为FPGA中每个逻辑单元都有寄存器,所以可有效支撑流水线设计。

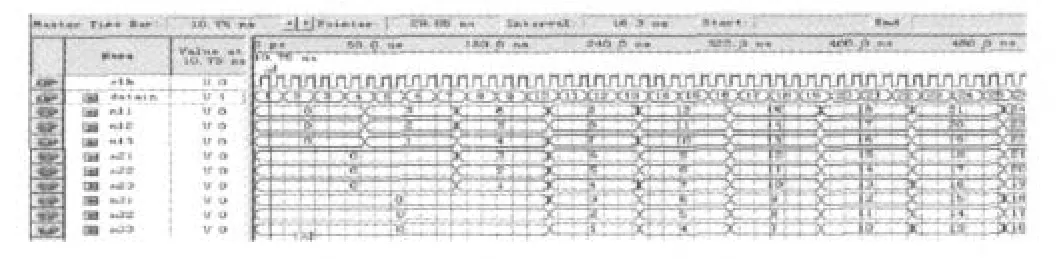

数据流的吞吐采用分块缓存读取的方式。对每一幅图像的数据进行处理之前,FPGA首先读取存储在缓存区的数据。每次处理的数据都是一个数据块中的多个数据,但FPGA一个周期只读一个数据。这样数据的串入并出就显得很重要。数据块的选取按照从上到下、从左往右的顺序进行。如3×3的处理模板,在进行一次计算时,FPGA首先从缓存区连续先后地读入3个数据,然后将这3个数据和保留在模块中其他6个数据一起输出到后续的模块。数据分块吞吐测试如图2所示。

图2 数据分块吞吐测试(截图)

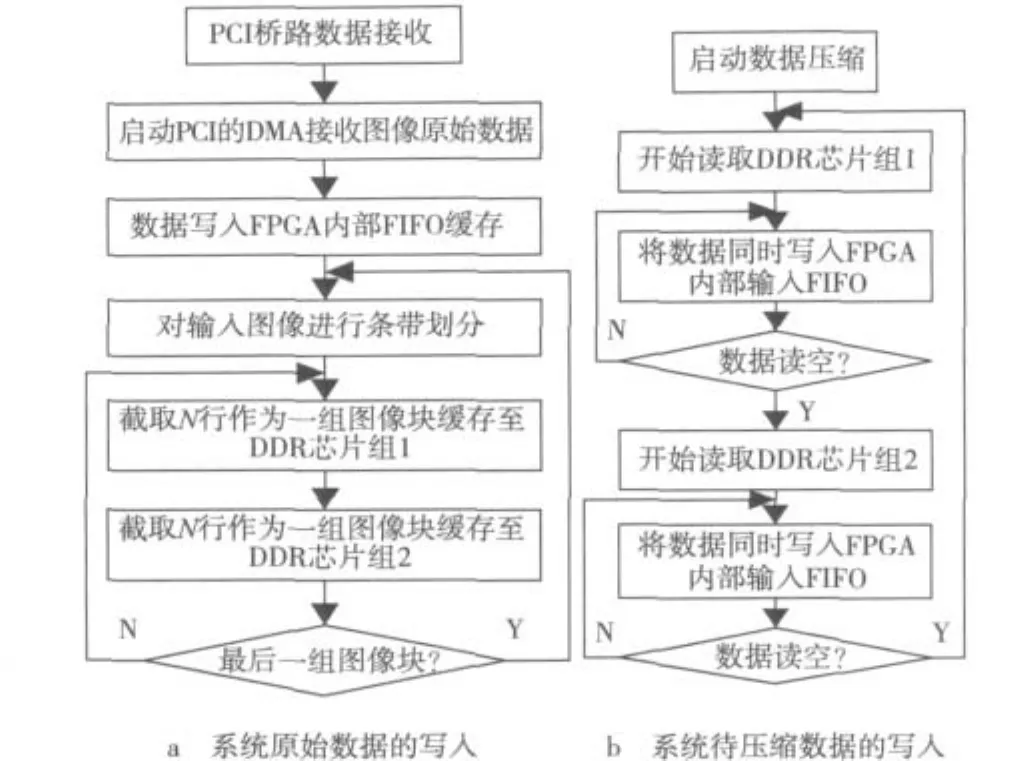

在控制输入待压缩数据时,按照图像的大小和传输特性,将图像进行分块,传输过来的数据被分成若干批次处理,每个批次分成4个图像块,依次送给ADV212压缩。在实现时,将4个图像块通过乒乓读写模式,实现同时缓存和压缩。

数据经ADV212的HDATA总线吞吐。获取ADV212产生的压缩码流时,系统通过设置ADV内部编码FIFO的门限值来实现码流的读取,当编码FIFO中的码流达到设定门限时,中断引脚IRQ产生中断信号与FPGA内部数据读取模块相连,一旦触发FPGA即启动读取编码FIFO中产生的码流。发送原始数据给ADV212的过程与获取压缩码流相似。

压缩码流写入FPGA内部的输出FIFO后,输出FIFO数据经并串转换模块转换成同步串口数据直接发送至信道。系统主要数据传输流程如图3所示。

图3 系统主要数据传输流程

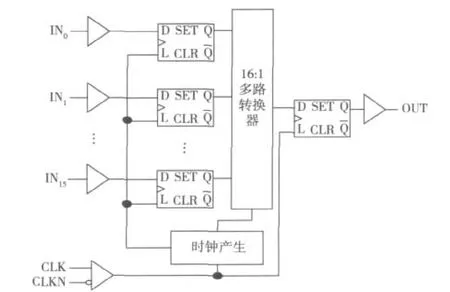

3.2 并串转换

系统内为16 bit的并行数据。为了提高信道传输速率,满足RS-422串口传输要求,在压缩码流输出前要将并行的16 bit数据转换为串行数据,转换过程在逻辑控制模块的控制下也采用了分块传输、分块转换的方法。并串转换采用双路恒流结构[8],在一定程度上有效地解决了电路工作速度的瓶颈问题,可提高集成度、降低功耗,其工作频率可达4 GHz以上。图4是一个16 bit并串转换接口电路的双路恒流结构工作原理图。

图4 16 bit并串转换电路原理图

3.3 图像降斑预处理

考虑FPGA的数据处理速度、滤波算法的稳定性和有效性,图像预处理采用空域滤波中成熟的经典增强Lee算法。该算法可实现高压缩比情况下对图像细节的有效保留,同时达到很好的实时性要求,还可改善SAR图像的相关性,有助于提高压缩性能。预处理算法通过FPGA编程实现,在不需要时可旁路。

在SAR图像相干斑噪声为乘性噪声[9]的条件下,图像数据可表示为

式中:I是观察到的图像;R是未被相干斑污染的数据;F是衰落过程所引起的相干斑噪声。

经增强Lee滤波后的表示为

图5 增强Lee滤波FPGA实现流程图

在进行图像数据压缩前,通过FPGA的预处理模块进行增强Lee滤波可很好地抑制SAR图像的相干斑,而且通过流水处理,在保证运算精度的同时,提高了在硬件上实现的实时性。经实际测试在FPGA资源使用上,增强Lee滤波占用6%的逻辑单元、12439 bit的内部存储器、20个DSP单元。在滤波过程中不会给系统的整体速度和资源分配带来太大影响。

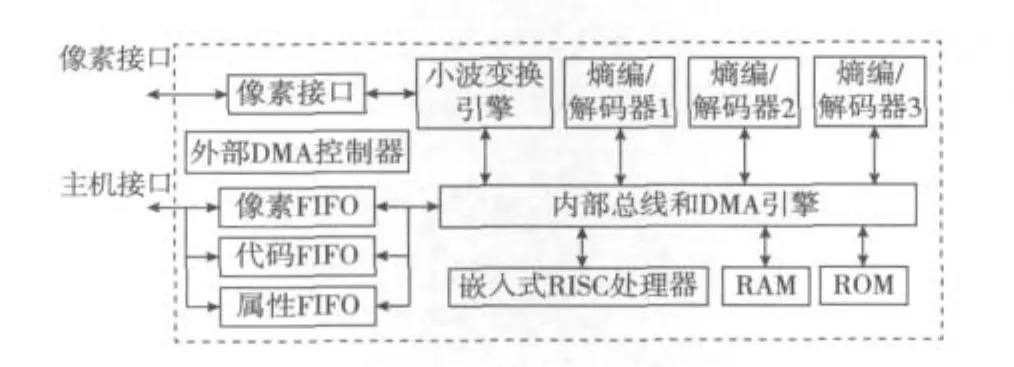

4 基于ADV212的图像压缩模块

ADV212[11]是ADI公司推出的一款用于视频和高带宽静止图像压缩的单片JPEG2000编解码芯片,具有可靠性好、配置灵活、支持格式多样等优点。考虑系统的稳定性,图像压缩采用成熟的ADV212专用芯片实现,相对软件形式实现压缩,利用ADV212可减少设计复杂度,将主要工作集中在外围电路和软件设计上。ADV212内部功能框图如图6所示。

图6 ADV212功能图

ADV212可通过异步SRAM方式、DMA访问方式或码流方式直接和大多数主机处理器及ASIC器件相连接,提供有16位和32位控制总线及8,16和32位数据传输总线。FPGA通过I/O总线和ADV212的HDATA总线连接,通过DSP来配置、控制功能以及直接传输压缩后的数据流,也可以在某种模式下传送解压的数据,在某些格式中还可用作未压缩数据流的传输。ADV212的工作模式是在初始化固件中通过HDATA总线进行写寄存器的状态字来设定,访问方式为异步RAM访问方式。图像压缩倍数的选择可以进行配置,主要由FPGA通过DSP来实现。

5 软件设计

系统软件设计集中在FPGA和DSP上,主要有2个部分:1)FPGA,TMS320F2812,ADV212的初始化;2)图像预处理、并串转换及逻辑控制。

设计中DSP部分程序采用C语言和汇编混合编程实现;对于FPGA内的各功能模块和时序用Verilog HDL编程[12]语言实现。ADV212初始化程序主要完成:1)配置和校验ADV212内部直接和间接寄存器;2)加载ADV212的编码固件程序;3)配置固件配置寄存器,设置工作状态;4)检验应用程序的ID;5)清除中断,使ADV212开始运行。ADV212的后缀名为.sea的固件程序,可在ADI公司网站下载。

系统在上电后,首先完成FPGA,DSP的初始化,包括清除所有CPU中断、使能外部中断以及使能全局中断等。DSP完成初始化后将存储在Flash中ADV212的固件通过数据线读出,然后便通过FPGA接口对ADV212进行初始化。所有模块初始化完成后,系统通过PCI9054桥路读入原始数据,在逻辑控制功能模块控制下,原始数据经降斑处理、压缩处理,最后完成压缩码流数据的读取及通过高速422串口向信道传输。系统软件总流程如图7所示。

6 系统测试结果及分析

图7 系统软件总体框图

系统各模块经设计、综合和布局布线,测试系统最终以PMC板形式实现。首先,系统采用分辨力为4096×4096的原始SAR图像,输入速率35 Mbyte/s,进行了压缩测试,在压缩比为8∶1时,系统以恒定速率(2.5 Mbyte/s)实时输出串行格式码流,生成了.jp2格式的图像文件,验证了系统的可用性和正确性。其次,为了测试系统降斑效果,在测试时,又对图像预处理功能进行了旁路,得到了没有经降斑处理的.jp2格式的图像文件。最后用JPEG200软件[13]对其进行解码得到重建图像,如图8所示。对其等效视数(ENL)、边缘保持指数(EPI)进行了比较,如表1所示。主观图像和客观数据表明,经过降斑处理的图像相干斑噪声明显减弱。

图8 重建图像降斑效果对比

表1 重建图像(8∶1)降斑效果对比

对于ADV212的HDATA总线,在150 MHz主频下,最大输入吞吐率为65 Msample/s(兆采样值/秒)。对于系统需压缩的静态图像,以最大的分辨力4096×16384(10.7 Msample/s)为例进行了测试,系统的最大需求小于ADV212的最大处理能力。因此,完全满足系统实时压缩的需求。

7 小结

SAR图像压缩系统对压缩比、失真度、实时性等都提出了较高的要求。本文设计并实现了一种基于降斑处理的压缩系统。该系统具有很高的灵活性和扩展性,系统留有一定的资源冗余和控制端口,且器件全部选用工业档,允许日后对其进行优化。

[1]WALLACE G K.The JPEG still picture compression standard[J].IEEE Trans.Consumer Electronics,1992,38(1):18-34.

[2]余楚才.SAR图像数据压缩技术研究[D].成都:电子科技大学,2009.

[3]LEE J S.Speckle suppression and analysis for synthetic aperture radar images[J].Optical Engineering,1986,25(5):636-643.

[4]李涛,许悦雷,田松,等.基于FPGA的室内智能吸尘平台设计与实现[J].电子技术应用,2012(3):47-49.

[5]邓宸伟,赵保军.基于ADV212的实时图像压缩系统[J].电视技术,2008,32(12):35-37.

[6]王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-35.

[7]蔺志强,孟令军,彭晴晴.基于ADV7180的视频图像实时采集系统的设计[J].电视技术,2011,35(17):36-39.

[8]杨毓军,王永禄,周述涛.一种超高速并串转换电路的新实现方式[J].微电子学,2006,32(2):145-147.

[9]ARSENAULT H H,APRIL G.Properties of speckle integrated with a finite aperture and logarithmically transformed[J].Journal of the Optical Society of America,1976,66(11):1160-1163.

[10]韦海萍.基于FPGA的增强Lee滤波算法设计与实现[J].航天控制,2011,29(3):33-36.

[11]JPEG2000 Video Codec ADV212[EB/OL].[2012-01-02].http://www.analog.com/zh/audiovideo-products/video-compression /ADV212/products/product.html,2008.4.

[12]PALNITKAR S.Verilog HDL:a guide to digital design and synthesis[M].2版.北京:电子工业出版社,2004.

[13]ADAMS M.D.Adams.JasPer project homepage[EB/OL].[2012-01-02].http://www.ece.uvic/ca/mdadams/jasper.