GJB289A与ARINC429双总线通讯接口卡设计✴

庞 帅,范惠林,竹武林

(空军航空大学航空军械工程系,吉林长春 130022)

0 引 言

随着PXI总线在一些测试系统中的应用,需要一种能够完成GJB289A和ARINC429总线通讯的PXI接口卡.在对发射装置测试的过程中,仅需要模拟GJB289A和ARINC429总线信号的发送与接收即可,不需要完成复杂的GJB289A和ARINC429总线通信协议,即依靠硬件电路产生相对等效的总线信号,便可完成对发射装置武器总线信号的测试[1].因此,本文提出利用FPGA实现模拟GJB289A和ARINC429总线信号接收发送的PXI接口卡,可将采集到的总线信号通过PXI总线送到主控机中分析和显示.

1 GJB289A和ARINC429总线

GJB289A武器总线和ARINC429武器总线标准差异较大.GJB289A总线字由20 b构成,电气特性规定为双向、变压器耦合、双绞屏蔽线传输,传输速率为1 Mb/s;ARINC429总线字由32 b构成,电气特性规定由单向、差分耦合、双绞屏蔽线传输,每条线上的信号电压范围为 -5 V~+5 V之间,高速工作状态的位速率为100 Kb/s,低速工作状态的位速率在12.0 Kb/s~14.5 Kb/s范围内.

1.1 GJB289A总线

GJB289A总线用的是双相曼彻斯特II型码(Manchester II).这种码在每个码位中点处存在一个跳变,信号“1”是由1到0的负跳,而“0”信号是由0到1的正跳.所谓双相,是双极性,本身包含定时的信息,它能与变压器耦合协调,形式如图1所示.

1.2 ARINC429总线

图1 曼彻斯特 Ⅱ型码格式Fig.1 The format of ManchesterⅡ

图2 ARINC429总线格式Fig.2 The format of ARINC429 bus

ARINC429总线信号的基本信息单元是一个32 b的数据字,有BNR数据、BCD数据、离散数据、维护数据和AIM数据5个应用组.ARINC429总线规定了使用该总线的航空电子设备的信息流向和基本数据字的格式.它采用单向传输、双极性归零制的三态码调制方式,即调制信号由“高”、“零”和“低”状态组成的三电平状态调制[2].例如,二进制“1011001”总线传输格式如图2所示.ARINC429总线接收端接收的是差动电压,A为A端相对地的电压,B为B端相对地的电压,A-B为A端相对于B端的电压.

2 设计方案

接口卡接收由主控机经PXI总线传输过来的GJB289A格式的消息,通过GJB289A发送模块将每16 b字转换为串行数据并由标准接口按照曼彻斯特码发送到发射装置;ARINC-429接收模块接收由发射装置转换后的满足ARINC-429总线格式的10 V差动电压信号,转化为5 V内部TTL逻辑电平,采样后,把串行数据转换为并行数据,经PXI总线接口,送入主控机同先前传输的GJB289A格式的消息进行对比,即可完成对发射装置总线通讯模块的测试.

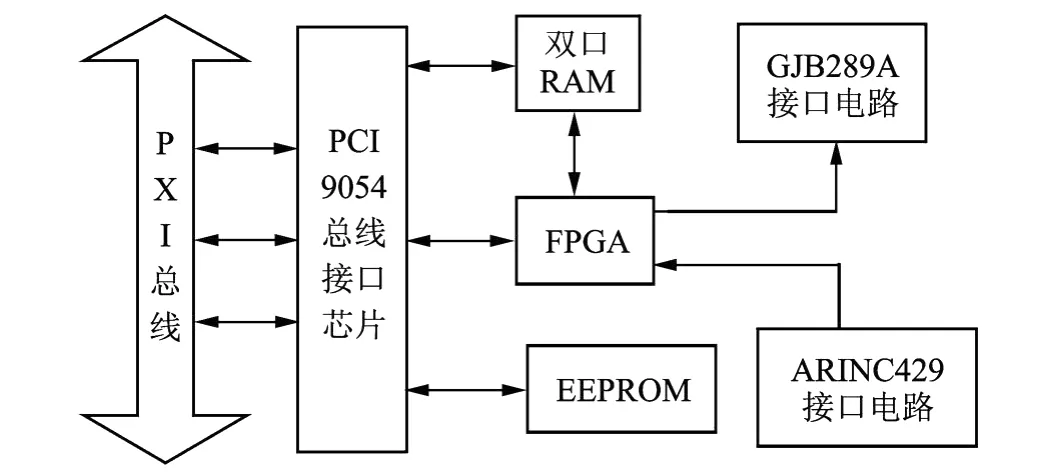

图3 接口卡硬件设计原理图Fig.3 Design of interface board

测试卡主要由 FPGA主模块、ARINC429总线接口电路、GJB289A总线接口电路及PXI接口电路组成.FPGA主模块完成总线数据的读写与通讯,429总线接口电路和GJB289A总线接口电路完成ARINC-429总线和GJB289A总线电平转换和总线标准,PXI接口电路完成测试模块与主控机之间的通信,双口RAM完成总线数据通讯时的数据缓冲.接口卡硬件设计原理如图 3所示.主要由PXI接口器件PCI9054、FPGA(Altera Cyclone系列的EPIC12Q240C8)、PCI接口配置芯片E2PROM(93CS56L),双口RAM(IDT70V28L)和电平转换器件HI1567/HI-8588组成.

3 硬件设计与实现

3.1 PXI接口电路

因为PXI总线与PCI总线兼容,可通过PCI9054完成PXI总线通讯.主控机经过“Host-PCI”桥与PCI总线连接,这个桥提供了一个低延迟的访问通路,使主控机能够访问PCI设备,PCI主设备也能访问内存.该桥还提供了数据缓冲功能,使微处理器与PCI总线上的设备并行工作而不必等待[3].

PCI9054是PXI总线的目标,因此,选择直接从模式作为PCI9054的数据传输模式.本地总线工作方式有M、C、J 3种,鉴于C模式的本地总线操作时序最为简单、逻辑控制相对容易、开发难度相对较低、且能够完全满足设计的需要,所以工作方式选择C模式,此时,将PCI9054的模式选择引脚mode0、model接地.PXI接口电路的设计主要包括3部分:PCI端(PCI Bus)、本地总线端(Local Bus)和E2 PROM端.如图4所示.

图4 PXI接口设计图Fig.4 Design of PXI interface

PCI9054的PCI总线接口主要完成数据传输地址和控制指令的译码,只要将芯片的PCI端信号线与PXI总线的相应信号线相互连接即可,要严格按照PXI总线的规范连接.

本地总线接口用来实现本地总线的数据传输以及标识本地端工作状态.本地总线接口端连接FPGA,FPGA负责整个系统的逻辑控制以及PCI主控设备的读写信号与局部总线设备的读写信号电平逻辑匹配.

鉴于输出GJB289A总线与输入ARINC429总线的传输速率相差较大,设计中使用了双端口RAM IDT 70V 28L作为FPGA和PCI9054之间的共享存储器,DT70V 28L是IDT公司的高速64 K*16b双端口静态RAM,最大存取时间为15 ns.它具有两组数据总线、地址总线和控制总线,两组总线可以同时访问不同的存储单元,这样,既能提高通信的实时效率,又能使通信具有很好的抗干扰性.使用双口RAM时,输入输出两端同时访问同一存储单元,就会发生冲突,造成写错误或者读错误,即争用问题,使用时,根据设计需要,将双端口RAM分成了读、写两块.其中,前32KB用来存储待发送的GJB289A总线数据,后32KB用来存储接收的ARINC429总线数据.

通过PCI总线访问存储器,所有目标设备都要检查AD[1:0],或者提供所要求的突发传输周期,或者执行一次目标设备断开操作.对于所有支持突发传输的设备都应该能够实现线性突发传输周期,但不一定要求支持Cache行操作.在存储器地址空间,要用AD[31:02]译码得到一个双字边界对齐的起始地址,在地址递增方式下,每个数据周期过后地址加4(双字节为4 B),直到传输过程结束.

以发送通道为例,其地址范围0x00000-0x07FFF,在发送通道内,又分为64个小部分,地址空间0x00000-0x001FF,0x00200-0x003FF,……,0x07E00-0x07FFF.当0x00000-0x001FF写满时,PCI9054将产生 TXFULL信号,由 FPGA读取其中数据,同时,发送数据可以存入下个地址空间0x00200-0x003FF,从而达到数据的无间隙传输.接收通道的工作过程类似.

根据以上设计分析,将PCI9054地址线的第0~15位与IDT70V28L连接,其中,第11位~15位用于对具体某一通道所划分的发送或接收空间块进行选择,第0~10位用于块内空间的定位.PCI9054数据位的第0~15位与IDT70V28L的I/O端口连接,用来传输总线通讯数据,高16位直接与FPGA连接,不用来传输具体数据.根据需要,PCI9054在使用时,用一个串行配置寄存器E2PROM 93CS56L在开机时对其初始化,以使接口电路具有特定的功能.配置寄存器标识地址映射关系以及PXI端和本地端工作.这部分的连接信号有EESK、EECS、EEDI/O等,连接时,应将EEDI/O接3.9k电阻上拉.

3.2 FPGA主模块

FPGA主要对双口RAM和协议芯片的各个控制信号进行I/O控制.FPGA的硬件程序采用状态机的方式,通过对地址信号译码,转移至对应的状态,同时有效相关的控制信号,使各个芯片处于有效的状态.FPGA程序内部的计时器保证了各个芯片控制信号的时序条件,使数据能够被可靠处理.

FPGA的I/O资源丰富,而且通过编程可以灵活配置输入与输出[4].FPGA的程序为并发执行的,利于实现较为复杂的状态机和时序控制.FPGA依靠IP核完成通道控制逻辑,GJAB289A总线标准和ARINC429总线标准数据通信.它从双口RAM中取出主控机给出的数字信号,并按照GJAB289A总线标准输出;接收经过转换成数字信号的ARINC429总线标准数据,并将其通过双口RAM送入PCI9054后经PXI总线送入主控机.

由上述分析可知,FPGA要完成以下工作:①实现双通道数据传输;②提供访问双端口RAM的控制信号,地址信号和数据新号;③提供与PCI9054连接的接口及同PCI9054通讯的控制信号等;④向PCI9054提供数据满信号(RAMRX1FUILL)和字计数器(COUNT[7……0];⑤接收PCI9054传来的数据满信号(TXFULL)、字计数器(PE[7……0])和RAM地址块选择信号(PA[15:11]);⑥实现GJB289A格式数据的发送和ARINC429格式数据的接收[5].

图6 GJB289A发送模块结构框图Fig.6 The framework of GJB289A bus

1)ARINC429接收模块

接收模块的主要作用是通过串/并转换将串行数据转换为32 b并行数据,并对收到的数据自动实行差错控制[6-8].对于字间隔、位间隔出错等错误能进行自动检测,如果没有错误,则将数据分两次送至DSP的16 b数据总线上,以供读取,ARINC429接收模块结构框图如图5所示.

2)GJB289A发送模块

GJB289A发送模块将处理器发出的并行二进制数据数据进行曼彻斯特码编码,在加上同步头及奇偶位等,组成符合GJB289A标准的总线信息帧后发送至总线[9].选用16 MHz时钟为其工作时钟.发送器主要由控制状态机、FIFO缓存、命令字同步头产生器、数据字同步头产生器、移位寄存器、奇偶校验器、曼彻斯特编码器组成,见图6.

3.3 ARINC429标准接口和GJB289A标准接口

根据ARINC429总线电平定义,接口器件选用HOLT公司的HI-8588为ARINC429总线接口芯片.接收通道选用HI-8588可将两路双极归零制电平信号转换成两路TTL信号.

GJB289A接口器件由电平转换器和耦合变压器组成,采用HOLT公司的HI-1567将互补的COMS/TTL电平转为适合GJB289A总线传输的双极性差分曼彻斯特码,由于HI-1567的工作电压是5V,在与IO电压非5V的FPGA互联时需要串接330 Ω的电阻.接口卡通过短截线与GJB289A主总线相连.在短截线和收发器间需要设置隔离变压器以提供总线驱动电压,防止终端因短路引起损坏和接口卡产生的噪声影响GJB289A主总线上的信号.本文变压器采用HOLT公司的PMDB2725EX,该变压器提供两种变压比,即1∶2.5和l∶1.79,分别适应直接耦合和变压器耦合两种方式.需要注意的是无论采用哪种方式,都必须在GJB289A总线和变压器之问串联隔离电阻对总线进行短路保护.

4 软件设计与实现

FPGA的软件开发采用VHDL语言编写[10].软件主要由Nios II处理器、ARINC429总线处理模块、GJB289A总线处理模块组成.

NiosII处理器是Altera公司开发的基于SOPC技术的32 b RISC处理器内核,采用改进的哈佛结构.处理器带有分离的数据和程序存储器控制,具备高速缓存、中断处理功能.ARINC429总线接收模块、GJB289A总线发送模块组成负责GJB289A总线的发送和ARINC429总线的接收,可通过VHDL语言来开发.由于篇幅有限,以下仅介绍GJB289A总线发送的部分软件设计方法.

GJB289A发送模块中状态机是其核心,它由4个状态组成:S0:空闲状态,根据状态转换标志信号可以转到状态S1或S2;S1:命令字同步头产生状态,它可以转换到S3;S2:数据字同步头产生状态,它可以转换到S3;S3:移位寄存状态,它可以转换到S0.

编码器需要完成生成奇校验码、曼彻斯特编码、添加同步头、串行发送等功能.通常用FPGA实现编码器的设计方法是:在编码器内部设置数据字计数器,由编码器直接读取内存区待发送数据,编码器每次完成一条消息的编码,这种方法存在命令字解析无法复用和内存操作部分重复设计的问题.

本文设计了通用性较好的曼彻斯特编码器,把发送数据字计数和对内存的寻址与读写功能放在位流控制模块中,通过状态机的转移来实现,编码器每次只完成个码字的编码任务.这样就使编码器可用于BC发送消息或RT回送消息.

编码器时钟频率为2MHz,由时钟管理模块对FPGA时钟分频得到,位流处理模块输入信息字类型tx_csw =1或tx_ dw =1,和16 b信息数据tx_dword .编码器先计算奇校验码parity=^(tx_dword),合成新系列后序列生成反相字,完成曼彻斯特编码;再根据信息字类型为序列添加同步头,txcsw=1时为111000,tx_ dw =1时为000111;最后有编码计数器en_ ent控制,在2 MHz时钟下按位串行发送到总线上,保证了总线传输速率是1 Mb/s.

曼彻斯特码生成本文采取的方法是将移位寄存器移出的串行数据与 1 M 的时钟相异或,程序代码如下:

5 结束语

本文设计的接口卡,基于FPGA可编程逻辑,利用VHDL语言实现GJB289A总线和ARINC429总线信号的处理;用IP核完成与PCI9054的本地总线连接,可接入PXI总线;使用双端口RAM完成了两种总线发送与接收的数据缓冲.解决了目前一些装置总线检测需求,具有配置灵活、易于扩展等特点.

[1]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2005:201-225,317-352.

[2]支超有.机载数据总线技术及其应用[M].北京:国防工业出版社,2009:152-315.

[3]孔德仁,何云峰,狄长安.仪表总线技术及应用[M].北京:国防工业出版社,2005:61-108,250-275.

[4]杨晓慧,杨旭.FPGA系统设计与实践[M].北京:人民邮电出版社,2010:92-105,168-200.

[5]刘锐,赵加凤,付平.基于FPGA的PXI-1553B模块设计[J].电子测量技术,2009,32(11):99-101.

Liu Rui,Zhao Jiafeng,Fu Pin.Design of PXI-1553B module based on FPGA[J].Electronic Measurement Technology,2009,32(11):99-101.(in Chinese)

[6]张超,许化龙.导弹控制系统数据采集系统设计[J].计算机测量与控制,2009,17(10):2015-2017.

Zhang Chao,Xu Hualong.Design of data acquisition system based on PC/104Bus for missile control system[J].Computer Measurement&Control,2009,17(10):2015-2017.(in Chinese)

[7]刘书智,李琳娜.Visual C++实践与提高[M].北京:中国铁道出版社,2009:41-53,131-140.

[8]张海林,杨勇.自动化系统中的串行通信协议的设计[J].计算机工程与应用,2003,31:159-160,218.

Zhang Hailin,Yang Yong.The design of serial communication protocol in automatic control system[J].Computer Engineering and Applications,2003,31:159-160,218.(in Chinese)

[9]刘锐,赵加凤,付平.基于FPGA的PXI-1553B模块设计[J].电子测量技术,2009,32(11):99-101.

Liu Rui,Zhao Jiafeng,Fu Pin.Design of PXI-1553B module based on FPGA[J].Electronic Measurement Technology,2009,32(11):99-101.(in Chinese)

[10]张洪润,张亚凡.FPGA/CPLD应用设计200例[M].北京:北京航空航天大学出版社,2009:61-108.