基于FPGA的FSK调制与接收系统设计

四川职业技术学院 谢大川 李海兵

1.选题背景

移频键控(FSK)是数字信息传输中使用较早的一种调制形式,它由于其抗干扰及衰落性较好且技术容易实现,因而在集散式工业控制系统中被广泛采用。以往的键控移频调制解调器采用“固定功能集成电路+连线”方式设计;集成块多,连线复杂,容易出错,且体积较大,本设计采用Lattice公司的FPGA芯片,有效地缩小了系统的体积,降低了成本,增加了可靠性,同时系统采用VHDL-87语言进行设计,具有良好的可移植性及产品升级的系统性。

2.二进制移频键控(2FSK)的基本原理

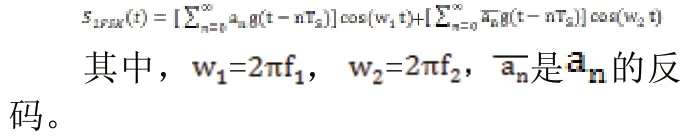

在二进制频移键控中载波频率随着调制信号1或者0而变,1对应于载波频率f1(或者w1),0对应于载波频率f2(或者w2),二进制频移键控已调信号的时域表达式为:

2FSK信号波形可以看作两个2ASK信号波形的合成。图1是相位续的2FSK信号波形。

3.在FPGA中的FSK实现

3.1 调制过程的实现

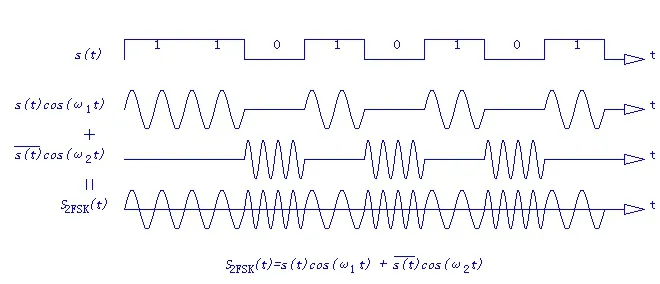

首先我们设置了一个输入电平判断器,能够通过不同的输入电平值启动不同的输出端口,调制流程图见图2。

然后根据FSK的特点我们分别设置两个计数器:计数器1和计数器2,其中计数器2的进位频率为计数器1的进位频率的2倍,通过计数器的进位端控制正弦信号发生器的输出频率,这样我们可以通过对两个计数器的切换实现对输出正弦信号频率的控制.

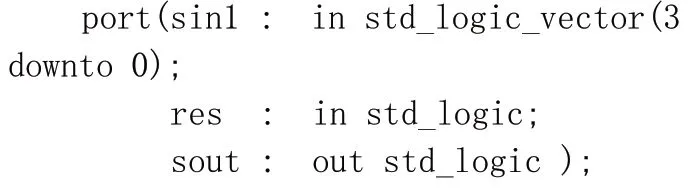

首先设计输入电平判断器:输入电平判决器共有一个输入和两个输出端口,根据输入端口电平高低的不同对两个不同的输出口置高电平,其中当某一端口为高电平时另一端口必为低电平,可以设计程序如下:

其中din为输入电平端口用于和输入信号相连,dout1和dout2是输出电平端口,用于和下一级电路元件级连作为控制。

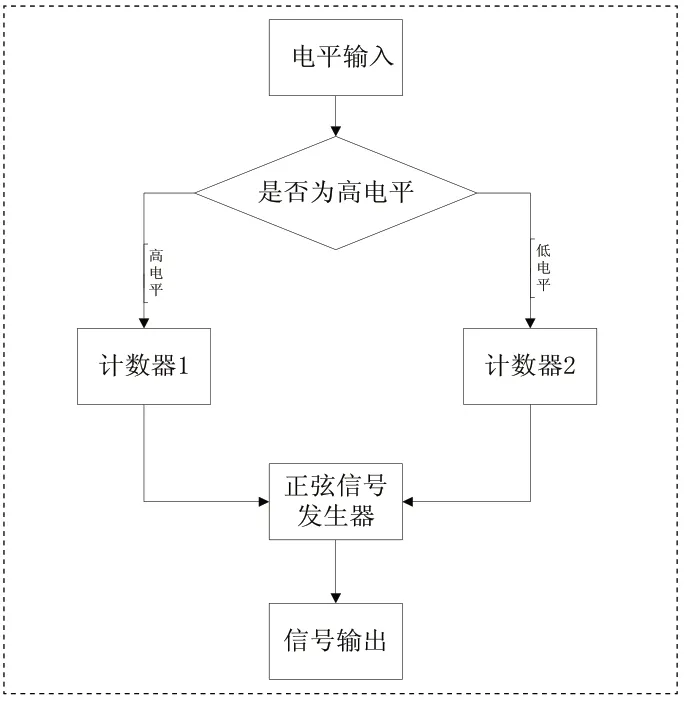

其次我们再设计用于调控输出频率的两个计数器。根据2FSK的特点输出的正弦波应该有两个不同的频率,因此我们需要两个计数器并且两个输出频率不能相同。采用quartuesII带有的宏功能模块分别设计两个计数器其中一个为8位一个为7位。在相同的记数时钟的激励下他们的最高位的跳变频率不相同,这样就实现了频分的目的。具体实现如图2。

其中P1为计数器1,采用同步清零方式,它的计数周期为:时钟频率/2的8次方,在此我们采用输出端的最高位即第7位与下级电路相连作为下级电路的输入频率。并且该频率作为“1”码的输出频率.

P2为计数器2,采用同步清零方式,它的计数周期为:时钟频率/2的7次方。在此我们采用输出端的最高位即第6位与下级电路相连作为下级的的输入频率,并且该频率作为“0”码的输出频率。

我们将判决器的“1”电平输出口与计数器P1计数使能端相连,取反和计数器本身的进位信号“相与”后接入计数器的同步清零端,当输入电平为“1”码时计数器P1开始工作;当输入电平为“0”码时计数器P1不工作并且通过相关的连接方式将计数器P1的输出相位置零保证每次“1”码重新到来是的相位能从固定值开始。

我们将判决器的“0”电平输出口与计数器P2计数使能端相连,取反和计数器本身的进位信号“相与”后接入计数器的同步清零端,当输入电平为“0”码时计数器P2开始工作;当输入电平为“1”码时计数器P2不工作并且通过相关的连接方式将计数器P2的输出相位置零保证每次“0”码重新到来是的相位能从固定值开始。

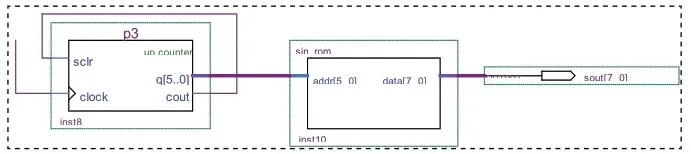

最后设计正弦信号的发生器分两步骤:首先设计一个地址发生器。采用计数器实现我们设计了一个采用同步清零6位的计数器利用计数器的6位输出端作为地址控制正弦信号的ROM,图4为调制部分信号输出实现图。

采用VHDL语言方式实现ROM文件程序思路如下:

with addr(地址信号名)select

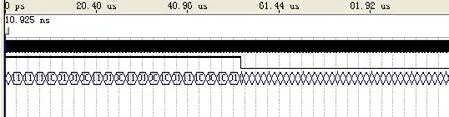

data(输出数据端口名)<=“11111111”(输出数据)when“000000”(地址信号),通过编译仿真得到仿真波形图如图5。

从仿真图形上可以看到“1”码信号在调制后产生的正弦波信号频率是“0”码信号在调制后产生的正弦波信号频率的1/2。符合调制要求。

3.2 解调过程的实现:

解调过程主要是通过过零点检测实现:其基本原理是根据频移键控的过零率的大小来检测已调的信号中频率的变化。

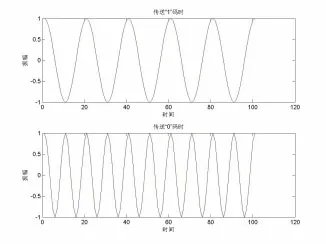

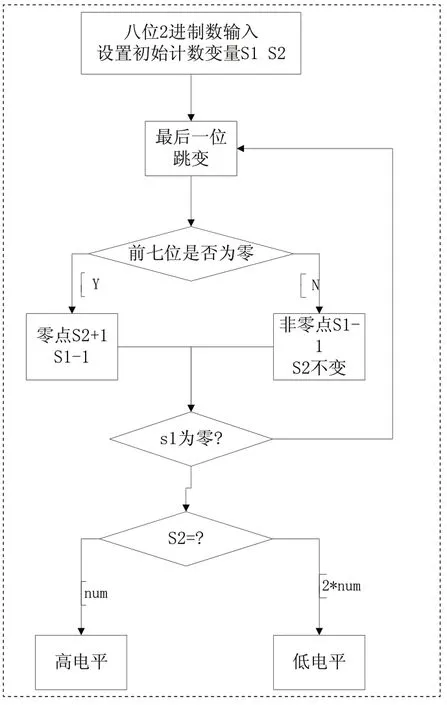

从图6中可以看出在同样的时间内,传“0”码中出现“0”的个数为传“1”码的两倍,由此我们可以通过在相同的时间段内判断码形为“0”的次数判断其为“0”码还是“1”码,图7为解调流程图。

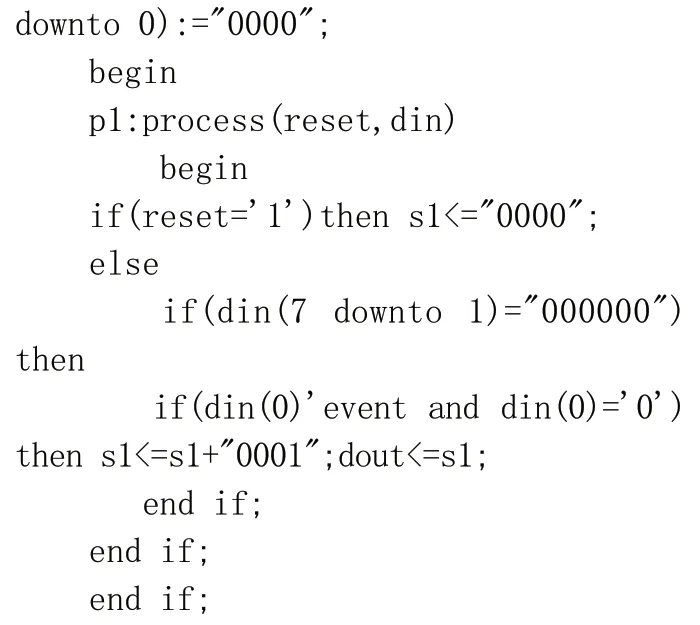

首先我们设计一个过零点计数器pq,该计数器的功能是在输入的正弦信号全为“0”时计数值自动加1,相关程序要点如下:.

图1 2FSK波形

图2 调制流程图

图3 调制部分地址产生电路实现图

图4 调制部分信号输出实现图

图5 调制模块仿真图

图6 两种传输波形的比较

图7 解调流程图

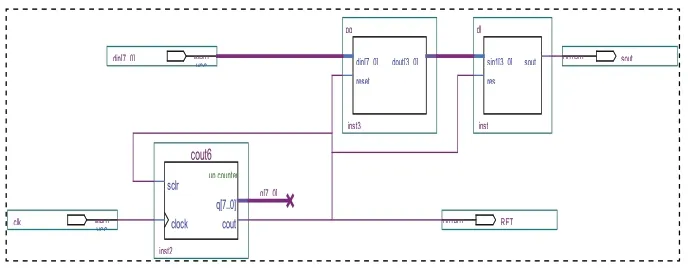

图8 解调部分实现图

图9 解调部分方针图

其中din[7..0]是8位正弦信号的输入口,reset为清零端,dout[3..0]为过零点计数值输出端。

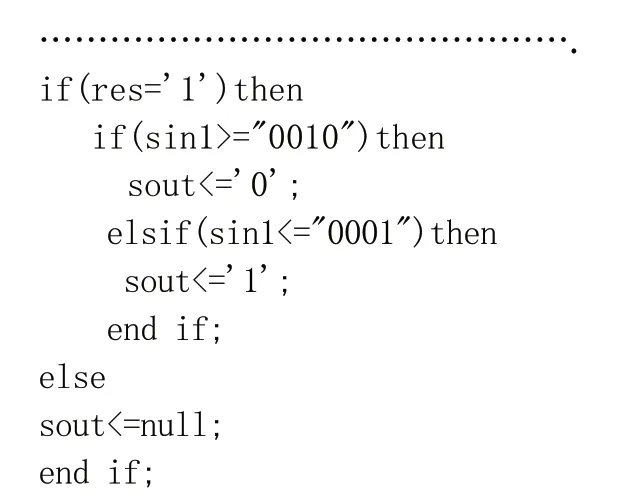

接下来我们设计一个数值判决器,用于判决过零点的数目根据数目的不同分别译出高低电平从而实现解调的目的。程序要点如下:

其中sin1[3..0]为过零点数目输入端,res为清零端,sout为解调信号输出端。

当res信号的“0”到“1”跳变到来时,将过零点计数器送来的过零点数目进行比较。当过零点数目大于等于2是判断为低电平,反之判断为高电平。从而实现解调。

另外为了提高准确性实现在单位时间内进行过零点数目的比较,我们还应该在设置一个计数器采用同步清零方式,利用它的进位端信号作为过零点计数器和数值判决器的reset和res信号这就保证了在固定的时间内测量过零点的数目。

具体实现电路如图8。

通过编译和仿真得到波形图9。

从波形图我们可以看出:在两次判决时间点上根据输入信号的不同,解调信号分别为“1”和“0”。从而实现了解调功能。

4.总结

根据我们以上的试验可以得出采用FSK调制方式能很好的传输信号。另外根据需要调整输入时钟,以可以获得不同频率的载波,从而克服来自外界的干扰实现各种远距离信号传输。

[1]曹志刚,钱亚生.现代通信原理[M].清华大学出版社,1992.

[2]刘笃仁,杨万海.在系统可编程技术及其器件原理与应用[M].西安电子科技大学出版社,2000.

[3]黄智伟.FPGA系统设计与实践[M].电子工业出版社,2005.

[4]黄继业,潘松.EDA技术实用教程[M].科学出版社,2002.

[5]黄正瑾.可编程逻辑击键设计[M].复旦大学出版社,1997.

[6][美]UWE MEY.数字信号处理的FPGA实现[M].